半导体存储器装置、其操作方法和动态随机存取存储器与流程

本发明涉及半导体装置,并且更具体地,涉及可减小由于全局输入和输出(io)线的负载而发生的影响的半导体存储器装置及其操作方法。

背景技术:

1、在半导体存储器装置中,对存储容量的扩大和面积的减小的需求不断增加。在此方面,电连接到全局io线中的每条的存储器单元或子阵列的数量增加。

2、随着电连接到一条全局io线的存储器单元或子阵列的数量增加,全局输入和输出线的负载也增加。因此,存在对可防止功耗或特性劣化的半导体存储器装置的控制的需求。

技术实现思路

1、本发明提供可减小由于全局输入和输出(io)线的负载而发生的影响的半导体存储器装置及其操作方法。

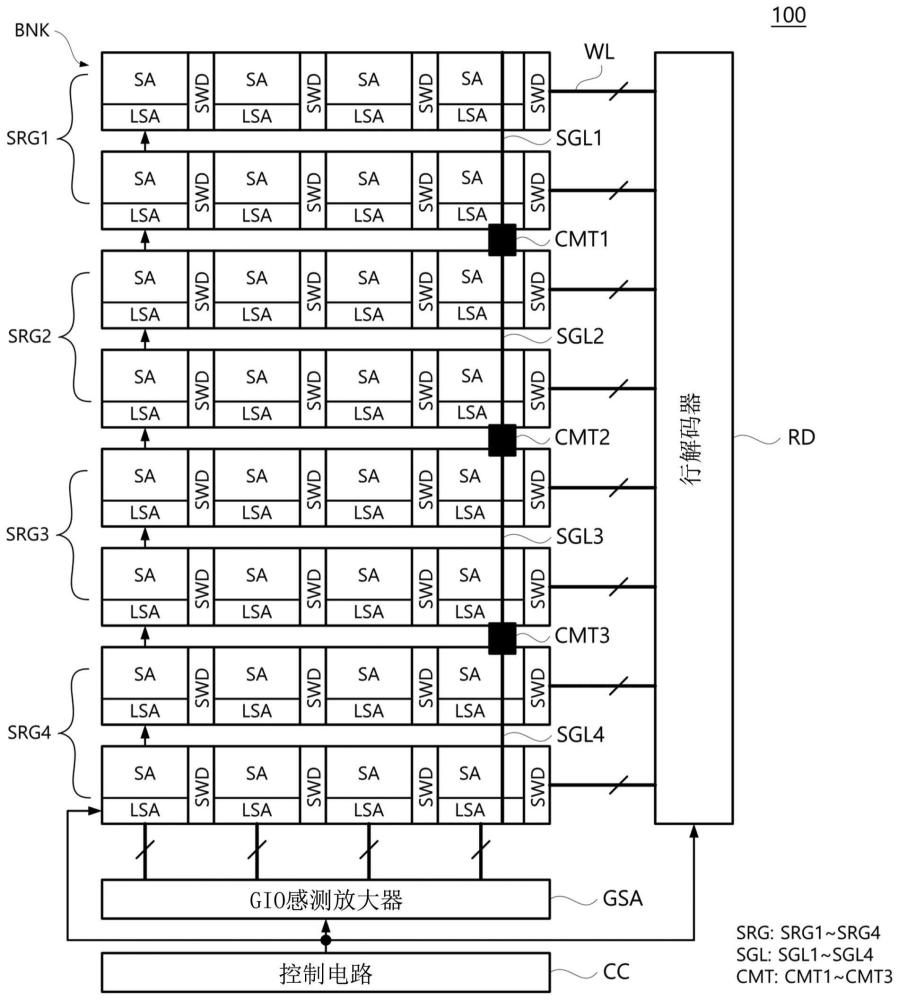

2、根据本发明的一个方面,提供了一种半导体存储器装置,包括:存储体,存储体被分割为包括多个子阵列的第一分割区域至第n分割区域;第一连接控制晶体管至第n-1连接控制晶体管,第一连接控制晶体管至第n-1连接控制晶体管由第一分割区域至第n分割区域之中的邻近分割区域共享并且响应于连接控制信号而接通;第一全局输入/输出(gio)分割线至第n gio分割线,通过第一连接控制晶体管至第n-1连接控制晶体管之中的对应连接控制晶体管彼此连接;以及gio感测放大器,gio感测放大器接收并且处理通过第一gio分割线至第n gio分割线之中的连接的gio分割线从存储器单元读取的数据。

3、存储器单元区域包括可在第一方向上堆叠在外围电路区域上并且与外围电路区域重叠的存储体,其中,第一连接控制晶体管至第n-1连接控制晶体管设置在外围电路区域中。

4、存储器单元区域可形成在第一基底上,外围电路区域可形成在第二基底上,并且第一基底可在第一方向上设置在第二基底的上部。

5、第一连接控制晶体管至第n-1连接控制晶体管可置于第一分割区域至第n分割区域之中的邻近分割区域之间。

6、第一分割区域至第n分割区域中的每个还可包括用于通过使用第一驱动电压感测和放大所述多个子阵列之中的对应子阵列的数据多个局部感测放大器,并且第一gio分割线至第n gio分割线可各自连接到所述多个局部感测放大器之中的局部感测放大器,所述局部感测放大器包括在第一分割区域至第n分割区域之中的对应分割区域中。

7、第一驱动电压可与从第一分割区域至第n分割区域之中的包括局部感测放大器的分割区域到gio感测放大器的间隔开的距离成比例。

8、当从第一分割区域到gio感测放大器的间隔开的距离大于从第n分割区域到gio感测放大器的间隔开的距离时,第一分割区域中的局部感测放大器的第一驱动电压可高于第n分割区域中的局部感测放大器的第一驱动电压。

9、所述半导体存储器装置还可包括:至少两个gio预充电晶体管,所述至少两个gio预充电晶体管中的每个连接到第一gio分割线至第n gio分割线之中的对应gio分割线的一端,并且响应于预充电信号而导通。

10、gio预充电晶体管可被包括在第一gio分割线至第n gio分割线中的每个中。

11、gio预充电晶体管的一端可连接到第一连接控制晶体管至第n-1连接控制晶体管之中的对应连接控制晶体管的一端。

12、所述半导体存储器装置还可包括:至少两个gio辅助驱动器,所述至少两个gio辅助驱动器连接到第一gio分割线至第n gio分割线之中的对应gio分割线,并且通过使用第二驱动电压来缓冲将被写入的数据。

13、第二驱动电压可与从对应于第一gio分割线至第n gio分割线之中的gio分割线的分割区域到gio感测放大器的间隔开的距离成比例,gio辅助驱动器连接到所述gio分割线。

14、gio辅助驱动器可分别连接到第一连接控制晶体管至第n-1连接控制晶体管之中的对应连接控制晶体管的一端以及第一gio分割线至第n gio分割线之中的对应gio分割线。

15、所述半导体存储器装置还可包括:至少两个gio预充电晶体管,所述至少两个gio预充电晶体管对第一gio分割线至第n gio分割线之中的对应gio分割线进行预充电;以及至少两个gio辅助驱动器,所述至少两个gio辅助驱动器缓冲将被施加到第一gio分割线至第n gio分割线之中的对应gio分割线的数据。

16、根据本发明的另一实施例,提供了一种操作半导体存储器装置的方法,包括:指定包括在存储体中的多个分割区域之中的与接收到的地址对应的分割区域;将多条gio分割线之中的对应gio分割线连接到指定的分割区域;通过连接的gio分割线来感测与所述地址对应的存储器单元的数据;以及放大感测到的数据以作为读取数据输出。

17、感测与所述地址对应的存储器单元的数据的步骤还可包括:响应于连接的gio分割线的数量,施加与所述地址对应的局部感测放大器的每个不同的第一驱动电压。

18、所述方法还可包括:对所述多条gio分割线中的每条分别进行预充电。

19、根据本发明的另一实施例,提供了一种动态随机存取存储器(dram),包括:存储器单元区域,存储器单元区域形成在第一基底上并且包括多个分割区和与所述多个分割区域对应的多条gio分割线;以及外围电路区域,外围电路区域形成在第二基底上,并且包括用于响应于接收到的地址来连接或分割所述多条gio分割线的多个连接控制晶体管,其中,第一基底在垂直方向上堆叠在第二基底上,并且与第二基底重叠。

20、驱动电压响应于所述多条gio分割线之中的连接的gio分割线的数量而被不同地施加到所述多个分割区域之中的对应分割区域,以感测或写入数据。

21、外围电路区域还可包括:至少两个gio预充电晶体管,所述至少两个gio预充电晶体管连接到所述多条gio分割线之中的对应gio分割线,并且对对应gio分割线进行预充电;以及至少两个gio辅助驱动器,所述至少两个gio辅助驱动器连接到所述多条gio分割线之中的对应gio分割线,并且缓冲将被施加到对应gio分割线的数据。

技术特征:

1.一种半导体存储器装置,包括:

2.根据权利要求1所述的半导体存储器装置,其中,存储器单元区域包括在第一方向上堆叠在外围电路区域上并且与外围电路区域重叠的存储体,其中,第一连接控制晶体管至第n-1连接控制晶体管设置在外围电路区域中。

3.根据权利要求2所述的半导体存储器装置,其中,存储器单元区域形成在第一基底上,外围电路区域形成在第二基底上,并且第一基底在第一方向上设置在第二基底的上部。

4.根据权利要求1所述的半导体存储器装置,其中,第一连接控制晶体管至第n-1连接控制晶体管置于第一分割区域至第n分割区域之中的邻近分割区域之间。

5.根据权利要求1所述的半导体存储器装置,还包括:用于通过使用第一驱动电压感测和放大所述多个子阵列之中的对应子阵列的数据多个局部感测放大器,其中,第一gio分割线至第n gio分割线各自连接到所述多个局部感测放大器之中的局部感测放大器,局部感测放大器感测和放大第一分割区域至第n分割区域之中的对应分割区域。

6.根据权利要求5所述的半导体存储器装置,其中,第一驱动电压与从第一分割区域至第n分割区域之中的分割区域到gio感测放大器的间隔开的距离成比例,在所述分割区域中,局部感测放大器执行感测和放大操作。

7.根据权利要求1所述的半导体存储器装置,其中,当从第一分割区域到gio感测放大器的间隔开的距离大于从第n分割区域到gio感测放大器的间隔开的距离时,第一分割区域中的局部感测放大器的第一驱动电压高于第n分割区域中的局部感测放大器的第一驱动电压。

8.根据权利要求1所述的半导体存储器装置,还包括:至少两个gio预充电晶体管,所述至少两个gio预充电晶体管中的每个连接到第一gio分割线至第n gio分割线之中的对应gio分割线的一端,并且响应于预充电信号而导通。

9.根据权利要求8所述的半导体存储器装置,其中,gio预充电晶体管连接到第一gio分割线至第n gio分割线中对应的gio分割线。

10.根据权利要求8所述的半导体存储器装置,其中,gio预充电晶体管的一端连接到第一连接控制晶体管至第n-1连接控制晶体管之中的对应连接控制晶体管的一端。

11.根据权利要求1所述的半导体存储器装置,还包括:至少两个gio辅助驱动器,所述至少两个gio辅助驱动器连接到第一gio分割线至第n gio分割线之中的对应gio分割线,并且通过使用第二驱动电压来缓冲将被写入的数据。

12.根据权利要求11所述的半导体存储器装置,其中,第二驱动电压与从对应于第一gio分割线至第n gio分割线之中的gio分割线的分割区域到gio感测放大器的间隔开的距离成比例,gio辅助驱动器连接到所述gio分割线。

13.根据权利要求11或12所述的半导体存储器装置,其中,gio辅助驱动器分别连接到第一连接控制晶体管至第n-1连接控制晶体管之中的对应连接控制晶体管的一端以及第一gio分割线至第n gio分割线之中的对应gio分割线。

14.根据权利要求1至7中的任一项所述的半导体存储器装置,还包括:

15.一种操作半导体存储器装置的方法,包括:

16.根据权利要求15所述的方法,其中,感测与所述地址对应的存储器单元的数据的步骤还包括:响应于连接的gio分割线的数量,施加与所述地址对应的局部感测放大器的每个不同的第一驱动电压。

17.根据权利要求15所述的方法,还包括:对所述多条gio分割线中的每条分别进行预充电。

18.一种动态随机存取存储器dram,包括:

19.根据权利要求18所述的dram,其中,驱动电压响应于所述多条gio分割线之中的连接的gio分割线的数量而被不同地施加到所述多个分割区域之中的对应分割区域,以感测或写入数据。

20.根据权利要求18所述的dram,其中,外围电路区域还包括:

技术总结

半导体存储器装置、其操作方法和动态随机存取存储器被提供。根据本发明的实施例的所述半导体存储器装置包括:存储体,存储体被分割为包括多个子阵列的第一分割区域至第n分割区域;第一连接控制晶体管至第n‑1连接控制晶体管,第一连接控制晶体管至第n‑1连接控制晶体管由第一分割区域至第n分割区域之中的邻近分割区域共享并且响应于连接控制信号而接通;第一全局输入/输出(GIO)分割线至第n GIO分割线,通过第一连接控制晶体管至第n‑1连接控制晶体管之中的对应连接控制晶体管彼此连接;以及GIO感测放大器,GIO感测放大器接收并且处理通过第一GIO分割线至第n GIO分割线之中的连接的GIO分割线从存储器单元读取的数据。

技术研发人员:李承俊,金尚玧,金钟赫,元福渊

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!