用于片上存储器的动态的、基于通路的可变流水线架构的制作方法

背景技术:

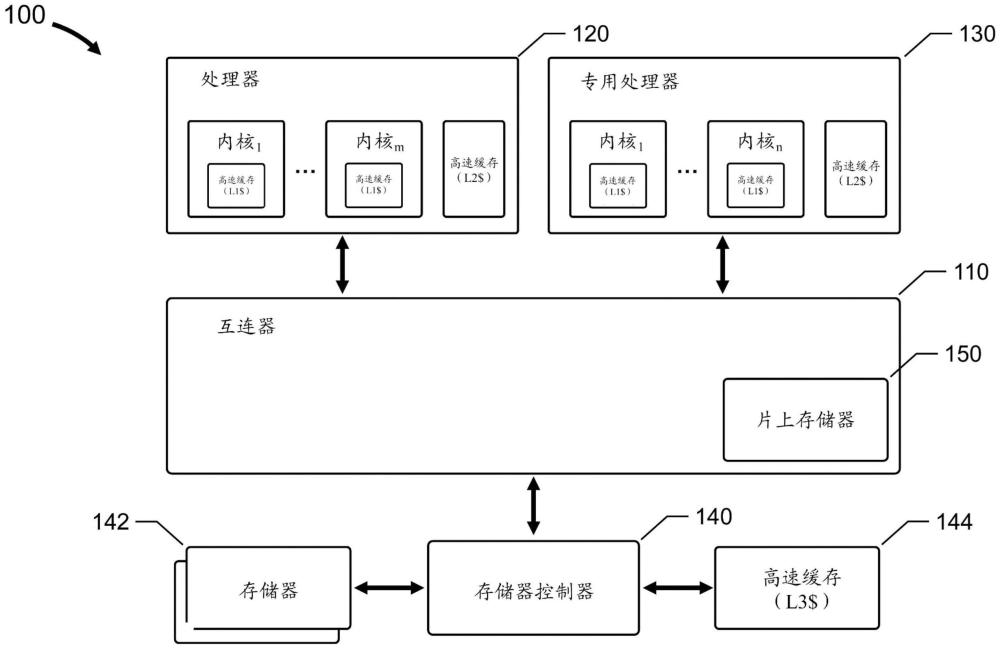

1、本公开涉及计算机系统。更具体地,本公开涉及存储器。

2、典型的存储器架构包含固定流水线,其中输入存储器地址、访问存储器单元并且读出数据。一些存储器架构尝试通过预测待读取的下一个存储器地址来提高存储器访问速度。遗憾的是,这些预测技术依赖于当前存储器地址并且通常需要多个数据总线或输出缓冲器,一个用于从当前存储器地址读取的数据,一个用于从下一个存储器地址读取的数据。

技术实现思路

技术特征:

1.一种用于管理存储器中的功率的方法,所述方法包括:

2.根据权利要求1所述的方法,所述方法还包括在所述访问所述地址之前,向输入/输出(i/o)电路施加功率。

3.根据权利要求2所述的方法,所述方法还包括在所述对所述地址进行解码之前,向控制电路施加功率。

4.根据权利要求3所述的方法,其中在所述接收所述访问请求之前,不向所述字线控制电路、所述i/o电路和所述控制电路施加功率。

5.根据权利要求4所述的方法,所述方法还包括:

6.根据权利要求3所述的方法,所述方法还包括:

7.根据权利要求6所述的方法,所述方法还包括:

8.根据权利要求7所述的方法,所述方法还包括:

9.根据权利要求2所述的方法,其中所述多个字线区段包括至少四个字线区段,并且每个字线区段包括相同数量的字线。

10.根据权利要求9所述的方法,其中:

11.一种存储器,所述存储器包括:

12.根据权利要求11所述的存储器,其中所述控制电路被进一步配置为在所述访问所述地址之前,向所述i/o电路施加功率。

13.根据权利要求12所述的存储器,其中在所述对所述地址进行解码之前,向所述控制电路施加功率。

14.根据权利要求13所述的存储器,其中在所述接收所述访问请求之前,不向所述字线控制电路、所述i/o电路和所述控制电路施加功率。

15.根据权利要求14所述的存储器,其中所述控制电路被进一步配置为:

16.根据权利要求13所述的存储器,其中所述控制电路被进一步配置为:

17.根据权利要求16所述的存储器,其中所述控制电路被进一步配置为:

18.根据权利要求17所述的存储器,其中所述控制电路被进一步配置为:

19.根据权利要求11所述的存储器,其中:

20.一种系统高速缓存,所述系统高速缓存包括多个存储器,每个存储器根据权利要求11所述。

技术总结

本公开提供了一种片上存储器。该存储器包括字线区段、输入/输出(I/O)电路和控制电路。每个字线区段包括多个字线,并且每个字线区段耦接到不同字线控制电路。该控制电路被配置为响应于接收到包括地址的访问请求,对该地址进行解码,包括基于该地址来确定相关联的字线,以及基于该相关联的字线来确定相关联的字线区段。该控制电路被进一步配置为向耦接到该相关联的字线区段的字线控制电路施加功率,以及访问该地址。

技术研发人员:爱德华·马丁·小麦库姆斯

受保护的技术使用者:Arm有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!