磁存储器检测电路、方法及电子设备与流程

本发明涉及半导体器件测试,特别是涉及一种磁存储器检测电路、方法及电子设备。

背景技术:

1、磁性存储器件的设计与制造中,需考虑磁性存储器件的测试电路,以便于在磁性存储器件生产完成后进行坏点检测,以在挑选出符合标准的磁性存储芯片的同时对集成电路加工工艺进行提升。传统的测试电路集成在磁性存储芯片中,占用了额外的面积。同时,内建的测试电路本身的pvt(process、voltage、temperature,工艺、电压、温度)偏移会对磁性存储器件的测量造成干扰。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种无需在磁性存储芯片内集成测试电路即可完成磁性存储器件测试的磁存储器检测电路、方法及电子设备。本发明提供了一种磁存储器检测电路,所述检测电路包括:

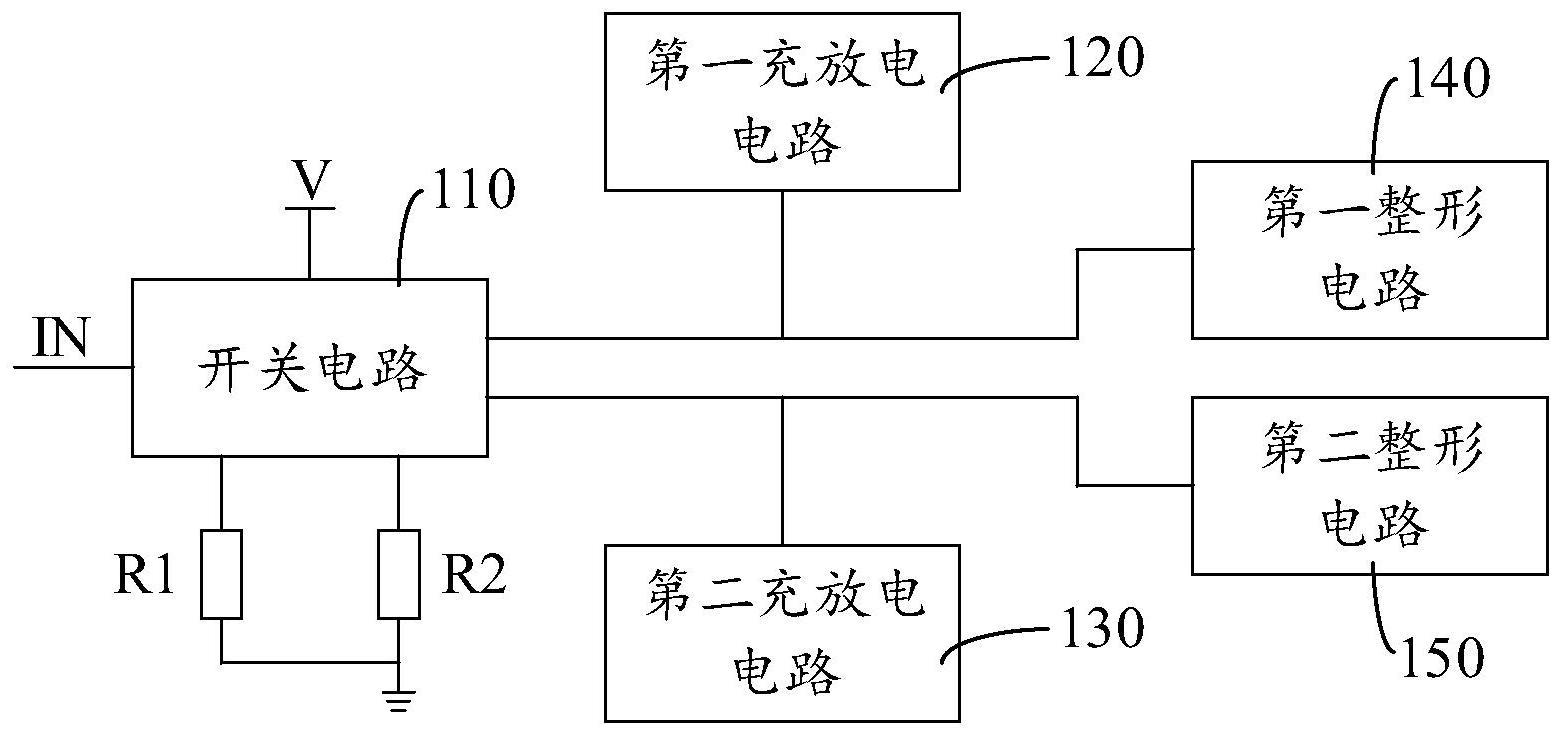

2、开关电路、第一充放电元件、第二充放电元件、第一整形电路与第二整形电路,所述开关电路具有第一检测端与第二检测端,分别用于连接第一磁存储器件与第二磁存储器件,第一磁存储器件与第二磁存储器件的磁化状态相反,且为磁性存储阵列中的一个互补单元;

3、所述开关电路用于所述第一充放电元件与第二充放电元件充电,或者分别通过第一磁存储器件与第二磁存储器件放电;

4、所述第一整形电路与第二整形电路分别用于将第一充放电元件的端电压与第二充放电元件的端电压整形为迅速变化的第一电压信号时域波形与第二电压信号时域波形,所述第一电压信号时域波形与第二电压信号时域波形用于在同一时域坐标中组合成组合时域波形后同预设时域波形进行比较,以得出所述互补单元的检测结果。

5、在其中一个实施例中,所述第一整形电路与第二整形电路分别为第一整形反相器与第二整形反相器,分别用于将第一充放电元件与第二充放电元件的端电压转换为反相的方波信号,所述第一充放电元件与第二充放电元件为负载电容。。

6、在其中一个实施例中,所述开关电路包括第一开关管、第二开关管、第三开关管与第四开关管,所述第一开关管与第三开关管的第一端用于连接第一电压,第二端分别连接所述第二开关管与第四开关管的第一端,以及分别连接第一充放电元件与第二充放电元件,所述第二开关管与第四开关管的第二端分别用于连接第一磁存储器件与第二磁存储器件。

7、在其中一个实施例中,所述检测电路还包括第一d触发器与第二d触发器,所述第一d触发器的数据输入端连接第一整形电路的输出端,时钟信号输入端连接第二整形电路的输出端,所述第二d触发器的数据输入端连接第二整形电路的输出端,时钟信号输入端连接第一整形电路的输出端。

8、本发明还提供了一种磁存储器检测方法,应用于上述所述的磁存储器检测电路,所述方法包括:

9、调整控制信号,使第一充放电元件与第二充放电元件先进行充电,随后通过互补单元放电,所述互补单元为第一磁存储器件与第二磁存储器件构成的存储单元;

10、获取充放电过程中第一电压信号时域波形与第二电压信号时域波形在同一时域坐标中的组合时域波形;

11、将所述组合时域波形同预设时域波形进行比对,得出所述互补单元的检测结果。

12、在其中一个实施例中,所述将所述组合时域波形同预设时域波形进行比对,得出所述互补单元的检测结果,包括:

13、响应于所述组合时域波形中的至少一个时域波形的时序延时超过第一阈值,输出所述互补单元疑似断路的结果;

14、响应于所述组合时域波形的至少一个时域波形的时序超前超过第二阈值,输出所述互补单元疑似短路的结果。

15、在其中一个实施例中,所述将所述组合时域波形同预设时域波形进行比对,得出所述互补单元的检测结果,包括:

16、响应于所述组合时域波形比对预设时域波形在波形和时序上完全一致,或者波形一致且时序颠倒,将所述组合时域波形保存为参考时域波形;

17、在对所述互补单元执行写入操作后,调整控制信号,以进行第一充放电元件与第二充放电元件的充电,以及对互补单元的放电;

18、获取第一电压信号时域波形与第二电压信号时域波形在同一时域坐标中的合成时域波形;

19、比对所述合成时域波形与所述参考时域波形;

20、响应于所述合成时域波形比对参考时域波形在波形和时序上完全一致,输出所述互补单元丧失写入能力的结果。

21、在其中一个实施例中,所述比对所述合成时域波形与所述参考时域波形,之后包括:

22、响应于所述合成时域波形比对参考时域波形在波形和时序均不一致,且所述合成时域波形中两个时域波形的时序均未发生颠倒,输出所述互补单元可以完成写入,但存在器件缺陷的结果;

23、响应于所述合成时域波形比对参考时域波形在波形上不一致,且所述合成时域波形中其中一个时域波形的时序发生颠倒,输出所述互补单元中其中一个磁存储器件可以写入,另一个磁存储器件丧失写入能力的结果。

24、在其中一个实施例中,所述比对所述合成时域波形与所述参考时域波形,之后包括:

25、响应于所述合成时域波形比对参考时域波形在波形上不一致,且所述合成时域波形中至少一个时域波形的时序延时超过第一阈值,输出所述互补单元存在断路的结果;

26、响应于所述合成时域波形比对参考时域波形在波形上不一致,且所述合成时域波形中至少一个时域波形的时序超前超过第二阈值,输出所述互补单元存在短路的结果。

27、本发明还提供了一种电子设备,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现如上述任一种所述的磁存储器检测方法。

28、上述磁存储器检测电路、方法及电子设备,采用充电后的第一充放电元件与第二充放电元件分别对磁性存储阵列中磁化状态相反的两个磁存储器件构成的互补单元进行放电,通过第一整形电路与第二整形电路对端电压整形后输出第一电压信号时域波形与第二电压信号时域波形,在同一时域坐标中组合后获得的组合时域波形,进而将组合时域波形与预设时域波形进行比较,获得互补单元的测试结果,该测试电路直接对磁性存储阵列中的互补单元进行测试,无需借助磁性存储芯片的内建测试电路,节约了磁性存储芯片的空间,改善了集成工艺,并且避免了因磁性存储芯片内建测试电路的pvt偏移造成的测试干扰,提高了检测精度。

技术特征:

1.一种磁存储器检测电路,其特征在于,所述检测电路包括:

2.根据权利要求1所述的磁存储器检测电路,其特征在于,所述第一整形电路与第二整形电路分别为第一整形反相器与第二整形反相器,分别用于将第一充放电元件与第二充放电元件的端电压转换为反相的方波信号,所述第一充放电元件与第二充放电元件为负载电容。

3.根据权利要求1所述的磁存储器检测电路,其特征在于,所述开关电路包括第一开关管、第二开关管、第三开关管与第四开关管,所述第一开关管与第三开关管的第一端用于连接第一电压,第二端分别连接所述第二开关管与第四开关管的第一端,以及分别连接第一充放电元件与第二充放电元件,所述第二开关管与第四开关管的第二端分别用于连接第一磁存储器件与第二磁存储器件。

4.根据权利要求1至3中任意一项所述的磁存储器检测电路,其特征在于,所述检测电路还包括第一d触发器与第二d触发器,所述第一d触发器的数据输入端连接第一整形电路的输出端,时钟信号输入端连接第二整形电路的输出端,所述第二d触发器的数据输入端连接第二整形电路的输出端,时钟信号输入端连接第一整形电路的输出端。

5.一种磁存储器检测方法,其特征在于,应用于权利要求1至4中任意一项所述的磁存储器检测电路,所述方法包括:

6.根据权利要求5所述的磁存储器检测方法,其特征在于,所述将所述组合时域波形同预设时域波形进行比对,得出所述互补单元的检测结果,包括:

7.根据权利要求5所述的磁存储器检测方法,其特征在于,所述将所述组合时域波形同预设时域波形进行比对,得出所述互补单元的检测结果,包括:

8.根据权利要求7所述的磁存储器检测方法,其特征在于,所述比对所述合成时域波形与所述参考时域波形,之后包括:

9.根据权利要求7所述的磁存储器检测方法,其特征在于,所述比对所述合成时域波形与所述参考时域波形,之后包括:

10.一种电子设备,包括存储器和处理器,所述存储器存储有计算机程序,其特征在于,所述处理器执行所述计算机程序时实现权利要求5至9中任一项所述的方法的步骤。

技术总结

本发明涉及一种磁存储器检测电路、方法及电子设备,该电路包括:开关电路、第一充放电元件、第二充放电元件、第一整形电路与第二整形电路,开关电路用于连接第一磁存储器件与第二磁存储器件,第一磁存储器件与第二磁存储器件的磁化状态相反,且为磁性存储阵列中的一个互补单元;开关电路用于控制第一充放电元件与第二充放电元件充电,或者通过互补单元放电;第一整形电路与第二整形电路分别用于将第一充放电元件与第二充放电元件的端电压整形为迅速变化的第一电压信号时域波形与第二电压信号时域波形,以在同一时域坐标中组合成组合时域波形后同预设时域波形进行比较,得出互补单元的检测结果。本发明节约了磁性存储芯片的空间,避免了测试干扰。

技术研发人员:欧乾雷,张和,王昭昊

受保护的技术使用者:致真存储(北京)科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!