一种启动时进行引脚内建自测试的芯片的制作方法

【】本发明涉及芯片dft(design for testability,可测试性设计)设计,特别涉及一种启动时进行引脚内建自测试(pad bist)的芯片。

背景技术

0、

背景技术:

1、针对芯片pad(焊盘或引脚)的测试是芯片整体测试的一个非常重要的组成部分,现有绝大多数芯片都是通过第三方工具在芯片设计阶段插入boundary scan chain(边界扫描链)来方便将来芯片裸片以及封装后的pad测试。传统的boundary scan(边界扫描)设计只能通过jtag(joint test action group,即联合测试工作组)接口对芯片的pad进行测试,通常是在ate(automatic test equipment,即集成电路自动测试机)机台上,或者测试板上,其成本低,测试简单。具体请参考图1所示,其为一种传统的boundary scan的结构示意图。

2、但是随着芯片可靠性要求的提高,在芯片应用系统中,特别是对于高可靠性要求的应用场景如自动驾驶芯片,需要感知因震动或者过热损坏的芯片pin脚,以提高系统安全。这就需要在每次启动时对自身所有pad进行自检,以确保pad可以正常工作。而传统的boundary scan设计无法支持此类应用场景需求。

3、因此,有必要提出一种新型的芯片pad自测试设计方案。

技术实现思路

0、

技术实现要素:

1、本发明的目的之一在于提供一种启动时进行引脚内建自测试的芯片,其可以在芯片启动时进行pad自检,并把结果存放到一个系统寄存器中,系统软件获得pad的自检状态(或自检结果)后做进一步处理,从而大大提高系统的整体安全性。

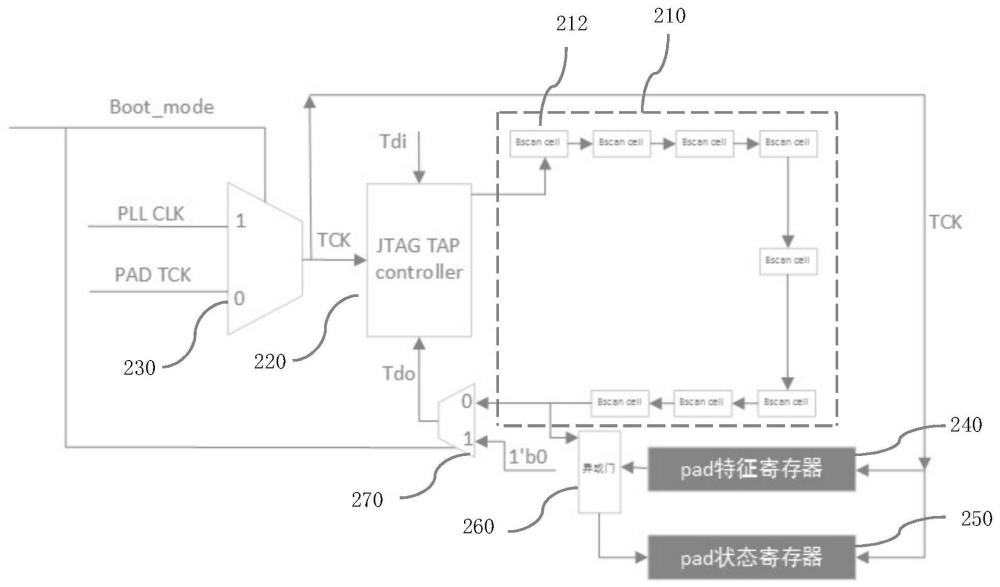

2、根据本发明的一个方面,本发明提供一种启动时进行引脚内建自测试的芯片,其包括:边界扫描链,其包括依次相连的多个边界扫描单元;测试时钟引脚、测试数据输出引脚、测试数据输入引脚;测试访问端口控制器,其与所述测试数据输出引脚和测试数据输入引脚分别相连;锁相环,其在芯片上电后启动,在所述锁相环锁定后,所述芯片使得启动模式信号有效;第一多路选择器,其包括接收所述锁相环输出的时钟信号的第一输入端、与所述测试时钟引脚相连的第二输入端、与所述测试访问端口控制器相连的输出端和接收所述启动模式信号的控制端;引脚特征寄存器,其内存储有多个特征值,其时钟端与所述第一多路选择器的输出端相连;引脚状态寄存器,其时钟端与所述第一多路选择器的输出端相连;比较单元,其包括与所述边界扫描链中的最后一个边界扫描单元相连的第一输入端、与所述引脚特征寄存器相连的第二输入端和与所述引脚状态寄存器相连的输出端。

3、与现有技术相比,本发明基于芯片现有boundary scan chain,在芯片boot(启动)的时候可以快速地做一次boundary scan(边界扫描)自测试并且把自检结果存放在一个系统寄存器中,系统启动后供软件读取分析处理,从而可以实现高可靠性的芯片pad自测试,大大提高系统的整体安全性。

技术特征:

1.一种启动时进行引脚内建自测试的芯片,其特征在于,其包括:

2.根据权利要求1所述的启动时进行引脚内建自测试的芯片,其特征在于,

3.根据权利要求2所述的启动时进行引脚内建自测试的芯片,其特征在于,

4.根据权利要求2所述的启动时进行引脚内建自测试的芯片,其特征在于,

5.根据权利要求4所述的启动时进行引脚内建自测试的芯片,其特征在于,其还包括第二多路选择器

6.根据权利要求1所述的启动时进行引脚内建自测试的芯片,其特征在于,

7.根据权利要求1-6任一所述的启动时进行引脚内建自测试的芯片,其特征在于,

技术总结

本发明提供一种启动时进行引脚内建自测试的芯片,其包括:边界扫描链;测试访问端口控制器,其与测试数据输出引脚和测试数据输入引脚相连;锁相环,其在芯片上电后启动,在锁相环锁定后,使得启动模式信号有效;第一多路选择器,其包括接收锁相环输出的时钟信号的第一输入端、与测试时钟引脚相连的第二输入端、与测试访问端口控制器相连的输出端和接收启动模式信号的控制端;引脚特征寄存器;引脚状态寄存器;比较单元,其包括与边界扫描链中的最后一个边界扫描单元相连的第一输入端、与引脚特征寄存器相连的第二输入端和与引脚状态寄存器相连的输出端。与现有技术相比,本发明可以实现高可靠性的芯片pad自测试,大大提高系统的整体安全性。

技术研发人员:仲留成

受保护的技术使用者:上海芯联芯智能科技有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!