基于氧化铟镓锌晶体管的电路单元、制备方法和电路架构

本公开涉及电路,更具体地涉及一种基于氧化铟镓锌晶体管的电路单元、制备方法和电路架构。

背景技术:

1、随着人工智能领域的飞速发展,基于存内计算的架构可以将存储单元和计算单元融为一体,以使得人工智能算法中的乘积累加(multiply-accumulate,mac)操作和内容搜索(content search)操作可以通过存内计算(computing-in-memory,cim)范式和按内容寻址存储(content-addressable memory,cam)范式高效的执行。

2、相关技术采用基于氧化铟镓锌晶体管(indium gallium zinc oxide,igzo)的2-transistor-0-capacitor(2t0c)电路单元结构实现存内计算操作。其中,读出氧化铟镓锌晶体管的栅氧层电容(gate oxide capacitance,cox)可以作为存储电容,用于存储数据。

3、在实现本公开构思的过程中,发明人发现相关技术中至少存在如下问题:相关技术中的电路单元结构基于氧化铟镓锌晶体管构建,电路单元结构的工作电压较高,工作频率较低,无法同时实现高能效的存内计算和按内容寻址存储操作。

技术实现思路

1、鉴于上述问题,本公开提供了基于氧化铟镓锌晶体管的电路单元、制备方法和电路架构。

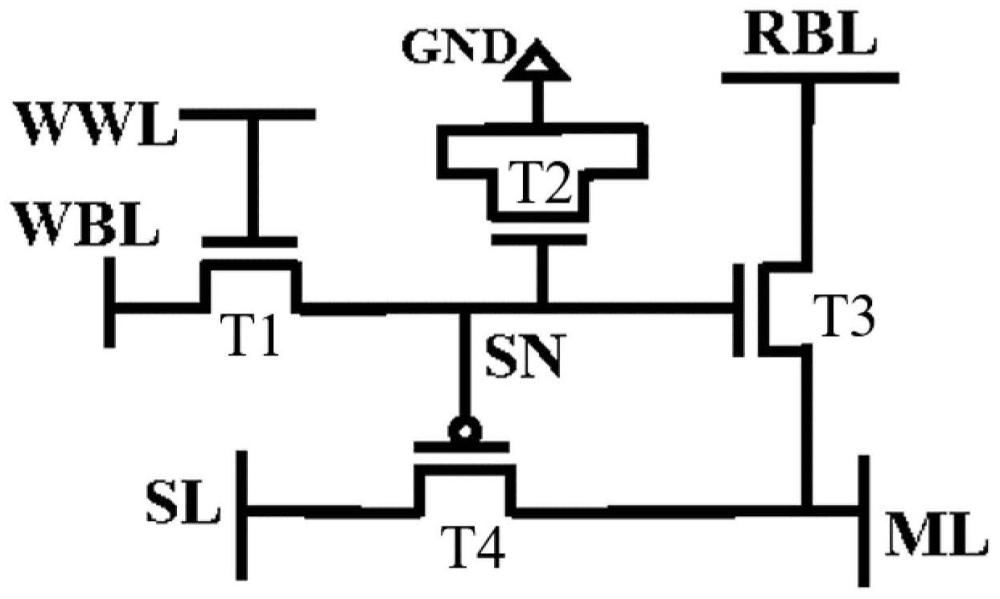

2、根据本公开的第一个方面,提供了一种基于氧化铟镓锌晶体管的电路单元,包括:第一氧化铟镓锌晶体管、第二氧化铟镓锌晶体管、n型场效应晶体管和p型场效应晶体管。其中,上述第一氧化铟镓锌晶体管的栅极连接写入字线端,上述第一氧化铟镓锌晶体管的源极连接写入位线端,上述第一氧化铟镓锌晶体管的漏极连接存储节点端。上述第二氧化铟镓锌晶体管的栅极连接上述存储节点端,上述第二氧化铟镓锌晶体管的源极和上述第二氧化铟镓锌晶体管的漏极连接地端。上述n型场效应晶体管的栅极连接上述存储节点端,上述n型场效应晶体管的源极连接匹配线端,上述n型场效应晶体管的漏极连接读出位线端。上述p型场效应晶体管的栅极连接上述存储节点端,上述p型场效应晶体管的源极连接匹配线端,上述p型场效应晶体管的漏极连接搜索线端。上述第一氧化铟镓锌晶体管用于控制上述电路单元执行写入操作。上述第一氧化铟镓锌晶体管和上述n型场效应晶体管用于共同控制上述电路单元执行读取操作。上述第一氧化铟镓锌晶体管、上述n型场效应晶体管和上述p型场效应晶体管用于共同控制上述电路单元执行内容搜索操作。上述第二氧化铟镓锌晶体管用于存储数据。

3、根据本公开的实施例,在上述写入字线端的输入电压为第一电压的情况下,上述第一氧化铟镓锌晶体管处于导通状态,上述电路单元执行写入操作。在上述写入字线端的输入电压为第二电压、上述读出位线端的输入电压为第三电压的情况下,上述第一氧化铟镓锌晶体管处于关闭状态,上述电路单元执行读取操作。

4、根据本公开的实施例,上述写入位线端的输入电压为第四电压的情况下,上述电路单元写入第一逻辑值。上述写入位线端的输入电压为第五电压的情况下,上述电路单元写入第二逻辑值。

5、根据本公开的实施例,在上述读出位线端的输入电压为第六电压,且上述搜索线端的输入电压为第七电压的情况下,上述电路单元执行内容搜索操作。

6、根据本公开的实施例,在上述匹配线端的输出电流为预设值的情况下,上述内容搜索操作的结果为搜索匹配。在上述匹配线端的输出电流不为零的情况下,上述内容搜索的结果为搜索不匹配。

7、本公开的第二方面提供了一种基于氧化铟镓锌晶体管的电路单元的制备方法,包括:将第一氧化铟镓锌晶体管和第二氧化铟镓锌晶体管制备于第一电路层。将n型场效应晶体管和p型场效应晶体管制备于第二电路层。其中,上述第一氧化铟镓锌晶体管用于控制上述电路单元执行写入操作。上述第一氧化铟镓锌晶体管和上述n型场效应晶体管用于共同控制上述电路单元执行读取操作。上述第一氧化铟镓锌晶体管、上述n型场效应晶体管和上述p型场效应晶体管用于共同控制上述电路单元执行内容搜索操作。上述第二氧化铟镓锌晶体管用于存储数据。

8、本公开的第三方面提供了一种基于氧化铟镓锌晶体管的电路架构,包括:电路阵列和外围电路。其中,上述外围电路与上述电路阵列相连接。上述电路阵列包括m×n个上述的电路单元,m,n均为大于1的整数。

9、根据本公开的实施例,第m行的上述电路单元的写入字线端之间相互连接,第m行的上述电路单元的搜索线端之间互相连接。第m行的上述电路单元的读出位线端之间互相连接。第n列的上述电路单元的写入位线端之间相互连接,第n列的上述电路单元的匹配线端之间相互连接。其中,m为大于等于1且小于等于m的整数,n为大于等于1且小于等于n的整数。

10、根据本公开的实施例,上述外围电路包括电流读取电路、模数转换电路、输入模块、逻辑运算电路和累加电路。其中,上述电流读取电路的输入端与上述电路单元的匹配线端相连接,用于读取上述电路单元的电流,上述电流读取电路的输出端与上述模数转换电路的输入端相连接,上述模数转换电路用于将模拟电流值转换为数字电压值。上述逻辑运算电路的输入端与上述输入模块和上述模数转换电路的输出端相连接。上述累加电路的输入端与上述逻辑运算电路的输出端相连接,用于对上述电路单元的逻辑运算结果进行累加。

11、根据本公开的实施例,上述逻辑运算电路包括与门逻辑电路;上述电流读取电路包括电流灵敏放大器;上述模数转换电路包括静态随机存取存储器单元。

12、根据本公开的实施例,本公开提供的基于氧化铟镓锌晶体管的电路单元,采用氧化铟镓锌晶体管、n型场效应晶体管和p型场效应晶体管的混合设计,一方面,场效应晶体管可以降低工作电压,降低电路单元的工作能耗。另一方面,场效应晶体管的充电速度快于氧化铟镓锌晶体管的充电速度,可以提升电路单元的工作速度,提高工作频率。而且,本公开提供的基于氧化铟镓锌晶体管的电路单元,基于第一氧化铟镓锌晶体管和n型场效应晶体管用于共同控制电路单元执行读取操作。基于第一氧化铟镓锌晶体管、n型场效应晶体管和p型场效应晶体管用于共同控制电路单元执行内容搜索操作。基于第二氧化铟镓锌晶体管进行数据的存储,以使得电路单元可以同时支持存内计算和按内容寻址存储操作。

技术特征:

1.一种基于氧化铟镓锌晶体管的电路单元,包括:

2.根据权利要求1所述的电路单元,其中,在所述写入字线端的输入电压为第一电压的情况下,所述第一氧化铟镓锌晶体管处于导通状态,所述电路单元执行写入操作;

3.根据权利要求2所述的电路单元,其中,所述写入位线端的输入电压为第四电压的情况下,所述电路单元写入第一逻辑值;

4.根据权利要求1所述的电路单元,其中,在所述读出位线端的输入电压为第六电压,且所述搜索线端的输入电压为第七电压的情况下,所述电路单元执行内容搜索操作。

5.根据权利要求1所述的电路单元,其中,在所述匹配线端的输出电流为预设值的情况下,所述内容搜索操作的结果为搜索匹配;

6.一种基于氧化铟镓锌晶体管的电路单元的制备方法,包括:

7.一种基于氧化铟镓锌晶体管的电路架构,包括:

8.根据权利要求7所述的电路架构,其中,第m行的所述电路单元的写入字线端之间相互连接,第m行的所述电路单元的搜索线端之间互相连接;第m行的所述电路单元的读出位线端之间互相连接;第n列的所述电路单元的写入位线端之间相互连接,第n列的所述电路单元的匹配线端之间相互连接;其中,m为大于等于1且小于等于m的整数,n为大于等于1且小于等于n的整数。

9.根据权利要求7所述的电路架构,其中,所述外围电路包括电流读取电路、模数转换电路、输入模块、逻辑运算电路和累加电路;

10.根据权利要求9所述的电路架构,其中,所述逻辑运算电路包括与门逻辑电路;所述电流读取电路包括电流灵敏放大器;所述模数转换电路包括静态随机存取存储器单元。

技术总结

本公开提供了一种基于氧化铟镓锌晶体管的电路单元、制备方法和电路架构,可以应用于电路技术领域。该电路单元包括:第一氧化铟镓锌晶体管、第二氧化铟镓锌晶体管、N型场效应晶体管和P型场效应晶体管。其中,第一氧化铟镓锌晶体管用于控制电路单元执行写入操作。第一氧化铟镓锌晶体管和N型场效应晶体管用于共同控制电路单元执行读取操作。第一氧化铟镓锌晶体管、N型场效应晶体管和P型场效应晶体管用于共同控制电路单元执行内容搜索操作。第二氧化铟镓锌晶体管用于存储数据。

技术研发人员:岳金山,郭泽钰,闫胜哲,戴卓玉,丛照日,李泠

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/8/21

- 还没有人留言评论。精彩留言会获得点赞!