存储芯片可靠性测试装置及存储芯片可靠性测试方法与流程

本申请涉及芯片测试,尤其涉及一种存储芯片可靠性测试装置及存储芯片可靠性测试方法。

背景技术:

1、存储芯片,也叫半导体存储器,是数字设备中用来存储信息的主要设备,在整个集成电路市场中占有相当重要的地位。存储芯片能够存储程序代码来处理各类数据,也能够存储中间数据和最终结果,是当前应用范围最广的基础性通用集成电路产品,各行各业所有电子产品设计都离不开存储芯片。

2、随着存储芯片的广泛应用,对其可靠性的要求也越来越高,因此,对存储芯片进行可靠性测试变得尤其重要。然而,由于存储芯片的可靠性测试涉及多个相互影响的参数指标,目前现有测试方法无法完全模拟存储芯片在实际工作环境中的复杂性和多变性,在测试过程仍需结合较多的人工操作和观察,导致测试效率和测试精度不高。

技术实现思路

1、本申请的目的旨在至少能解决上述的技术缺陷之一,特别是现有技术中无法完全模拟存储芯片在实际工作环境中的复杂性和多变性,在测试过程仍需结合较多的人工操作和观察,导致测试效率和测试精度不高的技术缺陷。

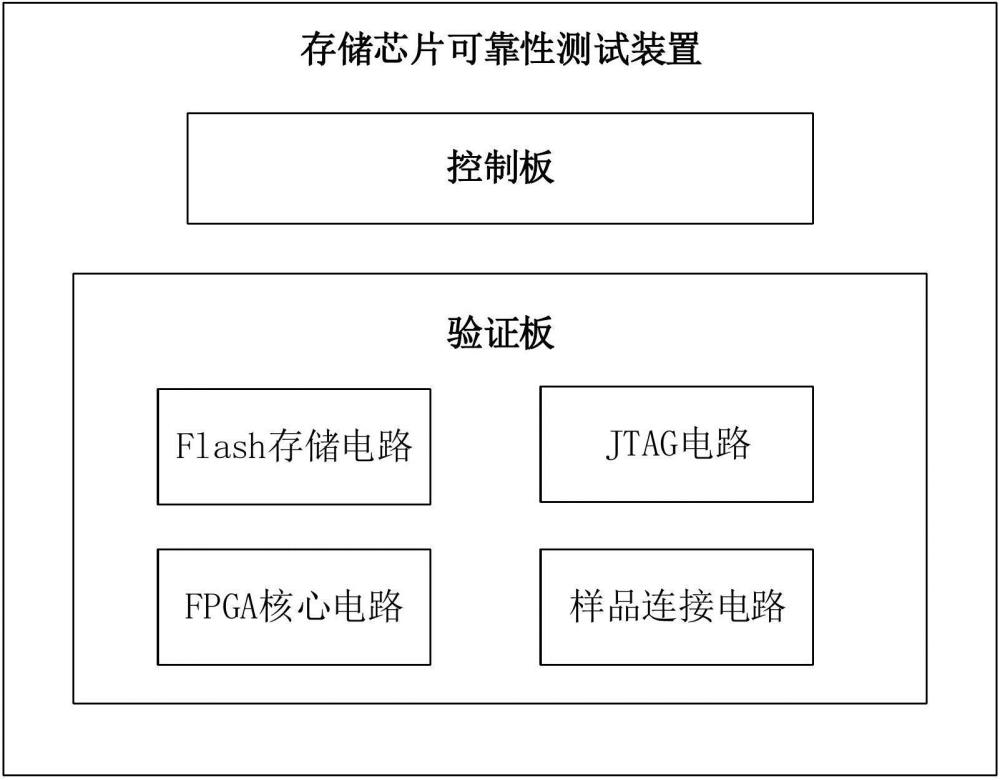

2、本申请提供了一种存储芯片可靠性测试装置,所述装置包括控制板和验证板;

3、所述控制板用于接收用户发送的测试指令,并根据所述测试指令生成控制信号,以对所述验证板进行管控;

4、所述验证板包括flash存储电路、jtag电路、fpga核心电路和样品连接电路;

5、所述flash存储电路用于存储待测芯片的测试程序;

6、所述jtag电路用于根据所述控制信号对所述flash存储电路中的测试程序进行配置和更改;

7、所述样品连接电路用于安装所述待测芯片;

8、所述fpga核心电路用于根据所述控制信号从所述flash存储电路中获取所述测试程序,并根据所述测试程序对所述待测芯片进行可靠性测试。

9、可选地,所述控制板包括转串口电路、按键电路、灯效电路;所述测试指令包括配置指令和按键指令;

10、所述转串口电路分别与上位机和所述jtag电路连接,用于通过所述上位机接收所述用户发送的配置指令时,根据所述配置指令生成第一控制信号,并将所述第一控制信号发送至所述jtag电路;

11、所述按键电路与所述样品连接电路的输入端连接,用于在接收到用户触发的按键指令时,根据所述生按键指令生成第二控制信号,并将所述第二控制信号发送至所述样品连接电路;

12、所述灯效电路与所述样品连接电路的输出端连接,用于通过所述样品连接电路接收所述待测芯片在测试过程中返回的状态信号,并根据所述状态信号进行亮灯操作。

13、可选地,所述控制板还包括控制板连接器;所述验证板还包括验证板连接器;

14、所述控制板连接器与所述验证板连接器进行连接,以实现所述控制板与所述验证板之间的通信。

15、可选地,所述验证板还包括复位电路和时钟电路;

16、所述复位电路用于将所述存储芯片可靠性测试装置重置到初始状态;

17、所述时钟电路用于为所述存储芯片可靠性测试装置中的各个电路提供时钟信号。

18、可选地,所述验证板还包括电源电路;

19、所述电源电路用于对所述待测芯片的测试过程进行电力提供。

20、可选地,所述验证板还包括jtag保护电路;

21、所述jtag保护电路用于对所述jtag电路进行过压保护。

22、本申请还提供了一种存储芯片可靠性测试方法,应用于如上述实施例中所述的存储芯片可靠性测试装置中的控制板,所述方法包括:

23、确定待测芯片测试所需的目标温度,并通过热流罩将所述存储芯片可靠性测试装置的测试温度调整至所述目标温度;

24、在检测到用户发送的测试指令时,根据所述测试指令生成控制信号,并基于所述控制信号从验证板中获取与所述测试指令对应的测试程序;

25、在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,并接收所述待测芯片返回的状态信号,以基于所述状态信号确定所述待测芯片的测试结果。

26、可选地,所述在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,包括:

27、当所述测试程序的测试类型为功耗测试时,确定所述功耗测试的第一数据规格,并生成与所述第一数据规格对应的随机数据;

28、将所述随机数据写入所述待测芯片中,并在数据写入的过程中,通过所述验证板对所述待测芯片进行持续的读入操作和功耗测试操作,以实现所述待测芯片的功耗测试。

29、可选地,所述在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,还包括:

30、当所述测试程序的测试类型为工作测试时,确定所述工作测试的第二数据规格,并生成与所述第二数据规格对应的随机数据;

31、将所述随机数据写入所述待测芯片中,并在数据写入的过程中,遍历所述待测芯片中的各个ip地址,并通过所述验证板对每一ip地址进行读入操作、稳定测试操作和校验操作,以实现所述待测芯片的工作测试。

32、可选地,所述在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,还包括:

33、当所述测试程序的测试类型为参数测试时,确定所述参数测试的第三数据规格,并生成与所述第三数据规格对应的随机数据;

34、将所述随机数据写入所述待测芯片中,并在数据写入的过程中,确定所述待测芯片中的各个存储单元,并通过所述验证板对每一存储单元进行容量测试操作和读写速度测试操作,以实现所述待测芯片的参数测试。

35、从以上技术方案可以看出,本申请实施例具有以下优点:

36、本申请提供的存储芯片可靠性测试装置及存储芯片可靠性测试方法,用户可以在存储芯片可靠性测试装置中对待测芯片进行可靠性检测。该装置包括了控制板和验证板,展开来讲,控制板可以接收用户发送的测试指令,并根据测试指令生成控制信号,并利用该控制信号控制验证板对待测芯片进行可靠性测试,以通过自动化测试来提高待测芯片的测试效率和测试精度。此外,验证板包括了flash存储电路、jtag电路、fpga核心电路和样品连接电路。其中,flash存储电路可以存储待测芯片的测试程序,以适配不同维度的可靠性测试,进而提高测试精度;jtag电路可以根据控制板的控制信号来对flash存储电路中的测试程序进行配置和更改,从而灵活扩展芯片测试范围,减少成本浪费;样品连接电路可以安装待测芯片,从而实现对各种待测芯片进行测试;而fpga核心电路可以根据控制信号从flash存储电路中获取测试程序,并根据测试程序对所述待测芯片进行可靠性测试,从而提高待测芯片与测试程序的适配度,进而提高测试精度。

技术特征:

1.一种存储芯片可靠性测试装置,其特征在于,所述装置包括控制板和验证板;

2.根据权利要求1所述的存储芯片可靠性测试装置,其特征在于,所述控制板包括转串口电路、按键电路、灯效电路;所述测试指令包括配置指令和按键指令;

3.根据权利要求1所述的存储芯片可靠性测试装置,其特征在于,所述控制板还包括控制板连接器;所述验证板还包括验证板连接器;

4.根据权利要求1所述的存储芯片可靠性测试装置,其特征在于,所述验证板还包括复位电路和时钟电路;

5.根据权利要求1所述的存储芯片可靠性测试装置,其特征在于,所述验证板还包括电源电路;

6.根据权利要求1所述的存储芯片可靠性测试装置,其特征在于,所述验证板还包括jtag保护电路;

7.一种存储芯片可靠性测试方法,应用于如上述权利要求1-6中任一项所述的存储芯片可靠性测试装置中的控制板,其特征在于,所述方法包括:

8.根据权利要求7所述的存储芯片可靠性测试方法,其特征在于,所述在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,包括:

9.根据权利要求7所述的存储芯片可靠性测试方法,其特征在于,所述在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,还包括:

10.根据权利要求7所述的存储芯片可靠性测试方法,其特征在于,所述在所述验证板中根据所述测试程序对所述待测芯片进行可靠性测试,还包括:

技术总结

本申请提供的存储芯片可靠性测试装置及存储芯片可靠性测试方法,该装置包括了控制板和验证板,控制板可以接收用户的测试指令,并根据测试指令控制验证板对待测芯片进行可靠性测试,以通过自动化测试来提高测试效率和测试精度。此外,验证板包括了Flash存储电路、JTAG电路、FPGA核心电路和样品连接电路。其中,Flash存储电路可以存储待测芯片的测试程序,以适配不同维度的测试;JTAG电路可以对测试程序进行配置和更改,从而提高测试的灵活性;样品连接电路可以安装待测芯片;而FPGA核心电路可以获取相应的测试程序,并根据测试程序对待测芯片进行可靠性测试,从而提高待测芯片与测试程序的适配度,进而提高测试精度。

技术研发人员:熊俊,王勇,陈俊,陈勉之,孔令明,肖百惠

受保护的技术使用者:广东电网有限责任公司广州供电局

技术研发日:

技术公布日:2024/7/25

- 还没有人留言评论。精彩留言会获得点赞!