运用于非易失性存储器的感测放大器的制作方法

本发明涉及一种感测放大器,且特别涉及一种运用于非易失性存储器的感测放大器。

背景技术:

1、众所周知,非易失性存储器内的存储器胞阵列(memory cell array)中包括多个存储器胞(memory cell)。而存储器胞至少包括一选择元件(selecting device)与一存储元件(storage device)。举例来说,存储元件可为浮动栅晶体管(floating gatetransistor)、反熔丝晶体管(antifuse type transistor)或者是电阻式元件(resistiveelement)。以下简单说明之。

2、浮动栅晶体管中的浮动栅极(floating gate)可以存储热载子(hot carrier),例如电子。根据热载子存储量的多寡即可决定存储器胞的存储状态。举例来说,在非易失性存储器的编程周期(program cycle),控制注入浮动栅极的热载子数量,即可改变浮动栅晶体管的临限电压(threshold voltage),并进而改变存储器胞的存储状态。而在读取动作(read action)时,提供一读取电压(read voltage)至浮动栅晶体管,便可以产生存储器胞电流(cell current),或称为读取电流(read current)。而根据存储器胞电流的大小,即可判断存储器胞的存储状态为第一存储状态或者第二存储状态。以p型浮动栅晶体管为例,在读取动作时,如果浮动栅极未存储热载子,则存储器胞产生的存储器胞电流非常小(几乎为零),可视为第一存储状态。反之,如果浮动栅极存储热载子时,则存储器胞产生的存储器胞电流较大,可视为第二存储状态。

3、反熔丝晶体管可以根据栅极介电层(gate dielectric layer)破裂与否来决定其存储状态。在非易失性存储器的编程动作时,提供编程电压至反熔丝晶体管,使得反熔丝晶体管的栅极介电层破裂,并进而改变存储器胞的存储状态。而在读取动作(read action)时,提供一读取电压(read voltage)至反熔丝晶体管,便可以产生存储器胞电流(cellcurrent),或称为读取电流(read current)。而根据存储器胞电流的大小,即可判断存储器胞的存储状态为第一存储状态或者第二存储状态。举例来说,在读取动作时,如果反熔丝晶体管的栅极介电层未破裂时,则存储器胞产生的存储器胞电流非常小(几乎为零),可视为第一存储状态。反之,如果反熔丝晶体管的栅极介电层破裂时,则存储器胞产生的存储器胞电流较大,可视为第二存储状态。

4、再者,提供不同偏压(bias voltage)至电阻式元件,可控制电阻式元件在高电阻值与低电阻值之间切换,而根据电阻值的大小即可决定该存储器胞的存储状态。举例来说,在非易失性存储器的编程周期(program cycle)时,提供不同偏压用以控制电阻式元件的电阻值大小。而在读取动作(read action)时,提供一读取电压(read voltage)至电阻式元件,便可以产生存储器胞电流(cell current),或称为读取电流(read current)。而根据存储器胞电流的大小,即可判断存储器胞的存储状态为第一存储状态或者第二存储状态。

5、由以上的说明可知,在非易失性存储器中更需要提供一感测放大器(senseamplifier),用来接收存储器胞产生的存储器胞电流,并判断存储器胞的存储状态。

技术实现思路

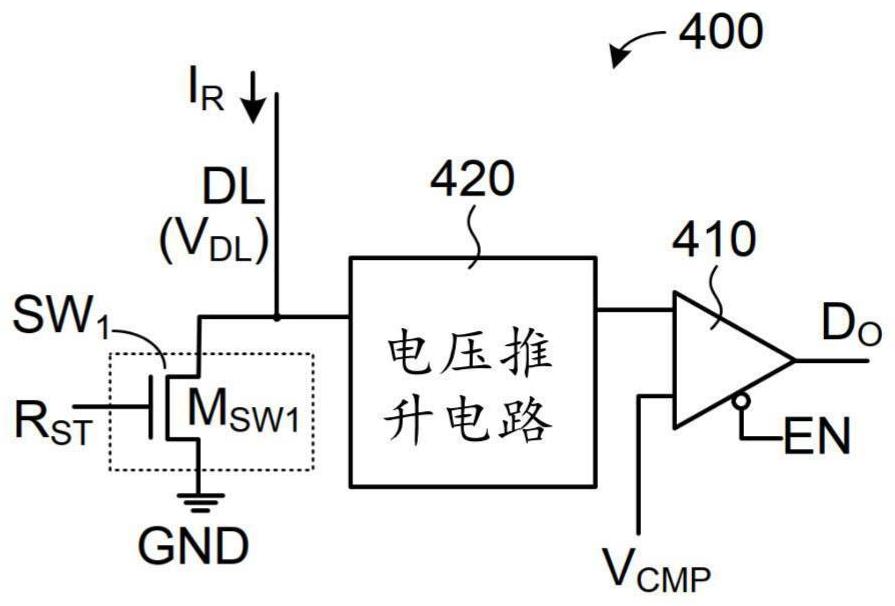

1、本发明涉及一种运用于非易失性存储器的一感测放大器,该非易失性存储器中的一第一存储器胞耦接至一数据线,该感测放大器包括:一第一开关元件,该第一开关元件的一第一端连接至该数据线,该第一开关元件的一第二端连接至一接地端,该第一开关元件的一控制端接收一第一控制信号,且该第一控制信号为一重置信号;一第一电压推升电路,该第一电压推升电路的一输入端连接至该数据线,该第一电压推升电路的一输出端连接至一感测节点;以及,一比较器,该比较器的一第一输入端接收一比较电压,该比较器的一第二输入端连接至该感测节点,该比较器的一输出端产生一输出数据;其中,在一读取动作的一重置阶段时,该数据线上的一数据线电压被重置为一接地电压,且该感测节点的一感测电压被重置为该接地电压;其中,在该读取动作中该重置阶段后的一充电阶段时,该第一存储器胞产生的一第一存储器胞电流充电该数据线,且该第一电压推升电路将该感测电压调整至该数据线电压;其中,在该读取动作中该充电阶段后的一推升阶段时,该第一电压推升电路将该感测电压调整至该数据线电压加上一第一电压增量;其中,该比较器根据该比较电压与该感测电压产生该输出数据用以决定该第一存储器胞的一存储状态。

2、为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合附图,作详细说明如下:

技术特征:

1.一种运用于非易失性存储器的感测放大器,该非易失性存储器中的第一存储器胞耦接至数据线,该感测放大器包括:

2.如权利要求1所述的感测放大器,其中该第一开关元件为第一晶体管,该第一晶体管的第一漏/源端连接至该数据线,该第一晶体管的第二漏/源端连接至该接地端,该第一晶体管的栅极端接收该第一控制信号。

3.如权利要求1所述的感测放大器,其中该比较器包括一致能端,接收一致能信号;以及,在该读取动作的该推升阶段结束时,该致能信号动作,该比较器根据该比较电压与该感测电压产生该输出数据。

4.如权利要求1所述的感测放大器,其中该第一电压推升电路包括推升元件,该推升元件的输入端连接第一节点,且该第一节点连接至该数据线,该推升元件的输出端连接至该感测节点,该推升元件包括:

5.如权利要求4所述的感测放大器,其中,在该读取动作的该重置阶段时,该第一开关元件、该第二开关元件、该第三开关元件与该第四开关元件为闭合状态,该数据线电压与该感测电压被重置为该接地电压;在该读取动作的该充电阶段时,该第二开关元件与该第四开关元件为该闭合状态,该第一开关元件与该第三开关元件为断开状态,该数据线电压等于该感测电压;以及,在该读取动作的该推升阶段时,该第三开关元件为该闭合状态,该第一开关元件、该第二开关元件与该第四开关元件为该断开状态,该感测电压等于该数据线电压加上该第一电压增量。

6.如权利要求1所述的感测放大器,其中该第一电压推升电路包括推升元件,该推升元件的输入端连接第一节点,且该第一节点连接至该数据线,该推升元件的输出端连接至该感测节点,该推升元件包括:

7.如权利要求6所述的感测放大器,其中该第一电容器包括第五晶体管,该第五晶体管的第一漏/源端与第二漏/源端连接至该第二节点,该第五晶体管的栅极端连接至该感测节点。

8.如权利要求7所述的感测放大器,其中该第五晶体管为耗尽型晶体管。

9.如权利要求1所述的感测放大器,其中该第一电压推升电路包括n个推升元件,n为大于1的正整数;在该n个推升元件中,第一推升元件的输入端连接至第一节点,第n推升元件的输出端连接至该感测节点,其他推升元件的输入端连接至前一个推升元件的输出端,其他推升元件的输出端连接至后一个推升元件的输入端;以及,该第一点连接至该数据线。

10.如权利要求9所述的感测放大器,其中该第一推升元件包括:

11.如权利要求9所述的感测放大器,其中该第一推升元件包括:

12.如权利要求11所述的感测放大器,其中该第一电容器包括第五晶体管,该第五晶体管的第一漏/源端与第二漏/源端连接至该第三节点,该第五晶体管的栅极端连接至该第二节点。

13.如权利要求12所述的感测放大器,其中该第五晶体管为耗尽型晶体管。

14.如权利要求1所述的感测放大器,还包括:

15.如权利要求1所述的感测放大器,还包括:

技术总结

一种运用于非易失性存储器的一感测放大器。非易失性存储器中的第一存储器胞耦接至数据线。感测放大器包括:第一开关元件、第一电压推升电路与比较器。第一开关元件的第一端连接至数据线,第一开关元件的第二端连接至接地端,第一开关元件的控制端接收重置信号。第一电压推升电路的输入端连接至数据线,第一电压推升电路的输出端连接至一感测节点(sensing node)。比较器的第一输入端接收比较电压,比较器的第二输入端连接至感测节点,比较器的一输出端产生输出数据。

技术研发人员:古惟铭

受保护的技术使用者:力旺电子股份有限公司

技术研发日:

技术公布日:2024/12/17

- 还没有人留言评论。精彩留言会获得点赞!