一种数据缓存的自愈机制系统及设计方法与流程

本发明涉及一种数据缓存的自愈机制系统及设计方法,属于计算、通信。

背景技术:

1、sram是数字芯片中不可或缺的一类存储器,具备读写速度快、使用寿命长等优势,以及数据易失、成本高等特点,常用于cpu、gpu、mcu、交换、路由等芯片的缓存模块。随着市场对高算力、高吞吐、高处理速度芯片的需求日益增长以及设计制造技术愈发先进,sram在芯片中的作用越来越重要。

2、sram作为芯片的缓存模块,接收cpu/dma等主设备发来的数据读写指令,根据地址信息实现相关数据存储、发送、转移等系统功能。

3、愈趋尖端的纳米级晶体管技术在制造过程中会造成sram的缺陷,包括sta(stuckat fault)、tf(transition fault)、cf(coupling fault)等导致数据异常的可能故障,因此sram缓存的数据正确性必须经过检测。当前,用来检测sram数据正确的技术包括奇偶校验、mbist、ecc等。

4、其中,奇偶校验,是通过在数据末端添加一个奇或偶校验位来检测数据传输过程中是否发生错误。奇偶校验实现简单,只能检测奇偶数位错误,无法纠正错误,对2比特以上的错误不能保证能检测。

5、dft中的mbist,通过内建自测电路,实现对片内数据缓存的检测,一般用于芯片大规模晶圆和成品筛选。mbist需要增加大量的自测试电路,增加了芯片设计的复杂性,且只能检查缓存电路的缺陷或故障,不能纠正缓存错误。

6、ecc通过编码方式,在数据位上额外的位存储一个用数据加密的代码,能纠正单比特错误和检测双比特错误,而且计算速度很快,但对1比特以上的错误无法纠正,对2比特以上的错误不能保证能检测,而且需要消耗数据缓存的12.5%(以每8字节数据一个ecc校验码为例),用来存储ecc校验码。

技术实现思路

1、本发明的目的是:基于现有技术对缓存故障修复的不足之处,通过设计来实现一种既能检测出故障缓存,又能纠正缓存中单比特和多比特错误的功能。

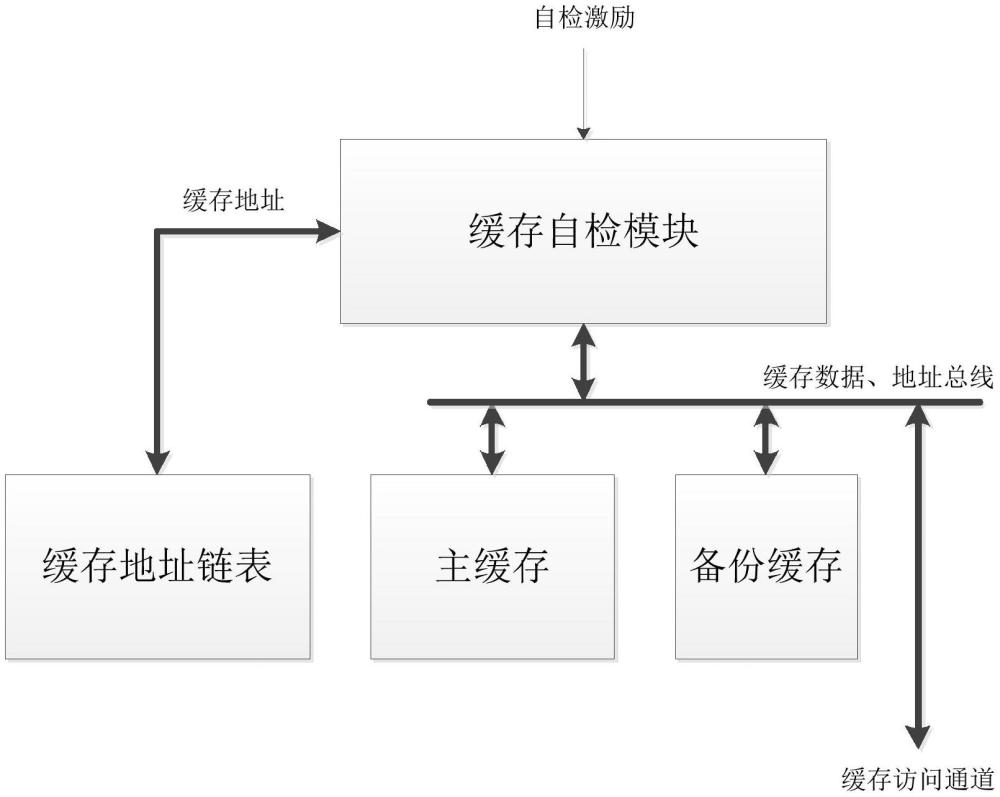

2、为了达到上述目的,本发明的一个技术方案是提供了一种数据缓存的自愈机制系统,其特征在于,包括缓存自检模块、缓存地址链表、主缓存以及备份缓存,其中:

3、缓存自检模块与缓存地址链表相连,对有效缓存地址和故障缓存地址进行管理;同时,缓存自检模块与主缓存一级备份缓存相连,对缓存进行数据自检;

4、缓存地址链表包括:有效缓存地址链表的数据结构和作为空闲缓存地址链表所需的指针管理;

5、主缓存由任意大小容量的sram存储阵列组成,与缓存自检模块以及缓存访问设备相连,用于数据缓存。

6、备份缓存包括由任意大小容量的sram存储阵列组成,与缓存自检模块以及缓存访问设备相连,用于主缓存出现部分缓存故障时的数据缓存。

7、优选地,所述缓存自检模块包括:缓存故障模型的导入,数据缓存的逐地址自动检测,有效缓存地址链表的建立和故障缓存地址的替换。

8、优选地,所述备份缓存的容量为主缓存容量的1‰。

9、本发明的另一个技术方案是提供了一种数据缓存的自愈机制设计方法,其特征在于,包括以下步骤:

10、步骤s1:系统复位后,进入数据缓存自检流程;

11、步骤s2:通过预置的数据模式或软件配置,加载各模式数据;

12、步骤s3:若通过各模式数据比对,则标识为有效缓存;若未通过数据比对,则标识为故障缓存,并建立有效缓存地址链表;

13、步骤s4:有故障缓存标志的缓存地址被备份缓存的缓存地址替代,更新至有效缓存地址链表;

14、步骤s5:结束主缓存所有地址检查,系统退出数据缓存自检状态。

15、优选地,在所述步骤s2中:针对缓存故障模型,采用四种或多种自定义模式的数据,覆盖缓存七种主要的故障行为。

16、优选地,在所述步骤s3中:从主缓存初始地址开始,依次加载模式1、2、3、4数据,并通过读取该缓存地址进行数据比对:若比对一致,则表明该地址的缓存有效,写入有效缓存地址链表,通过四种模式数据比对后,自动进行下一个地址的数据比对。

17、优选地,在所述步骤s4中:在缓存地址链表的数据结构中,有一位备份标识,0表示主缓存地址有效,1表示主缓存地址由备份缓存地址替代,保证了缓存地址链表中的所有缓存都是有效的、无故障的。

18、本发明提供了一种数据缓存的自愈机制系统及设计方法,通过多模式数据对缓存的检测,及屏蔽故障缓存地址、采用备份缓存替代故障缓存、建立有效缓存地址链表的方法,在保证可使用的数据缓存容量等同的情况下,实现了数据缓存的自我修复,达到了自愈效果。

19、与现有技术方案相比,本发明具体具有如下有益效果:

20、1、本发明通过备份缓存替代错误缓存的方法,解决了现有技术无法很好处理的多比特错误缓存问题,另外通过数据缓存的逐地址自动检测,达到缓存自检的功能;

21、2、本发明涉及的电路相比ecc电路,开销比较低,备份缓存只占主缓存的1‰;

22、3、本发明涉及的数据缓存自愈机制,可修复数据缓存中的故障sram,提高芯片良率,降低芯片成本。

技术特征:

1.一种数据缓存的自愈机制系统,其特征在于,包括缓存自检模块、缓存地址链表、主缓存以及备份缓存,其中:

2.如权利要求1所述的一种数据缓存的自愈机制系统,其特征在于,所述缓存自检模块包括:缓存故障模型的导入,数据缓存的逐地址自动检测,有效缓存地址链表的建立和故障缓存地址的替换。

3.如权利要求1所述的一种数据缓存的自愈机制系统,其特征在于,所述备份缓存的容量为主缓存容量的1‰。

4.一种数据缓存的自愈机制设计方法,其特征在于,包括以下步骤:

5.如权利要求4所述的一种数据缓存的自愈机制设计方法,其特征在于,在所述步骤s2中:针对缓存故障模型,采用四种或多种自定义模式的数据,覆盖缓存七种主要的故障行为。

6.如权利要求4所述的一种数据缓存的自愈机制设计方法,其特征在于,在所述步骤s3中:从主缓存初始地址开始,依次加载模式1、2、3、4数据,并通过读取该缓存地址进行数据比对:若比对一致,则表明该地址的缓存有效,写入有效缓存地址链表,通过四种模式数据比对后,自动进行下一个地址的数据比对。

7.如权利要求4所述的一种数据缓存的自愈机制设计方法,其特征在于,在所述步骤s4中:在缓存地址链表的数据结构中,有一位备份标识,0表示主缓存地址有效,1表示主缓存地址由备份缓存地址替代,保证了缓存地址链表中的所有缓存都是有效的、无故障的。

技术总结

本发明的一个技术方案是提供了一种数据缓存的自愈机制系统,其特征在于,包括缓存自检模块、缓存地址链表、主缓存以及备份缓存。本发明的另一个技术方案是提供了一种数据缓存的自愈机制设计方法。本发明提供了一种数据缓存的自愈机制系统及设计方法,通过多模式数据对缓存的检测,及屏蔽故障缓存地址、采用备份缓存替代故障缓存、建立有效缓存地址链表的方法,在保证可使用的数据缓存容量等同的情况下,实现了数据缓存的自我修复,达到了自愈效果。

技术研发人员:刘宇,徐国强,于建旺,於健,赵永建,马鹏,郑海燕,王叶辉,吴丽平,王芸,许伟领

受保护的技术使用者:华东计算技术研究所(中国电子科技集团公司第三十二研究所)

技术研发日:

技术公布日:2024/9/5

- 还没有人留言评论。精彩留言会获得点赞!