增强用于存储器修复机制的区域有效性的通信逻辑的制作方法

本公开一般而言涉及测试设计(dft),并且在特定实施例中,涉及用于测试和修复存储器的改善的系统体系架构。

背景技术:

1、硬件加速器,诸如图形处理单元(gpu)、现场可编程门阵列(fpga)和专用集成电路(asic),都是被设计为比传统通用处理器更高效地执行特定任务的专门硬件设备。随着数据集的尺寸和模型的复杂性增加,硬件加速器在机器学习和人工智能中的使用变得越来越重要,这导致跨片上系统(soc)的存储器计数和存储器散布均增加。

2、在ai和机器学习领域,硬件加速器可以加速机器学习模型的训练和推理中所涉及的计算密集型任务。通过将计算卸载到专门硬件,机器学习算法可以被更快且更高效地进行训练和部署,从而使得基于ai的产品和服务的性能更好且上市时间更快。

3、一般而言,硬件加速器要求大量存储器空间才能有效操作,并且要求存储大量数据,例如训练数据集、模型参数和计算中间结果。因此,硬件加速器中的存储器变得越来越复杂,需要更多的存储器信道和更高的存储器带宽来支持机器学习和ai工作负载的日益增长的需求。此外,随着工作负载尺寸的不断增长,支持它们所需的存储器量也增加。

4、传统上,使用分层方法来测试和修复存储器,通过抽象底层存储器子系统的细节并提供用于错误检测和纠正的标准化接口简化存储器修复处理。在分层方法中,存储器子系统被划分为多个抽象级别,每个抽象级别具有自己的测试和包装器的集合。顶级包装器与外部环境接口并为较低级别的包装器生成测试模式。较低级别的包装器在其相应的抽象级别验证存储器的功能性和性能并向顶级包装器提供反馈。

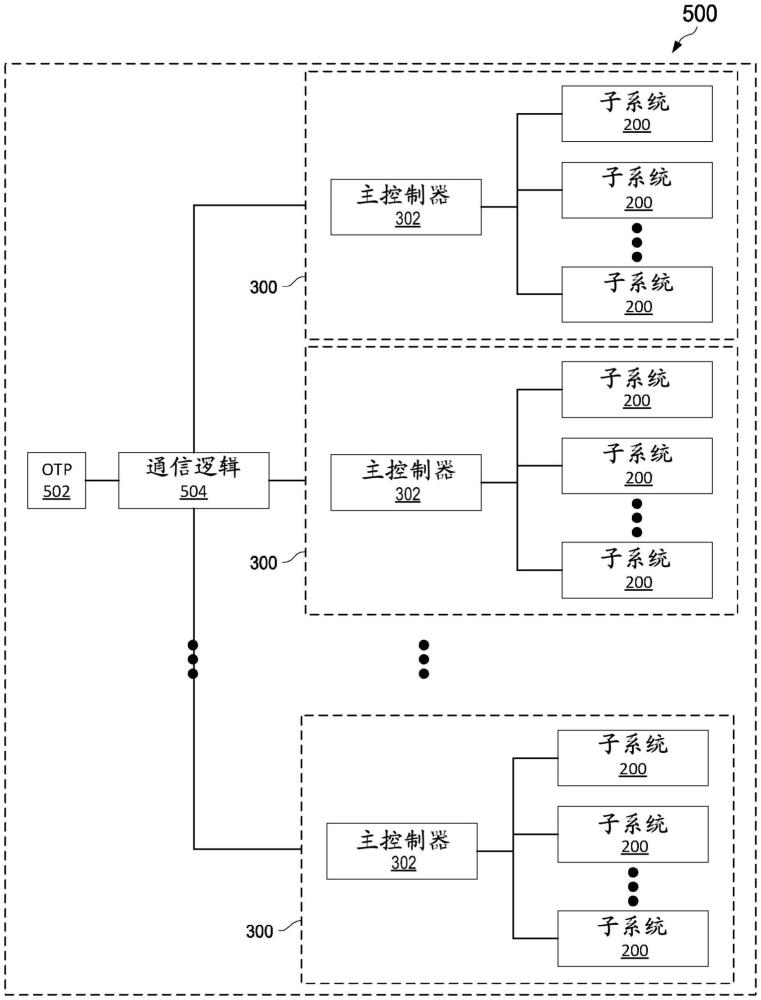

5、常规而言,通过测试访问点(tap)加载指令并与一次性可编程(otp)存储器通信是通过分层方法的顶部主控制器/子控制器系统体系架构完成的。由于综合约束和多个处理核心,因此在人工智能和机器学习应用中使用多个控制器,使得每个系统都需要专用otp存储器。但是,每个系统不一定使用整个otp存储器空间来存储修复数据,这导致存储器浪费。

6、存储器测试处理器基于存储器故障位置计算修复签名,以使用分层方法修复存储器。修复签名在制造测试期间存储在otp存储器中。在现场,在上电序列期间,从otp存储器读取修复签名并将其加载到存储器修复签名寄存器中。

7、因此,期望改善的系统体系架构来测试和修复存储器。

技术实现思路

1、由本公开的实施例一般地实现技术优势,本公开的实施例描述了用于测试和修复存储器的改善的系统体系架构。

2、第一方面涉及用于测试和修复硬件加速器中的本地存储器的系统。该系统包括一次性可编程(otp)存储器、otp定序器电路、第一主控制器、第二主控制器以及偏移添加和选择逻辑电路。一次性可编程(otp)存储器被配置为按顺序在第一分区中存储第一修复数据并在第二分区中存储第二修复数据以分别用于本地存储器的第一子集和本地存储器的第二子集。otp定序器电路被配置为断言第一授权信号。第一主控制器耦合到otp定序器电路和本地存储器的第一子集。第一主控制器被配置为从第一分区第一次加载用于本地存储器的第一子集的第一修复数据,并在第一次加载完成之后向otp定序器电路传送指示第一次加载完成的第一状态信号。otp定序器电路还被配置为响应于otp定序器电路接收到第一状态信号而解除断言第一授权信号并且响应于第一授权信号的解除断言而断言第二授权信号。偏移添加和选择逻辑电路被配置为向由第二主控制器使用来访问第二分区的地址添加偏移。第二主控制器被配置为使用访问第二分区的地址从第二分区第二次加载用于与第二主控制器相关联的本地存储器的第二子集的第二修复数据,并且在第二次加载完成之后向otp定序器电路传送指示第二次加载完成的第二状态信号。otp定序器电路还被配置为响应于otp定序器电路接收到第二状态信号而解除断言第二授权信号。

3、第二方面涉及用于从一次性可编程存储器(otp)测试和修复硬件加速器中的本地存储器的方法。该方法包括:由一次性可编程(otp)定序器电路断言第一授权信号;由第一主控制器从otp存储器的第一分区第一次加载用于与第一主控制器相关联的本地存储器的第一子集的第一修复数据;由第一主控制器在第一次加载完成之后向otp定序器电路传送指示第一次加载完成的第一状态信号;由otp定序器电路响应于otp定序器电路接收到第一状态信号而解除断言第一授权信号;由otp定序器电路响应于第一授权信号的解除断言而断言第二授权信号;由偏移添加和选择逻辑电路将偏移添加到由第二主控制器使用来访问otp存储器的包括第二修复数据的第二分区的地址,其中第一修复数据和第二修复数据被按顺序加载到otp存储器中;由第二主控制器使用访问第二分区的地址从otp存储器的第二分区第二次加载用于与第二主控制器相关联的本地存储器的第二子集的第二修复数据;由第二主控制器在第二次加载完成之后向otp定序器电路传送指示第二次加载完成的第二状态信号;以及由otp定序器电路响应于otp定序器电路接收到第二状态信号而解除断言第二授权信号。

4、第三方面涉及用于测试和修复硬件加速器中的本地存储器的系统。该系统包括一次性可编程(otp)存储器、测试控制寄存器(tcr)、第一主控制器、第二主控制器以及偏移添加和选择逻辑电路。otp存储器被配置为按顺序将第一修复数据存储在第一分区中并将第二修复数据存储在第二分区中以分别用于本地存储器的第一子集和本地存储器的第二子集。tcr被配置为断言第一授权信号。第一主控制器耦合到本地存储器的第一子集,第一主控制器被配置为响应于第一授权信号被断言而从第一分区第一次加载用于本地存储器的第一子集的第一修复数据。偏移添加和选择逻辑电路耦合到tcr和第一主控制器。偏移添加和选择逻辑电路被配置为将偏移添加到由第二主控制器使用来访问第二分区的地址。tcr还被配置为解除断言第一授权信号并响应于第一授权信号的解除断言而断言第二授权信号。第二主控制器被配置为响应于第二授权信号被断言而使用访问第二分区的地址从第二分区第二次加载用于与第二主控制器相关联的本地存储器的第二子集的第二修复数据,其中tcr还被配置为解除断言第二授权信号。

5、实施例可以以硬件、软件或其任何组合来实现。

技术特征:

1.一种用于测试和修复硬件加速器中的本地存储器的系统,该系统包括:

2.如权利要求1所述的系统,其中,otp定序器电路被配置为响应于otp定序器电路接收到功能模式复位信号而生成第一授权信号。

3.如权利要求1所述的系统,还包括耦合到第一主控制器和otp定序器电路的第一修复控制器,其中otp定序器电路被配置为响应于接收到第一授权信号而指示第一主控制器通过第一修复控制器加载第一修复数据。

4.如权利要求1所述的系统,还包括耦合到第二主控制器和otp定序器电路的第二修复控制器,其中otp定序器电路被配置为响应于接收到第二授权信号而指示第二主控制器通过第二修复控制器加载第二修复数据。

5.如权利要求1所述的系统,其中,硬件加速器包括图形处理单元(gpu)、现场可编程门阵列(fpga)、专用集成电路(asic)或其组合。

6.如权利要求1所述的系统,其中,硬件加速器用于人工智能或机器学习。

7.如权利要求1所述的系统,其中,在otp存储器中在第一修复数据之后按顺序存储第二修复数据,使得添加到所述地址的偏移指向紧接在第一修复数据之后的存储器空间。

8.一种用于从一次性可编程存储器otp测试和修复硬件加速器中的本地存储器的方法,该方法包括:

9.如权利要求8所述的方法,其中,响应于otp定序器电路接收到功能模式复位信号而生成第一授权信号。

10.如权利要求8所述的方法,还包括响应于接收到第一授权信号而指示第一主控制器通过第一修复控制器加载第一修复数据,其中第一修复控制器耦合到第一主控制器和otp定序器电路。

11.如权利要求8所述的方法,还包括响应于接收到第二授权信号而指示第二主控制器通过第二修复控制器加载第二修复数据,其中第二修复控制器耦合到第二主控制器和otp定序器电路。

12.如权利要求8所述的方法,其中,硬件加速器包括图形处理单元(gpu)、现场可编程门阵列(fpga)、专用集成电路(asic)或其组合。

13.如权利要求8所述的方法,其中,硬件加速器用于人工智能或机器学习。

14.如权利要求8所述的方法,还包括在otp存储器中在第一修复数据之后按顺序存储第二修复数据,使得添加到所述地址的偏移指向紧接在第一修复数据之后的存储器空间。

15.一种用于测试和修复硬件加速器中的本地存储器的系统,该系统包括:

16.如权利要求15所述的系统,其中,tcr还被配置为断言访问信号以在测试模式下操作硬件加速器。

17.如权利要求15所述的系统,其中,硬件加速器包括图形处理单元(gpu)、现场可编程门阵列(fpga)、专用集成电路(asic)或其组合。

18.如权利要求15所述的系统,其中,硬件加速器用于人工智能或机器学习。

19.如权利要求15所述的系统,其中,在otp存储器中在第一修复数据之后按顺序存储第二修复数据,使得添加到所述地址的偏移指向紧接在第一修复数据之后的存储器空间。

20.如权利要求15所述的系统,还包括能够耦合到tcr的测试访问点tap,该tap被配置为在硬件加速器的测试模式操作期间控制tcr的操作。

技术总结

本公开涉及增强用于存储器修复机制的区域有效性的通信逻辑。根据实施例,提供了用于从一次性可编程存储器(OTP)测试和修复硬件加速器中的本地存储器的方法。该方法包括断言授权信号、从OTP存储器的第一分区加载用于与主控制器相关联的本地存储器的子集的第一修复数据、在加载完成之后传送指示加载完成的状态信号、以及响应于接收到状态信号而解除断言授权信号。

技术研发人员:U·喀山拜帕特尔,D·H·赛伊德,P·辛格

受保护的技术使用者:意法半导体国际公司

技术研发日:

技术公布日:2024/12/23

- 还没有人留言评论。精彩留言会获得点赞!