本发明涉及一种针对存算一体芯片编程特性的快速编程方法及其装置,属于存算一体架构芯片编程方法领域。

背景技术:

1、神经网络已经成为处理图像识别、分类、优化等任务的核心技术要求,在通用中央处理器或者图像处理器上进行神经网络训练和验证,其中核心的矩阵乘法和加法,依托的是传统的冯诺依曼架构的存储计算分离方式。由于存储单元访问速度和最大能效受限,在数据量较大时会遇到计算速度和芯片功耗的瓶颈。

2、基于此,提出了计算和存储紧密耦合的存算一体架构,能够在很低的功耗下完成大数据量的矩阵乘积累加运算。然而目前存算一体架构芯片普遍存在的问题是编程速度慢。经实际电路测试,存算一体器件的编程电导值随着外部激励会逐渐减小,并且编程特性是非线性的,在电导值较高的编程开始阶段,编程速度较快,电流下降明显。而在编程后期电导值较小时,编程速度会远远低于前期,因此如果采取线性等步长的编程方法,不能很好的利用存算一体器件的编程特性。相反的,根据每次编程的初始值和目标值进行一定的判断和计算,就可以在不同编程阶段给出不同的编程时间,从而更快达到目标值,完成存算一体芯片的全片编程。

3、在中国专利申请cn117032562a中,虽然也提到了将权值与输入时长的不规则曲线分段线性近似,但是在器件编程中每一个权值区间内仍然是等步长的,还是没有做到真正可自定义的编程时间。

技术实现思路

1、针对以上现有技术中存在的问题,本发明提出了一种针对存算一体芯片编程特性的快速编程方法及其装置,能够加快器件的编程速度。

2、本发明采用的技术方案如下:

3、一种针对存算一体芯片的编程方法,包括以下步骤:

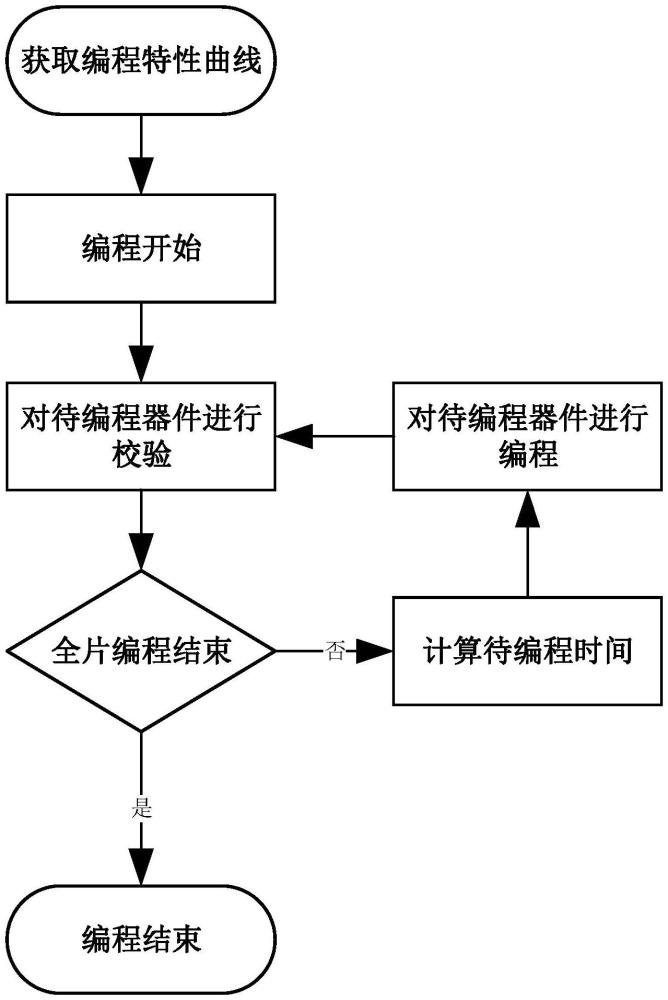

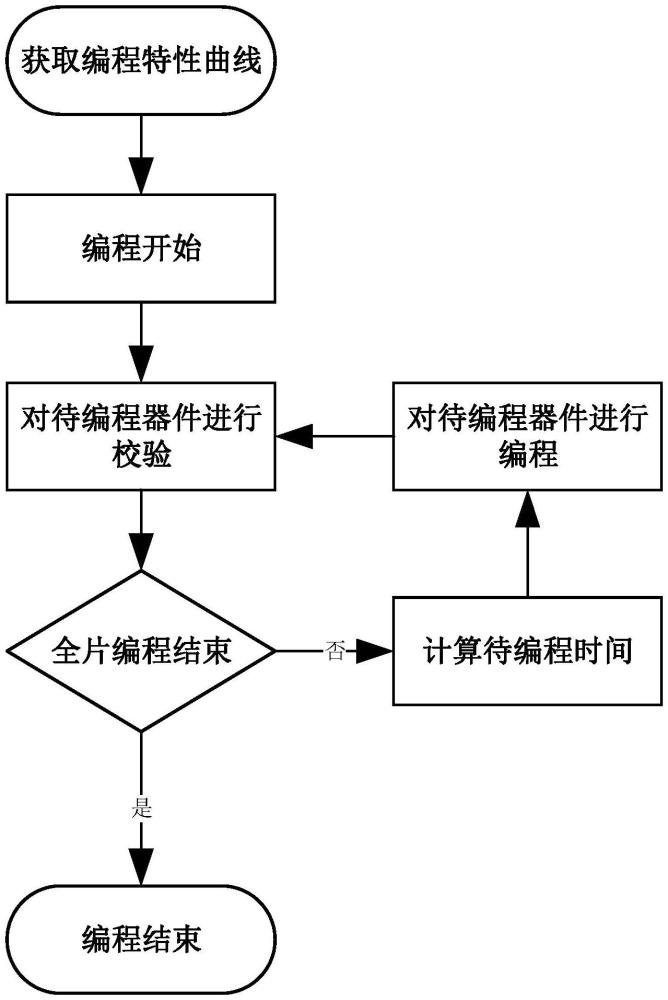

4、步骤1,通过对存算一体芯片的构成器件进行全量程编程,测得器件权值随编程时间的特性曲线,将所述特性曲线按照编程速度相近的区域进行分段处理,得到不同区间权值随编程时间的下降率;

5、步骤2,输入待编程的矩阵,将存算一体芯片的构成器件分为多组,分别对每一组进行多轮的并行编程,即同时编程多个器件:对于每一组器件,在每一轮编程中,首先根据上一轮校验时读出的权值,计算器件待编程值和当前权值之间的差值,并对所述差值通过编程特性查找表得到对应的下降率,基于所述差值和下降率计算出本轮的编程时间,然后开始编程,编程结束后对器件的当前权值进行校验,如果还存在有未完成编程的器件,则开始进行下一轮编程。

6、进一步地,所述步骤1具体为:测得离散的器件权值并进行曲线拟合,将编程速度即曲线下降率相近的区域划分为一个区间,得到多个编程区间。

7、进一步地,所述得到多个编程区间之后,将权值较小和长度较短的区间合并到前一区间,以减少编程区间的数量。

8、进一步地,所述步骤2中,编程时间tprog的计算方式为利用器件待编程值和当前权值之间的差值wdiff除以对应的下降率k,即tprog=wdiff/k。

9、进一步地,所述步骤2中,对于每一组器件,在每一轮编程中同时计算多个权值差的值,并获取对应的下降率,得到所有器件的编程时间后,比较多个编程时间大小,并选取最短的编程时间进行本轮编程。

10、进一步地,所述步骤2中,计算编程时间时以单个器件的编程为参照,即在对每一组器件计算出并行编程所有器件的编程时间并作出编程时间大小比较后,开始编程,当编程完最短编程时间对应的器件并校验完成后,再次计算每一组所有器件的编程时间,如果最短编程时间对应的器件的校验正确,则无需计算该器件的编程时间;重复前述过程,直至所有并行编程器件完成编程和校验。

11、进一步地,所述步骤2中,计算编程时间时以每一组的所有器件为参照,即在计算出并行编程所有器件的编程时间并作出编程时间大小比较后,开始编程,当编程完最短编程时间对应的器件后,不作校验,直接关闭最短编程时间对应器件的选通信号,继续进行下一阶段次短编程时间的编程,编程时间为次短编程时间减去上一阶段编程的时间,重复前述过程,直到所有并行编程器件完成本轮编程,再进行校验。

12、本发明还提供一种针对存算一体芯片的编程装置,其包括光输入驱动模块、光校验模块、编程时间控制模块和光输入顶层控制模块,其中,光输入顶层控制模块用于将待编程矩阵信息传输给光校验模块和编程时间控制模块,将模式切换信号传输给光输入驱动模块和光校验模块,并接收光输入驱动模块的光输入结束信号以及光校验模块的比较正确和错误信号;编程时间控制模块用于根据待编程器件权值、当前器件读出权值以及光校验模块的比较正确和错误信号计算编程时间,并传输给光输入驱动模块;光输入驱动模块用于接收光校验模块的比较正确和错误信号以切换内部工作状态,并给出当前编程行列信息到光校验模块;光校验模块用于对接收到的行列信号和当前器件读出权值对对应器件的权值进行校验,并输出比较正确和错误信号。

13、进一步地,所述编程时间控制模块中,使用寄存器或者存储器存储器件权值随编程时间的特性曲线。

14、进一步地,所述编程时间控制模块还输出一个标识编程时间有效的标志位给光输入驱动模块,光输入驱动模块检测到此标志位时进入编程状态。

15、本发明的优点包括:利用了存算一体器件自身的编程特性,不再采用固定步长编程,而是根据实际编程值来动态调整每次编程的时间,并且此技术可以应用到多个器件的并行编程上。此方法可以在编程前期起到较大加速作用,并且在接近目标权值时会转为最小步长编程,即不会出现过编程较多的问题。相比于现有的传统的等间隔编程方式,非线性编程的方式有很大优势,并且可以和其他加速方法一并使用。本发明方法能够加快器件的编程速度,加速比在不同编程权值下可以达到2.7~31.6倍。

技术特征:1.一种针对存算一体芯片的编程方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种针对存算一体芯片的编程方法,其特征在于,所述步骤1具体为:测得离散的器件权值并进行曲线拟合,将编程速度即曲线下降率相近的区域划分为一个区间,得到多个编程区间。

3.根据权利要求2所述的一种针对存算一体芯片的编程方法,其特征在于,所述得到多个编程区间之后,将权值较小和长度较短的区间合并到前一区间,以减少编程区间的数量。

4.根据权利要求1所述的一种针对存算一体芯片的编程方法,其特征在于,所述步骤2中,编程时间tprog的计算方式为利用器件待编程值和当前权值之间的差值wdiff除以对应的下降率k,即tprog=wdiff/k。

5.根据权利要求1所述的一种针对存算一体芯片的编程方法,其特征在于,所述步骤2中,对于每一组器件,在每一轮编程中同时计算多个权值差的值,并获取对应的下降率,得到所有器件的编程时间后,比较多个编程时间大小,并选取最短的编程时间进行本轮编程。

6.根据权利要求5所述的一种针对存算一体芯片的编程方法,其特征在于,所述步骤2中,计算编程时间时以单个器件的编程为参照,即在对每一组器件计算出并行编程所有器件的编程时间并作出编程时间大小比较后,开始编程,当编程完最短编程时间对应的器件并校验完成后,再次计算每一组所有器件的编程时间,如果最短编程时间对应的器件的校验正确,则无需计算该器件的编程时间;重复前述过程,直至所有并行编程器件完成编程和校验。

7.根据权利要求5所述的一种针对存算一体芯片的编程方法,其特征在于,所述步骤2中,计算编程时间时以每一组的所有器件为参照,即在计算出并行编程所有器件的编程时间并作出编程时间大小比较后,开始编程,当编程完最短编程时间对应的器件后,不作校验,直接关闭最短编程时间对应器件的选通信号,继续进行下一阶段次短编程时间的编程,编程时间为次短编程时间减去上一阶段编程的时间,重复前述过程,直到所有并行编程器件完成本轮编程,再进行校验。

8.一种针对存算一体芯片的编程装置,其特征在于,包括光输入驱动模块、光校验模块、编程时间控制模块和光输入顶层控制模块,其中,

9.根据权利要求8所述的一种针对存算一体芯片的编程装置,其特征在于,所述编程时间控制模块中,使用寄存器或者存储器存储器件权值随编程时间的特性曲线。

10.根据权利要求8所述的一种针对存算一体芯片的编程装置,其特征在于,所述编程时间控制模块还输出一个标识编程时间有效的标志位给光输入驱动模块,光输入驱动模块检测到此标志位时进入编程状态。

技术总结本发明公开了一种针对存算一体芯片的编程方法及其装置。该方法包括以下步骤:步骤1,通过对存算一体芯片的构成器件进行全量程编程,测得器件权值随编程时间的特性曲线;步骤2,输入待编程的矩阵,将存算一体芯片的构成器件分为多组,分别对每一组进行多轮的并行编程:在每一轮编程中,首先根据上一轮校验时读出的权值,计算器件待编程值和当前权值之间的差值,并对差值通过编程特性查找表得到对应的下降率,基于差值和下降率计算出本轮的编程时间,然后开始编程,编程结束后对器件的当前权值进行校验,如果还存在有未完成编程的器件,则开始进行下一轮编程。本发明可以极大提高存算一体芯片的编程速度。

技术研发人员:王宇宣,王悬济,郝晨君,孙晓磊,潘红兵,彭成磊

受保护的技术使用者:南京大学

技术研发日:技术公布日:2024/11/28