存储阵列、存储器以及电子设备的制作方法

本申请涉及存储,尤其涉及存储阵列、存储器以及电子设备。

背景技术:

1、磁性随机存储器(magnetic random access memory,mram)由于具有非易失性、抗辐照、低功耗等优点,引起了学术与工业领域极大的关注。磁性隧道结(magnetic tunneljunction,mtj)是磁性随机存储器mram的基本存储单元。

2、传统的存储阵列中的存储单元结构包括两个选通晶体管和一个sot-mram器件。其中,sot-mram为自旋轨道转矩磁性存储器,英文全称为spin-orbit torque mram。sot-mram一般包括磁隧道结,以及与磁隧道结的自由层相邻近的自旋轨道矩层(又称sot层),故存储阵列难以提高集成密度。

3、目前,为了提高存储密度,一些阵列使用由单个选通晶体管和sot-mram存储器件构成的存储单元。该结构的存储单元中的晶体管位于单元自旋轨道矩层的位线上,用于控制写入电流。这一结构通过削减mtj顶电极晶体管的方式,提高了阵列的面积效率。但是,当阵列规模持续增大,由于存储单元缺少了一个选通晶体管,阵列的行/列间电流干扰会严重影响电路读取的准确性。

技术实现思路

1、本申请提供一种存储阵列、存储器以及电子设备,用以提供一种提高阵列面积效率的同时减小大规模阵列中存在的行间电流干扰的技术方案。

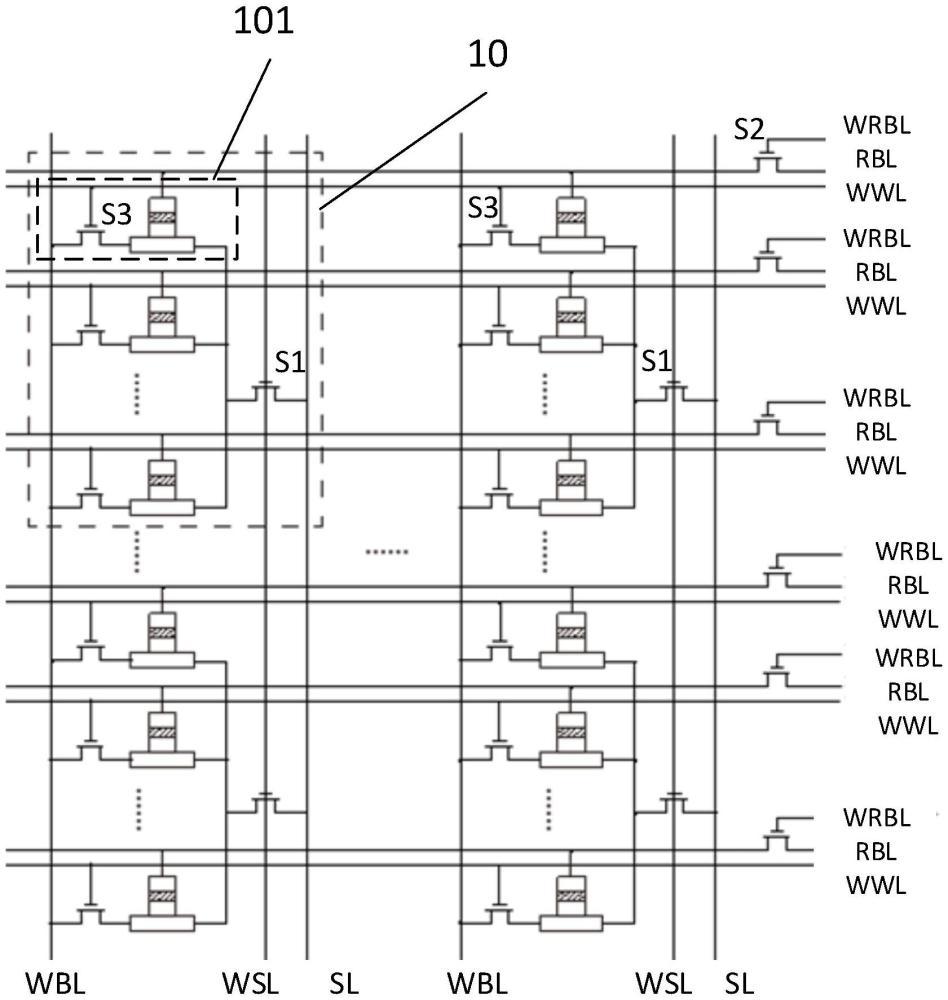

2、第一方面,本申请提供一种存储阵列,包括:若干矩阵式排布的存储单元;

3、每列所述存储阵列均包括至少一个存储单元组,所述存储单元组包括多个存储单元和第一开关管,每个所述存储单元包括存储器件;

4、每行所述存储阵列包括第二开关管;

5、所述第一开关管的三端分别连接对应组中所述存储器件的自旋轨道矩层、对应的列公用源线及对应的列选通信号线;

6、所述第二开关管的三端分别连接对应行中所述存储器件的磁隧道结、对应的读位线及对应的行读取选通信号线;

7、数据读取时,通过所述对应的行读取选通信号线中的信号选通所述第二开关管,通过所述对应的列选通信号线中的信号选通所述第一开关管,所述存储器件用于在同时打开对应所述第一开关管和对应所述第二开关管的情况下,通过所述对应的读位线读出对应的存储器件中的数据。

8、在一种可选的实施方式中,每个所述存储单元还包括第三开关管,所述第三开关管的三端分别连接对应的写位线、对应所述存储器件的第一端及对应的行写字线;

9、数据写入时,通过所述对应的行写字线中的信号选通所述第三开关管,通过所述对应的列选通信号线中的信号选通所述第一开关管,所述存储器件用于在对应所述第三开关管和对应所述第一开关管打开的情况下,通过所述对应的写位线和所述对应的列公用源线向对应的存储器件中写入数据。

10、在一种可选的实施方式中,在数据读取阶段,所述存储单元组中的多个存储单元累积到所述读位线上的干扰电压小于或等于预设干扰电压。

11、在一种可选的实施方式中,所述预设干扰电压为所述读位线可承受的最大干扰电压。

12、在一种可选的实施方式中,所述存储器件为自旋轨道转矩磁性存储器;所述自旋轨道转矩磁性存储器至少包括磁隧道结和自旋轨道矩层;所述磁隧道结至少包括依次叠置的自由层、势垒层和参考层,所述自由层邻近所述自旋轨道矩层。

13、第二方面,本申请提供一种存储器,所述存储器包括行地址译码模块、列地址译码模块、读取模块、列公用源线、列选通信号线、读位线、行读取选通信号线以及第一方面所述的存储阵列。

14、所述列地址译码模块通过所述对应的列选通信号线与所述第一开关管的控制端连接,所述行地址译码模块通过所述对应的行读取选通信号线与所述第二开关管的控制端连接;所述读取模块通过所述对应的读位线与所述第二开关管的第一端连接,所述第二开关管的第二端与对应行中所述存储器件的磁隧道结连接。

15、数据读取时,所述行地址译码模块通过所述对应的行读取选通信号线中的信号选通所述第二开关管,所述列地址译码模块通过所述对应的列选通信号线中的信号选通所述第一开关管,所述读取模块用于在同时打开所述第一开关管和所述第二开关管的情况下,通过所述对应的读位线读出所述存储器中的数据。

16、在一种可选的实施方式中,所述存储器还包括写入模块,写位线、以及行写字线;每个所述存储单元还包括第三开关管,所述第三开关管的三端分别连接对应的写位线、对应所述存储器件的第一端及对应的行写字线。

17、所述写入模块通过所述对应的写位线以及所述第三晶体管与所述存储器件连接;所述行地址译码模块通过所述对应的行写字线与所述第三晶体管的控制端连接。

18、数据写入时,所述行地址译码模块通过所述对应的行写字线中的信号选通所述第三开关管,列地址译码模块通过所述对应的列选通信号线中的信号选通所述第一开关管,所述写入模块用于在对应所述第三开关管和对应所述第一开关管打开的情况下,通过所述对应的写位线和所述对应的列公用源线向所述存储器件中写入数据。

19、在一种可选的实施方式中,所述列地址译码器用于根据地址信号生成列选通信号,所述列选通信号为所述对应的列选通信号线中的信号。

20、所述行地址译码器用于根据所述地址信号生成行写字信号,所述行写字信号为所述对应的行写字线中的信号。

21、所述行地址译码器还用于根据所述地址信号生成行读取选通信号,所述行读取选通信号为所述对应的行读取选通信号线中的信号。

22、在一种可选的实施方式中,所述存储单元组中的多个存储单元累积到对应所述读位线上的干扰电压小于或等于预设干扰电压。

23、第三方面,本申请提供一种电子设备,包括第二方面所述的存储器。

24、本申请提供的技术方案,在数据读取时,通过对应的行读取选通信号线中的信号选通需要打开的第二开关管,通过对应的列选通信号线中的信号选通需要打开的第一开关管,相当于在每次读取操作时,开启了存储器件所在行和所在列的第一开关管和第二开关管。而在本申请中,将每列所述存储阵列中的多个存储单元划分为至少一个存储单元组,每个存储单元组对应设置一个第一开关管,基于此,可以减少每列存储单元中的第一开关管的数量,进而减小了阵列中的行/列电流干扰。

25、且本申请将每列所述存储阵列中的多个存储单元划分为至少一个存储单元组,每个存储单元组对应设置一个第一开关管,可以削减传统存储阵列中开关管的数量,提高了存储阵列的面积效率。

26、故本申请能够在减少存储单元中开关管数量以提高面积效率的同时,减小了大规模阵列中存在的行/列电流干扰,保证了数据读取的准确性。

技术特征:

1.一种存储阵列,其特征在于,包括:若干矩阵式排布的存储单元;

2.根据权利要求1所述的存储阵列,其特征在于,每个所述存储单元还包括第三开关管,所述第三开关管的三端分别连接对应的写位线、对应所述存储器件的自旋轨道矩层及对应的行写字线;

3.根据权利要求1所述的存储阵列,其特征在于,在数据读取阶段,所述存储单元组中的多个存储单元累积到对应所述读位线上的干扰电压小于或等于预设干扰电压。

4.根据权利要求3所述的存储阵列,其特征在于,所述预设干扰电压为对应所述读位线可承受的最大干扰电压。

5.根据权利要求1-4任一项所述的存储阵列,其特征在于,所述存储器件为自旋轨道转矩磁性存储器;

6.一种存储器,其特征在于,所述存储器包括行地址译码模块、列地址译码模块、读取模块、列公用源线、列选通信号线、读位线、行读取选通信号线以及权利要求1-5任一项所述的存储阵列;

7.根据权利要求6所述的存储器,其特征在于,所述存储器还包括写入模块,写位线、以及行写字线;

8.根据权利要求7所述的存储器,其特征在于,所述列地址译码器用于根据地址信号生成列选通信号,所述列选通信号为所述对应的列选通信号线中的信号;

9.根据权利要求7所述的存储器,其特征在于,在数据读取阶段,所述存储单元组中的多个存储单元累积到对应所述读位线上的干扰电压小于或等于预设干扰电压。

10.一种电子设备,包括权利要求6-9中任一项所述的存储器。

技术总结

本申请提供了一种存储阵列、存储器以及电子设备,涉及存储技术领域,包括:若干矩阵式排布的存储单元;每列所述存储阵列均包括至少一个存储单元组,所述存储单元组包括多个存储单元和第一开关管,每个所述存储单元包括存储器件;每行所述存储阵列包括第二开关管;所述第一开关管的三端分别连接对应组中所述存储器件的自旋轨道矩层、对应的列公用源线及对应的列选通信号线;所述第二开关管的三端分别连接对应行中所述存储器件的磁隧道结、对应的读位线及对应的行读取选通信号线;本申请能够在减少存储单元中开关管数量以提高面积效率的同时,减小了大规模阵列中存在的行/列电流干扰,保证了读取操作的准确性。

技术研发人员:张和,黄炜亮,王戈飞

受保护的技术使用者:致真存储(北京)科技有限公司

技术研发日:

技术公布日:2024/11/18

- 还没有人留言评论。精彩留言会获得点赞!