SRAM增强型测试方法、装置、计算机设备及存储介质与流程

本发明涉及数据存储,更具体地说是sram增强型测试方法、装置、计算机设备及存储介质。

背景技术:

1、ssd-solid state drives(固态硬盘)soc芯片,一般采用传统的sram测试方法,使用专门的测试设备通过jtag接口进行mbist测试,这在芯片的晶圆和封装阶段(cp/ft)都能进行,然而,到了产品化阶段(slt),环境的变化(如电压和温度)可能导致一些内存问题,这些问题在cp/ft阶段可能并未被发现。这种情况下,无法明确这些问题是否是由于memory本身的良率导致的,也无法指导后续的芯片量产测试是否需要加严测试标准。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供sram增强型测试方法、装置、计算机设备及存储介质。

2、为实现上述目的,本发明采用以下技术方案:

3、第一方面,本发明提供了sram增强型测试方法,包括:

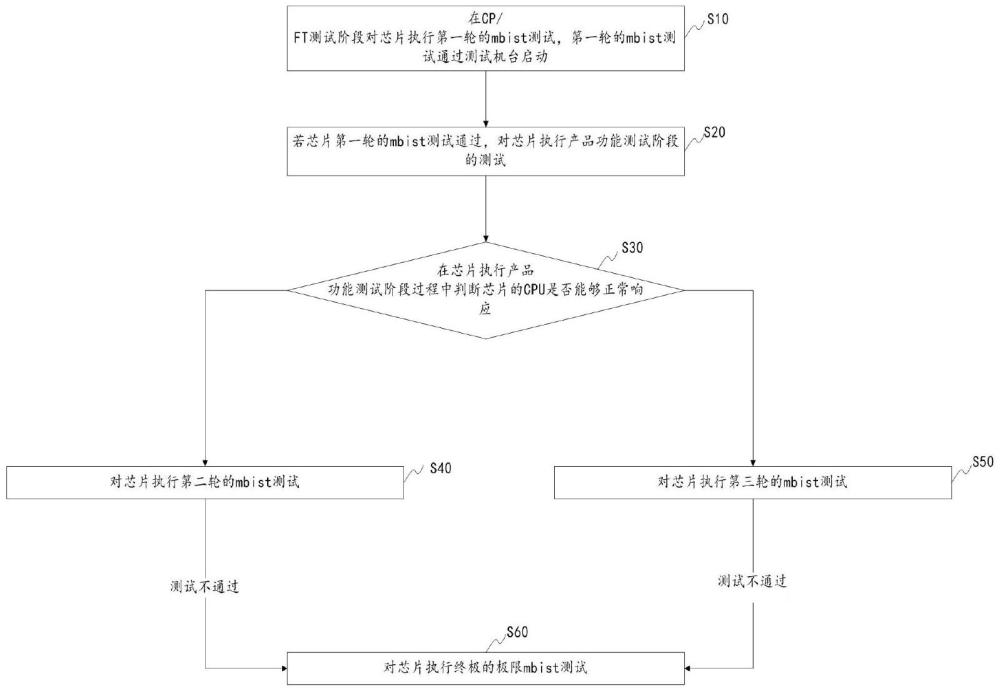

4、在cp/ft测试阶段对芯片执行第一轮的mbist测试,第一轮的mbist测试通过测试机台启动;

5、若芯片第一轮的mbist测试通过,对芯片执行产品功能测试阶段的测试;

6、在芯片执行产品功能测试阶段过程中判断芯片的cpu是否能够正常响应;

7、若cpu能够正常响应,则对芯片执行第二轮的mbist测试;

8、若芯片第二轮的mbist测试不通过,则对芯片执行终极的极限mbist测试;

9、若cpu不能够正常响应,则对芯片执行第三轮的mbist测试,若芯片第三轮的mbist测试不通过,则对芯片执行终极的极限mbist测试。

10、进一步地,所述对芯片执行第二轮的mbist测试,包括:

11、利用cpu初始化控制寄存器和状态寄存器;

12、设定循环测试次数;

13、利用cpu控制初始化后的控制寄存器按照设定的循环测试次数执行mbist测试,并将测试结果写入状态寄存器;

14、cpu读取状态寄存器,以判断测试是否通过。

15、进一步地,所述对芯片执行第三轮的mbist测试,包括:

16、启动拨码开关;

17、通过拨码开关直接开启mbist测试功能。

18、进一步地,所述对芯片执行终极的极限mbist测试,包括:

19、标记芯片为疑似坏片;

20、将疑似坏片断电,静置一段时间;

21、在静置一段时间后,重新上电,并进入mbist测试;

22、若测试通过,则逐步增加测试通过的困难程度,直至测试不通过为止。

23、第二方面,本发明还提供了sram增强型测试装置,包括:

24、第一测试单元,用于在cp/ft测试阶段对芯片执行第一轮的mbist测试,第一轮的mbist测试通过测试机台启动;

25、第二测试单元,用于若芯片第一轮的mbist测试通过,对芯片执行产品功能测试阶段的测试;

26、判断单元,用于在芯片执行产品功能测试阶段过程中判断芯片的cpu是否能够正常响应;

27、第三测试单元,用于若cpu能够正常响应,则对芯片执行第二轮的mbist测试;

28、第四测试单元,用于若芯片第二轮的mbist测试不通过,则对芯片执行终极的极限mbist测试;

29、第五测试单元,用于若cpu不能够正常响应,则对芯片执行第三轮的mbist测试,若芯片第三轮的mbist测试不通过,则对芯片执行终极的极限mbist测试。

30、进一步地,所述第三测试单元包括:

31、初始化模块,用于利用cpu初始化控制寄存器和状态寄存器;

32、设定模块,用于设定循环测试次数;

33、第一测试模块,用于利用cpu控制初始化后的控制寄存器按照设定的循环测试次数执行mbist测试,并将测试结果写入状态寄存器;

34、读取模块,用于cpu读取状态寄存器,以判断测试是否通过。

35、进一步地,所述第四测试单元包括:

36、标记模块,用于标记芯片为疑似坏片;

37、断电静置模块,用于将疑似坏片断电,静置一段时间;

38、重新上电模块,用于在静置一段时间后,重新上电,并进入mbist测试;

39、逐步测试模块,用于若测试通过,则逐步增加测试通过的困难程度,直至测试不通过为止。

40、进一步地,所述第五测试单元包括:

41、启动模块,用于启动拨码开关;

42、直接测试模块,用于通过拨码开关直接开启mbist测试功能。

43、第三方面,本发明还提供了一种计算机设备,包括存储器、处理器以及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如上述的sram增强型测试方法。

44、第四方面,本发明还提供了一种计算机可读存储介质,所述存储介质存储有计算机程序,所述计算机程序包括程序指令,所述程序指令被处理器执行时,使得所述处理器执行如上述的sram增强型测试方法。

45、本发明与现有技术相比的有益效果是:sram增强型测试方法,包括:在cp/ft测试阶段对芯片执行第一轮的mbist测试,第一轮的mbist测试通过测试机台启动;若芯片第一轮的mbist测试通过,对芯片执行产品功能测试阶段的测试;在芯片执行产品功能测试阶段过程中判断芯片的cpu是否能够正常响应;若cpu能够正常响应,则对芯片执行第二轮的mbist测试;若芯片第二轮的mbist测试不通过,则对芯片执行终极的极限mbist测试;若cpu不能够正常响应,则对芯片执行第三轮的mbist测试,若芯片第三轮的mbist测试不通过,则对芯片执行终极的极限mbist测试。本发明通过在实际系统环境中多种方式启动mbist测试,不依赖机台,从而提高了产品的可靠性,并指导后续的量产测试标准。

46、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明技术手段,可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的特征及优点能够更明显易懂,以下特举较佳实施例,详细说明如下。

技术特征:

1.sram增强型测试方法,其特征在于,包括:

2.根据权利要求1所述的sram增强型测试方法,其特征在于,所述对芯片执行第二轮的mbist测试,包括:

3.根据权利要求1所述的sram增强型测试方法,其特征在于,所述对芯片执行第三轮的mbist测试,包括:

4.根据权利要求1所述的sram增强型测试方法,其特征在于,所述对芯片执行终极的极限mbist测试,包括:

5.sram增强型测试装置,其特征在于,包括:

6.根据权利要求5所述的sram增强型测试装置,其特征在于,所述第三测试单元包括:

7.根据权利要求5所述的sram增强型测试装置,其特征在于,所述第四测试单元包括:

8.根据权利要求5所述的sram增强型测试装置,其特征在于,所述第五测试单元包括:

9.一种计算机设备,其特征在于,包括存储器、处理器以及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如权利要求1~4中任意一项所述的sram增强型测试方法。

10.一种计算机可读存储介质,其特征在于,所述存储介质存储有计算机程序,所述计算机程序包括程序指令,所述程序指令被处理器执行时,使得所述处理器执行如权利要求1~4任意一项所述的sram增强型测试方法。

技术总结

本发明公开了SRAM增强型测试方法、装置、计算机设备及存储介质,方法包括:在CP/FT测试阶段对芯片执行第一轮的mbist测试,第一轮的mbist测试通过测试机台启动;若芯片第一轮的mbist测试通过,对芯片执行产品功能测试阶段的测试;在芯片执行产品功能测试阶段过程中判断芯片的CPU是否能够正常响应;若CPU能够正常响应,则对芯片执行第二轮的mbist测试;若芯片第二轮的mbist测试不通过,则对芯片执行终极的极限mbist测试;若CPU不能够正常响应,则对芯片执行第三轮的mbist测试,若芯片第三轮的mbist测试不通过,则对芯片执行终极的极限mbist测试。本发明通过在实际系统环境中多种方式启动mbist测试,不依赖机台,从而提高了产品的可靠性,并指导后续的量产测试标准。

技术研发人员:李湘锦,王永亮

受保护的技术使用者:苏州忆联信息系统有限公司

技术研发日:

技术公布日:2024/12/30

- 还没有人留言评论。精彩留言会获得点赞!