经编译的多端口存储器的制作方法

本公开总体上涉及存储器架构,并且更具体地涉及多端口存储器。

背景技术:

1、存储器在诸如智能手机和计算机等电子设备中起着重要作用。在一些实现中,可以使用多端口存储器设备,该设备允许对存储器单元的多于一个访问端口。例如,多端口存储器可以包括用于存储器单元的多个读取端口和多个写入端口。系统的不同电路可以使用读取端口来执行来自存储器单元的同时读取操作。

技术实现思路

1、以下给出了本公开的一个或多个方面的简化概述,以便提供对这样的方面的基本理解。本概述不是对本公开的所有预期特征的广泛概述,既不旨在标识本公开的所有方面的关键或重要元素,也不旨在界定本公开的任何或所有方面的范围。其唯一目的是以简化形式呈现本公开的一个或多个方面的一些概念,作为稍后呈现的更详细描述的前奏。

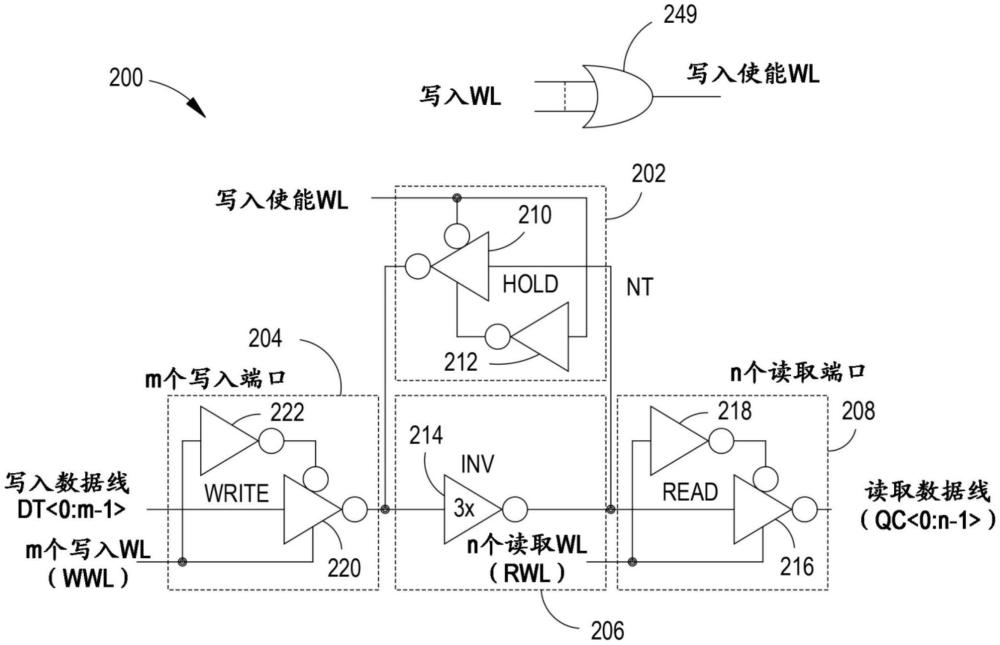

2、本公开的某些方面涉及多端口存储器单元。该多端口存储器单元可以包括:反相器电路单元;具有耦合到反相器电路单元的输入的输出和耦合到反相器电路单元的输出的输入的保持电路单元;以及具有相应三态驱动器的多个单位电路单元,其中多个单位电路单元中的第一多个单位电路单元被配置为具有耦合到反相器电路单元的输出的输入的读取电路单元,并且多个单位电路单元中的第二多个单位电路单元被配置为具有耦合到反相器电路单元的输入的输出的写入电路单元。

3、本公开的某些方面涉及用于多端口存储器单元处理的方法。该方法总体上包括:通过将多个单位电路单元中的第一多个单位电路单元的输入耦合到反相器电路单元的输出,将多个单位电路单元中的第一多个单位电路单元配置为读取电路单元,多个单位电路单元包括相应三态驱动器;以及通过将多个单位电路单元中的第二多个单位电路单元的输出耦合到反相器电路单元的输入,将多个单位电路单元中的第二多个单位电路单元配置为写入单元,其中保持电路单元的输出耦合到反相器电路单元的输入,并且保持电路单元的输入耦合到反相器电路单元的输出。

4、本公开的某些方面涉及用于多端口存储器单元处理的装置。该装置总体上包括存储器;以及耦合到存储器的一个或多个处理器,该一个或多个处理器被配置为:通过将多个单位电路单元中的第一多个单位电路单元的输入耦合到反相器电路单元的输出,将多个单位电路单元中的第一多个单位电路单元配置为读取电路单元,多个单位电路单元具有相应三态驱动器;以及通过将多个单位电路单元中的第二多个单位电路单元的输出耦合到反相器电路单元的输入,将多个单位电路单元中的第二多个单位电路单元配置为写入单元,其中保持电路单元的输出耦合到反相器电路单元的输入并且保持电路单元的输入耦合到反相器电路单元的输出。

技术特征:

1.一种多端口存储器单元,包括:

2.根据权利要求1所述的多端口存储器单元,其中所述保持电路单元包括三态驱动器。

3.根据权利要求2所述的多端口存储器单元,其中当所述写入电路单元中的一者被启用时,所述保持电路单元的所述三态驱动器被禁用。

4.根据权利要求2所述的多端口存储器单元,其中所述保持电路单元还包括反相器,所述反相器耦合在所述保持电路单元的所述三态驱动器的使能输入与互补使能输入之间。

5.根据权利要求1所述的多端口存储器单元,其中所述多个单位电路单元中的每一者包括反相器,所述反相器耦合在所述三态驱动器中的相应一者的使能输入与互补使能输入之间。

6.根据权利要求1所述的多端口存储器单元,还包括:

7.根据权利要求6所述的多端口存储器单元,其中通过将所述第一节点耦合到所述多个单位电路单元中的所述第一多个单位电路单元的所述三态驱动器的输入,所述多个单位电路单元中的所述第一多个单位电路单元被配置为读取单元。

8.根据权利要求6所述的多端口存储器单元,其中通过将所述第二节点耦合到所述多个单位电路单元中的所述第二多个单位电路单元的所述三态驱动器的输出,所述多个单位电路单元中的所述第二多个单位电路单元被配置为写入单元。

9.根据权利要求1所述的多端口存储器单元,其中通过将读取数据线耦合到所述多个单位电路单元中的所述第一多个单位电路单元的所述三态驱动器中的每一者的输出,所述多个单位电路单元中的所述第一多个单位电路单元被配置为读取单元。

10.根据权利要求1所述的多端口存储器单元,其中通过将写入数据线耦合到所述多个单位电路单元中的所述第二多个单位电路单元的所述三态驱动器中的每一者的输入,所述多个单位电路单元中的所述第二多个单位电路单元被配置为写入电路单元。

11.根据权利要求1所述的多端口存储器单元,其中通过将字线耦合到所述多个单位电路单元中的所述第二多个单位电路单元的所述三态驱动器的相应使能输入,所述多个单位电路单元中的所述第二多个单位电路单元被配置为写入单元。

12.根据权利要求11所述的多端口存储器单元,还包括or门,其中所述字线还耦合到所述or门的输入,并且其中所述or门的输出耦合到所述保持电路单元的使能输入。

13.一种用于多端口存储器单元处理的方法,包括:

14.根据权利要求13所述的方法,其中所述保持电路单元包括三态驱动器。

15.根据权利要求14所述的方法,还包括将所述保持电路单元的所述三态驱动器配置为基于所述写入单元中的一者被启用而被禁用。

16.根据权利要求13所述的方法,其中:

17.根据权利要求13所述的方法,其中将所述多个单位电路单元中的所述第一多个单位电路单元配置为读取电路单元包括:将读取数据线耦合到所述多个单位电路单元中的所述第一多个单位电路单元的所述三态驱动器中的每一者的输出。

18.根据权利要求13所述的方法,其中将所述多个单位电路单元中的所述第二多个单位电路单元配置为写入电路单元包括:将写入数据线耦合到所述多个单位电路单元中的所述第二多个单位电路单元的所述三态驱动器中的每一者的输入。

19.根据权利要求13所述的方法,其中:

20.一种用于多端口存储器单元处理的装置,包括:

技术总结

本公开涉及经编译的多端口存储器,某些方面涉及一种多端口存储器单元。该多端口存储器单元可以包括:反相器电路单元;具有耦合到反相器电路单元的输入的输出和耦合到反相器电路单元的输出的输入的保持电路单元;以及具有相应三态驱动器的多个单位电路单元,其中多个单位电路单元中的第一多个单位电路单元被配置为读取电路单元,读取电路单元具有耦合到反相器电路单元的输出的输入,并且多个单位电路单元中的第二多个单位电路单元被配置为写入电路单元,写入电路单元具有耦合到反相器电路单元的输入的输出。

技术研发人员:J·E·巴思

受保护的技术使用者:美商新思科技有限公司

技术研发日:

技术公布日:2025/4/14

- 还没有人留言评论。精彩留言会获得点赞!