一种存储器的适配能力测试装置的制作方法

本技术属于服务器,具体涉及一种存储器的适配能力测试装置。

背景技术:

1、存储器根据断电后是否保留存储的信息可分为易失性存储器和非易失性存储器,其中只读存储器(rom)是主要的非易失性存储器,其特点是一旦在其体内存储了资料就无法再被改写或删除,但其存储过的内容也不会因为电源关闭而丢失。

2、作为一种电可擦除可编程只读存储器,flash存储器不但能进行擦除和编程操作,具有非易失性的同时还可以快速读取数据。目前占据主流市场的flash存储器分为norflash和nand flash,nor flash的读取速度较快,常用于存储系统固件、引导程序和操作系统,nand flash的写入速度较快,常用于存储大量数据,如图像、音频和视频文件。

3、在服务器领域,nor flash通常用于存储主控芯片的启动代码,初始化相关的硬件配置,实现相应的功能逻辑,因此,主控芯片需要与nor flash进行适配,方可正常使用。通常,芯片厂商会在avl清单中列出芯片所适配的flash型号,然而实际使用过程中,avl清单中的nor flash可能存在eol或是交期跳票的情况,这时需要我们自行对主控芯片的norflash进行适配。面对不同封装、不同厂商的各种nor flash,通常采用飞线的方式,将主控板的spi总线连接到待适配nor flash上,若适配失败需要重新飞线,费时费力,效果不理想,而且需要在板卡上进行多处飞线操作,操作不当容易造成板卡短路,烧坏板卡。

技术实现思路

1、针对现有技术的上述不足,本实用新型提供一种存储器的适配能力测试装置,以解决上述技术问题。

2、本实用新型提供一种存储器的适配能力测试装置,包括:

3、存储器插槽,所述存储器插槽用于搭载待测存储器;所述存储器插槽搭载的待测存储器通过二选一开关芯片分别连接主控芯片和bmc,所述bmc连接所述二选一开关芯片的控制端口;所述主控芯片的io接口连接bmc;所述bmc通过i2c线路连接复杂可编程逻辑器件;所述存储器插槽连接供电电源,且所述存储器插槽与供电电源之间串联有供电开关。

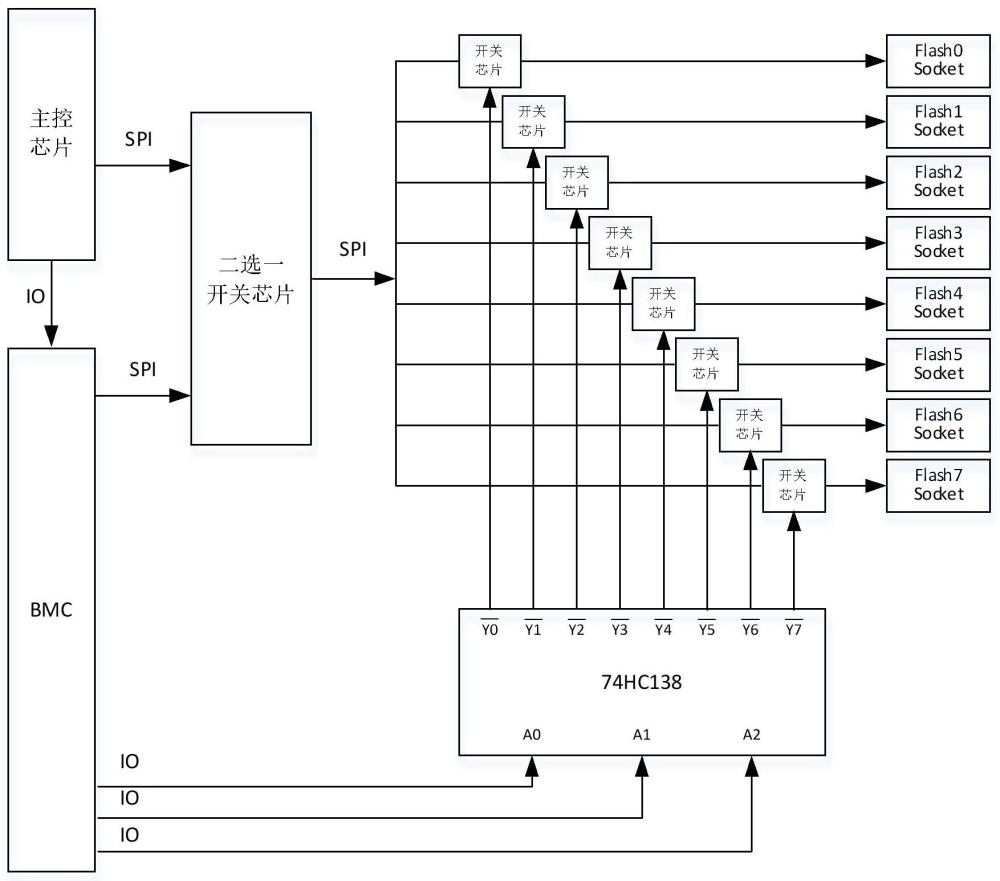

4、在一个可选的实施方式中,包括多个存储器插槽,多个所述存储器插槽搭载多个存储器,多个所述存储器的spi总线端口均连接二选一开关芯片的输出端,二选一开关芯片的一个输入端连接主控芯片的spi接口,二选一开关芯片的另一个输入端连接bmc的spi接口。

5、在一个可选的实施方式中,bmc通过同步串行信号线连接二选一开关芯片的第一输入端,主控芯片通过同步串行信号线连接二选一开关芯片的第二输入端,二选一开关芯片的输出端通过同步串行信号线连接多个存储器插槽。

6、在一个可选的实施方式中,所述存储器插槽通过第一线路连接第一供电电源,所述存储器插槽通过第二线路连接第二供电电源,第一线路上串联有第一插针开关,第二线路上串联有第二插针开关。

7、在一个可选的实施方式中,所述第一供电电源为3.3v电源,所述第二供电电源为1.8v电源。

8、在一个可选的实施方式中,所述bmc通过i2c线路连接辅助芯片,所述辅助芯片的io引脚连接存储器插槽的电源接口。

9、在一个可选的实施方式中,所述辅助芯片电连接led灯。

10、在一个可选的实施方式中,所述辅助芯片采用ca9555芯片。

11、在一个可选的实施方式中,所述bmc通过三个io引脚连接目标选择芯片。

12、在一个可选的实施方式中,二选一开关芯片的多条与待测存储器相连接的输出端支路上,均设有开关芯片;所述目标选择芯片的多个引脚分别连接对应的开关芯片的控制端

13、本实用新型的有益效果在于,本实用新型提供的存储器的适配能力测试装置,通过构建bmc、主控芯片、目标选择芯片和待测存储器之间的连接拓扑,针对flash芯片擦写失败导致与主控芯片适配失败的情况加以区分,排除此种情况下flash型号与主控芯片不适配的结果,提高了检测的可靠性。

14、此外,本实用新型设计原理可靠,结构简单,具有非常广泛的应用前景。

技术特征:

1.一种存储器的适配能力测试装置,其特征在于,包括:

2.根据权利要求1所述的存储器的适配能力测试装置,其特征在于,包括多个存储器插槽,多个所述存储器插槽搭载多个存储器,多个所述存储器的spi总线端口均连接二选一开关芯片的输出端,二选一开关芯片的一个输入端连接主控芯片的spi接口,二选一开关芯片的另一个输入端连接bmc的spi接口。

3.根据权利要求2所述的存储器的适配能力测试装置,其特征在于,bmc通过同步串行信号线连接二选一开关芯片的第一输入端,主控芯片通过同步串行信号线连接二选一开关芯片的第二输入端,二选一开关芯片的输出端通过同步串行信号线连接多个存储器插槽。

4.根据权利要求1所述的存储器的适配能力测试装置,其特征在于,所述存储器插槽通过第一线路连接第一供电电源,所述存储器插槽通过第二线路连接第二供电电源,第一线路上串联有第一插针开关,第二线路上串联有第二插针开关。

5.根据权利要求4所述的存储器的适配能力测试装置,其特征在于,所述第一供电电源为3.3v电源,所述第二供电电源为1.8v电源。

6.根据权利要求1所述的存储器的适配能力测试装置,其特征在于,所述bmc通过i2c线路连接辅助芯片,所述辅助芯片的io引脚连接存储器插槽的电源接口。

7.根据权利要求6所述的存储器的适配能力测试装置,其特征在于,所述辅助芯片电连接led灯。

8.根据权利要求7所述的存储器的适配能力测试装置,其特征在于,所述辅助芯片采用ca9555芯片。

9.根据权利要求2所述的存储器的适配能力测试装置,其特征在于,所述bmc通过三个io引脚连接目标选择芯片。

10.根据权利要求9所述的存储器的适配能力测试装置,其特征在于,二选一开关芯片的多条与待测存储器相连接的输出端支路上,均设有开关芯片;所述目标选择芯片的多个引脚分别连接对应的开关芯片的控制端。

技术总结

本技术涉及服务器技术领域,具体提供一种存储器的适配能力测试装置,包括:存储器插槽,所述存储器插槽用于搭载待测存储器;所述存储器插槽搭载的待测存储器通过二选一开关芯片分别连接主控芯片和BMC,所述BMC连接所述二选一开关芯片的控制端口;所述主控芯片的IO接口连接BMC;所述BMC通过I2C线路连接复杂可编程逻辑器件;所述存储器插槽连接供电电源,且所述存储器插槽与供电电源之间串联有供电开关。本技术提高了存储器适配能力检测的可靠性。

技术研发人员:杨德浩

受保护的技术使用者:苏州元脑智能科技有限公司

技术研发日:20240430

技术公布日:2024/12/19

- 还没有人留言评论。精彩留言会获得点赞!