一种波导式光电探测器的制作方法

1.本申请涉及光通信技术领域,尤其涉及一种波导式光电探测器。

背景技术:

2.高性能的光电探测器(photodetector)是高速光通讯的核心器件之一,波导式光接收器件对于高度集成化有很大的优势,但是随着带宽的需求越来越高,许多团队采用单晶硅接触(si-contact)来取代锗接触(ge-contact),通过优化金属/半导体接面的电学特性可以降低接触电阻及暗电流特性,预期整体性能相较垂直(vertical)结构会大大提升。论文

“-

1v bias 67ghz bandwidth si-contacted germanium waveguide p-i-n photodetector for optical links at 56gbps and beyond”《-1v偏置67ghz带宽si接触锗波导pin光电探测器,用于56gbps及以上的光链路》(期刊“optics express”(光学快讯)第24卷第5期)公开了一种侧向(lateral)结构的pin建立在si与ge的堆栈结构下,透过较窄的锗宽度(<0.5微米)来提升载子渡越时间(transit time),但是尺寸窄化会造成光响应度的牺牲,因此还需要增加一个poly-si(多晶硅)来辅助光波导耦合,以增加光响应度。但是通过增加耦合器来辅助光波导耦合,对光模式有较多的限制,又额外引入了偏振相关损耗(pdl),而且工艺比较复杂。

3.为了解决光耦合问题,专利申请《用于没有锗层接触的硅上锗光电探测器的方法和系统》(申请号:cn 201510864620.4)公开了一种硅上锗光电探测器,透过沟槽的外延生长,控制锗的尺寸与光耦合问题,在速度与响应度都有不错的性能,但衍生了暗电流偏大(>500na)的问题,影响器件的灵敏问题。

技术实现要素:

4.本申请的目的在于提供一种波导式光电探测器,结合了垂直与水平pin结构的优点,具有高传输速度、高响应度和低暗电流等优点。

5.为了实现上述目的之一,本申请提供了一种波导式光电探测器,包括:

6.衬底,至少包括一硅层,所述硅层上形成有硅波导;

7.主动层,设于所述硅波导上,所述主动层上形成有第一掺杂区域;

8.所述硅层位于所述主动层下方的位置形成有水平pin结,所述水平pin结包括第二掺杂区域、第一本征区域和第三掺杂区域,所述第一本征区域分别连接所述第二掺杂区域和第三掺杂区域;

9.所述第二掺杂区域与所述第一掺杂区域的掺杂类型相同,所述第二掺杂区域临近所述第一本征区域的一端与所述第一掺杂区域连接;所述第一本征区域和所述第三掺杂区域位于所述主动层下面,所述第三掺杂区域、所述主动层及所述第一掺杂区域形成垂直pin结。

10.作为实施方式的进一步改进,所述第三掺杂区域延伸至所述主动层外侧。

11.作为实施方式的进一步改进,所述硅层上还设有第二本征区域和第四掺杂区域,

所述第二本征区域分别连接所述第三掺杂区域和第四掺杂区域,所述第三掺杂区域、第二本征区域及第四掺杂区域形成水平pin结;

12.所述第四掺杂区域与所述第一掺杂区域的掺杂类型相同,所述第四掺杂区域临近所述第二本征区域的一端与所述第一掺杂区域连接。

13.作为实施方式的进一步改进,所述硅波导上设有一凹槽或单边槽,所述主动层由所述凹槽或单边槽的槽底延伸至硅波导上方。

14.作为实施方式的进一步改进,所述主动层的厚度在0.1微米~1微米的范围内。

15.作为实施方式的进一步改进,所述主动层的宽度在0.3微米~20微米的范围内。

16.作为实施方式的进一步改进,所述第一本征区域的宽度与所述主动层的厚度之比大于或等于0.5。

17.作为实施方式的进一步改进,所述主动层包括硅层、锗硅层、锗层或锗锡层其中的一种或多种的组合。

18.作为实施方式的进一步改进,所述锗硅层为si

x

ge

1-x

,其中x≤10%;所述锗锡层为sn

x

ge

1-x

,其中x≤10%。

19.作为实施方式的进一步改进,所述第二掺杂区域还包括第一电极接触区,所述第一电极接触区位于所述第二掺杂区域远离所述主动层的一端;

20.所述第三掺杂区域还包括第二电极接触区,所述第二电极接触区位于所述第三掺杂区域远离所述主动层的一端。

21.作为实施方式的进一步改进,所述硅波导为脊波导或条状波导。

22.本申请的有益效果:本申请结合了垂直与水平pin结构的优点,采用了垂直的pin结构和水平的硅电极接触,减少了金属电极的光学吸收,解决了锗电极接触引起的暗电流问题,有效提高了传输速度、响应度,降低了暗电流。

附图说明

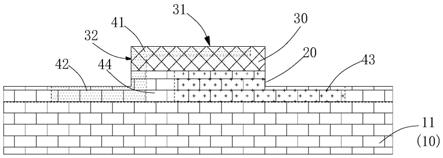

23.图1为本申请波导式光电探测器实施例1的芯片截面示意图;

24.图2为本申请波导式光电探测器实施例1结构示意图;

25.图3为本申请实施例1主动层结构的一种变形示意图;

26.图4为本申请波导式光电探测器实施例2的芯片截面示意图;

27.图5为本申请实施例2主动层结构的一种变形示意图;

28.图6为本申请波导式光电探测器实施例3的芯片截面示意图;

29.图7为本申请实施例3衬底及硅波导结构示意图;

30.图8为本申请实施例3硅波导结构的一种变形示意图;

31.图9为本申请实施例3的主动层结构的一种变形示意图;

32.图10为本申请实施例3的掺杂区域的另一种变形示意图;

33.图11为本申请波导式光电探测器实施例4的芯片截面示意图;

34.图12为本申请波导式光电探测器中硅波导的一种变形示意图。

具体实施方式

35.以下将结合附图所示的具体实施方式对本申请进行详细描述。但这些实施方式并

不限制本申请,本领域的普通技术人员根据这些实施方式所做出的结构、方法、或功能上的变换均包含在本申请的保护范围内。

36.在本申请的各个图示中,为了便于图示,结构或部分的某些尺寸会相对于其它结构或部分夸大,因此,仅用于图示本申请的主题的基本结构。

37.另外,本文使用的例如“上”、“上方”、“下”、“下方”等表示空间相对位置的术语是出于便于说明的目的来描述如附图中所示的一个单元或特征相对于另一个单元或特征的关系。空间相对位置的术语可以旨在包括设备在使用或工作中除了图中所示方位以外的不同方位。例如,如果将图中的设备翻转,则被描述为位于其他单元或特征“下方”或“之下”的单元将位于其他单元或特征“上方”。因此,示例性术语“下方”可以囊括上方和下方这两种方位。设备可以以其他方式被定向(旋转90度或其他朝向),并相应地解释本文使用的与空间相关的描述语。当元件或层被称为在另一部件或层“上”、与另一部件或层“连接”时,其可以直接在该另一部件或层上、连接到该另一部件或层,或者可以存在中间元件或层。

38.在硅光技术的光接收器上,对波导式锗光电探测器的性能要求越来越高,要求兼具高速、高响应度和低暗电流。本申请提供的波导式光电探测器,在顶层为硅层的衬底上定义水平的pin结构,并在该水平的pin结构上外延主动层(如本征锗波导),在主动层上定义p掺杂结构,并使该p掺杂结构与硅层上形成水平pin结的p掺杂区域连接。或者在主动层上定义n掺杂结构,并使该n掺杂结构与硅层上形成水平pin结的n掺杂区域连接。主动层波导上的p掺杂结构或n掺杂结构与顶层硅层的n掺杂区域或p掺杂区域形成垂直的pin结构。该结构结合了垂直与水平pin结构的优点,采用了垂直的pin结构和水平的硅电极接触,减少了金属电极的光学吸收,解决了锗电极接触引起的暗电流问题,有效提高了传输速度、响应度,降低了暗电流。具体的,在以下实施例中进行阐述。

39.实施例1

40.如图1所示的实施例1,该实施例的波导式光电探测器包括衬底10和主动层30。其中,衬底10至少包括一硅层,该硅层上形成有硅波导20,该实施例的衬底10采用的是一硅基板11,主动层30为一锗波导,在硅基板11的上表层上形成有硅波导20,在硅波导20上外延生长锗波导。主动层30(锗波导)包括相对的两侧壁32,且主动层30的顶部31及其中至少一侧壁32形成连续的第一掺杂区域41。上述硅基板11位于主动层30下方的位置形成有水平pin结,该实施例的结构,在主动层30下方的位置形成有一个水平pin结,在其它实施例中也可以形成有两个水平pin结。该水平pin结包括第二掺杂区域42、第一本征区域44和第三掺杂区域43,其中第一本征区域44分别连接第二掺杂区域42和第三掺杂区域43。这里,第二掺杂区域42与上述第一掺杂区域41的掺杂类型相同,且第二掺杂区域42临近第一本征区域44的一端与上述第一掺杂区域41连接,第一本征区域44位于主动层30下面、临近主动层30与第二掺杂区域42连接的侧壁32的一侧;第三掺杂区域43则位于主动层30下面,与上述第一掺杂区域41形成垂直pin结。上述第一本征区域44的宽度与主动层30的厚度之比大于或等于0.5,该实施例中,第一本征区域44的宽度与上述垂直pin结的两个掺杂区域的间距相当,使得主动层上具有相对均匀的电场分布。或者第一本征区域44的宽度也可以大于垂直pin结的两个掺杂区域的间距,以增加主动层的电位分布和电场强度。

41.该实施例中,第三掺杂区域43延伸至主动层30外侧的硅基板11上,金属电极在主动层30之外的硅基板11上分别与第二掺杂区域42和第三掺杂区域43电连接,避免了主动层

30与金属电极的接触,解决了锗接触结构暗电流大的问题,有效降低了暗电流,可达到暗电流小于50na,提升了器件的电学性能。而且采用的垂直式的pin结构,吸收光的主动层的厚度可以精确控制在0.1微米~1微米的范围内,可以更精准地控制渡越时间,速度更快,而且较低的硅接触电阻,可以大幅降低rc延迟的时间常数,进一步提升了速度。另外,垂直式的pin结构光生载流子的渡越时间不受主动层宽度尺寸的影响,主动层接收光的面积可以做得更大,该实施例中主动层的宽度可以做到0.3微米~20微米的范围,或者更宽,具有更大的光吸收区域,且没有传统垂直式pin结构上面的金属电极的光学吸收,大大提升了光学耦合效率,从而有效提高了响应度,响应度可达到0.9a/w以上。

42.具体的,如图2所示的波导式光电探测器,在主动层30及硅基板11上覆盖有包层50,在包层50的上表面设置至少两个金属电极71、72,分别作为阳极和阴极,包层50上还设有第一导电通道61和第二导电通道62,分别与上述主动层30之外的硅基板11上的第二掺杂区域42和第三掺杂区域43连接,导电通道61、62的另一端与上述两个金属电极导71、72电连接,以将光探测器产生的电信号导出。这里,第二掺杂区域42还可在远离主动层30的一端设置第一电极接触区421,第三掺杂区域43也可在远离主动层30的一端设置第二电极接触区431,上述第一导电通道61和第二导电通道62分别与第一电极接触区421和第二电极接触区432连接。其中,第一电极接触区421的掺杂浓度可以高于第二掺杂区域42其它部分的掺杂浓度,第二电极接触区431的掺杂浓度可以高于第三掺杂区域43其它部分的掺杂浓度,以减小掺杂区域的电阻,进一步提升光探测器的带宽。

43.如图1所示,该实施例中第二掺杂区域42与第一掺杂区域41的连接方式为掺杂的硅波导的侧壁与掺杂的主动层30的侧壁32相互抵接。即,主动层30的宽度小于或等于硅波导20的宽度,主动层30的侧壁32也位于硅波导20上,第二掺杂区域42包括硅波导20的一侧壁,第一掺杂区域41也包括主动层30的一侧壁32,通过掺杂的硅波导20的侧壁与主动层30上的第一掺杂区域41连接。

44.在其它实施例中,如图3所示,主动层30掺杂的侧壁32可以包绕于硅波导20外侧,延伸至硅波导20外侧的硅基板11上,与第二掺杂区域42连接,第二掺杂区域42只掺杂在硅波导20外侧的硅基板11上,与其临近的硅波导20的侧壁则构成第一本征区域44。当包绕硅波导20外侧的主动层30的侧壁32厚度足够的情况下,第一本征区域44也可以包括主动层30侧壁32内侧靠近硅波导20侧壁的部分,只在主动层30的侧壁32表层掺杂合适的厚度,并与硅波导20外侧硅基板11上的第二掺杂区域42连接。

45.上述的第一掺杂区域41和第二掺杂区域42可以是p型掺杂,如第一掺杂区域41为p+ge,第二掺杂区域42为p+si,第三掺杂区域43为n型掺杂,如n+si。或者,也可以是反过来的,第一掺杂区域41为n+ge,第二掺杂区域42为n+si,第三掺杂区域43为p+si。如图1-3所示,第二掺杂区域42位于硅波导20的左侧,第一掺杂区域41包括主动层30的顶部31和左侧壁,通过掺杂的左侧壁与第二掺杂区域42连接。在其它的实施例中,第二掺杂区域42也可以设于硅波导20的右侧,第一掺杂区域41包括主动层30的顶部31和右侧壁,通过掺杂的右侧壁与第二掺杂区域42连接。

46.该实施例中的主动层为一锗波导,在其它的实施例中,主动层还可以是硅层、锗硅层、锗层或锗锡层其中的一种或多种的组合。这里,锗硅层为si

x

ge

1-x

,其中x≤10%,锗锡层为sn

x

ge

1-x

,其中x≤10%。

47.实施例2

48.如图4所示的波导式光电探测器的芯片截面示意图,与实施例1不同的是,该实施例中主动层30的顶部31及其两个侧壁32形成连续的第一掺杂区域41,即第一掺杂区域41包括了主动层30的顶部31和两个侧壁32;在硅基板11上还设有第二本征区域45和第四掺杂区域46,其中,第二本征区域45分别连接上述第三掺杂区域43和第四掺杂区域46,形成第二个水平pin结;该第四掺杂区域46与上述第一掺杂区域41的掺杂类型相同,第四掺杂区域46临近第二本征区域45的一端与第一掺杂区域41连接。

49.该实施例中,主动层30的宽度小于或等于硅波导20的宽度,主动层30的侧壁32也位于硅波导20上,第二掺杂区域42包括硅波导20的一侧壁,第四掺杂区域46包括硅波导20的另一侧壁,第二掺杂区域42和第四掺杂区域46分别通过掺杂的硅波导20的侧壁与主动层30上的第一掺杂区域41连接。第三掺杂区域43位于主动层30下方的硅波导20上,与第一掺杂区域41形成垂直pin结;另外,第三掺杂区域43分别与两侧的第二掺杂区域42和第四掺杂区域46形成水平的pin结,两个水平pin结分别位于硅波导20上靠近主动层30两侧壁32的位置。

50.在其它实施例中,如图5所示,主动层30掺杂的侧壁32可以包绕于硅波导20外侧,延伸至硅波导20外侧的硅基板11上,分别与第二掺杂区域42和第四掺杂区域46连接,第二掺杂区域42和第四掺杂区域46则只掺杂在硅波导20两侧壁外侧的硅基板11上,与第二掺杂区域42临近的硅波导20的侧壁构成第一本征区域44,与第四掺杂区域46临近的硅波导20的侧壁构成第四本征区域45。当包绕硅波导20外侧的主动层30的侧壁32厚度足够的情况下,第一本征区域44和第二本征区域45也可以分别包括主动层30两侧壁32内侧靠近硅波导20侧壁的部分,只在主动层30的两侧壁32表层掺杂合适的厚度,并分别与硅波导20外侧硅基板11上的第二掺杂区域42和第四掺杂区域44连接。

51.实施例3

52.如图6和7所示,与上述实施例1和2不同的是,该实施例中,硅波导20上设有一凹槽21,主动层30则由该凹槽21的槽底延伸至硅波导20上方。在其它实施例中,如图8所示,上述凹槽也可以是单边槽21。

53.该实施例中,主动层30由硅波导20的凹槽21槽底直接往上外延生长形成。主动层30的顶部31及一侧壁32掺杂形成第一掺杂区域41。凹槽21的一侧壁及该侧壁外侧的硅基板11掺杂形成第二掺杂区域42,凹槽21的底部则形成第一本征区域44和第三掺杂区域43,其中第一本征区域44分别连接第二掺杂区域42和第三掺杂区域43。第一掺杂区域41和第二掺杂区域42通过掺杂的主动层30侧壁32和掺杂的凹槽21侧壁相互连接。第一掺杂区域41、主动层30和第三掺杂区域43形成垂直pin结,第二掺杂区域42、第一本征区域44和第三掺杂区域43形成水平pin结。

54.该实施例中,上述第三掺杂区域43还延伸至硅波导外侧的硅基板上。通过第二掺杂区域42和第三掺杂区域43位于硅波导20外侧的部分与金属电极接触,避免了主动层30与金属电极的接触,解决了锗接触结构暗电流大的问题,有效降低了暗电流,提升了器件的电学性能。

55.在其它实施例中,如图9所示,主动层30也可以由凹槽21底部外延生长至凹槽21上方并覆盖凹槽21的侧壁。在主动层30位于凹槽21上方的部分掺杂形成第一掺杂区域41,在

凹槽21的一侧壁及该侧壁外侧的硅基板11掺杂形成第二掺杂区域42,第一掺杂区域41和第二掺杂区域42通过凹槽21的上述掺杂侧壁相互连接。而凹槽21的另一侧壁则没有掺杂,上述第三掺杂区域43只形成在凹槽21的底部,并往硅波导20外侧的硅基板11延伸。

56.如图10所示,在其它实施例中,还可在硅基板11上设置第二本征区域45和第四掺杂区域46。其中,第二本征区域45分别连接上述第三掺杂区域43和第四掺杂区域46,形成第二个水平pin结;该第四掺杂区域46与上述第一掺杂区域41的掺杂类型相同,第四掺杂区域46临近第二本征区域45的一端与第一掺杂区域41接触连接。上述依次排列的第一本征区域44、第三掺杂区域43和第二本征区域45均形成于硅波导20的凹槽21的槽底。

57.实施例4

58.如图11所示的波导式光电探测器的芯片截面示意图,与上述实施例1-3不同的是,该实施例中衬底10采用的是soi(silicon-on-insulator,绝缘体上硅)的结构,包括依次层叠的硅基板11、掩埋绝缘层12(box)和顶层硅13。上述硅波导20和形成水平pin结的本征区域44、第二掺杂区域42和第三掺杂区域43等形成于顶层硅13上。

59.上述各实施例中的硅波导20均为脊波导,在其它实施例中,如图12所示,硅波导20也可以采用条状波导,例如可以通过刻蚀衬底10的硅层形成条状波导。上述第二掺杂区域42、第一本征区域44、第三掺杂区域43,或者还有第二本征区域和第四掺杂区域均形成于条状波导上。当然也可以在条状波导上刻蚀凹槽,再由凹槽底部开始往上外延生长主动层。

60.上文所列出的一系列的详细说明仅仅是针对本申请的可行性实施方式的具体说明,它们并非用以限制本申请的保护范围,凡未脱离本申请技艺精神所作的等效实施方式或变更均应包含在本申请的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1