半导体封装、半导体装置以及电力变换装置的制作方法

本公开涉及半导体封装、半导体装置以及电力变换装置。

背景技术:

1、以往,有被称为功率半导体元件的半导体元件。功率半导体元件是应对高电压以及大电流的半导体元件。在功率半导体元件中,有通电路径沿着功率半导体元件的纵向的元件。将功率半导体元件安装到电路基板上并且利用密封树脂封装而成的功率半导体封装与被称为散热器(heat sink)的冷却器、控制零件等连接。与散热器连接的功率半导体封装作为半导体装置用于工业机器、汽车、铁路等广泛的领域。

2、近年来,伴随搭载有半导体装置的机器的小型化以及轻量化,还要求功率半导体封装的小型化以及轻量化。例如,日本特开2014-179612号公报(专利文献1)记载的半导体器件模块(半导体封装)具备半导体器件(半导体元件)、电介体层(第1绝缘层)以及金属化层(第1布线层)。半导体器件模块能够用作功率半导体封装。电介体层叠加于半导体器件。在电介体层设置有与半导体器件重叠的贯通孔。金属化层通过贯通孔与半导体器件的电极电连接。由此,金属化层的布线被抽出到电介体层的表面。因此,金属化层的布线叠加于电介体层。因此,能够实现半导体器件模块的沿着宽度方向的小型化。

3、另外,功率半导体封装的功率半导体元件在高电压以及大电流下开关动作。在开关动作中功率半导体元件从截止状态成为导通状态时,对功率半导体元件施加浪涌电压。浪涌电压的大小与电流的时间变化率以及功率半导体封装的布线的电感成比例。在浪涌电压大的情况下,功率半导体元件可能劣化。因此,在功率半导体封装中,与小型化一起,还要求降低电感。

4、现有技术文献

5、专利文献

6、专利文献1:日本特开2014-179612号公报

技术实现思路

1、然而,在上述文献记载的半导体封装(半导体器件模块)中,在以确保相邻的布线的绝缘距离的方式对第1布线层(金属化层)进行布线的情况下,布线复杂化。在布线复杂化的情况下,难以考虑在相邻的布线中流过的电流的朝向,所以有时在相邻的布线中流过相同朝向的电流。由此,在第1布线层中,产生由于电流引起的磁通的影响。因此,难以降低半导体封装的电感。

2、本公开是鉴于上述课题完成的,其目的在于提供能够降低电感的半导体封装、半导体装置以及电力变换装置。

3、本公开的半导体封装具备半导体元件、第1绝缘层、第1布线层、第2绝缘层以及第2布线层。第1绝缘层覆盖半导体元件。在第1绝缘层设置有第1贯通孔以及第2贯通孔。第1布线层包括第1层部。第1层部覆盖第1绝缘层。第1布线层通过第1贯通孔与半导体元件电连接。第2绝缘层覆盖第1绝缘层以及第1布线层。在第2绝缘层设置有第3贯通孔。第3贯通孔与第2贯通孔连通。第2布线层通过第2贯通孔以及第3贯通孔与半导体元件电连接。第2布线层包括第2层部。第2层部覆盖第2绝缘层。第2布线层的第2层部具有在夹着第2绝缘层的状态下叠加于第1布线层的第1层部的部分。

4、根据本公开的半导体封装,第2布线层的第2层部具有叠加于第1布线层的第1层部的部分。因此,能够使在第2层部的叠加于第1布线层的第1层部的部分中流过的电流的朝向与在第1层部中流过的电流的朝向相反。由此,能够相互抵消由于在第1层部中流过的电流以及在第2层部中流过的电流分别引起的磁通的影响。因此,能够降低半导体封装的电感。

技术特征:

1.一种半导体封装,具备:

2.根据权利要求1所述的半导体封装,其中,

3.根据权利要求1或者2所述的半导体封装,其中,

4.根据权利要求3所述的半导体封装,其中,还具备:

5.根据权利要求1~4中的任意一项所述的半导体封装,其中,还具备:

6.根据权利要求5所述的半导体封装,其中,

7.根据权利要求5或者6所述的半导体封装,其中,

8.根据权利要求7所述的半导体封装,其中,

9.根据权利要求8所述的半导体封装,其中,

10.根据权利要求7~9中的任意一项所述的半导体封装,其中,

11.一种半导体装置,具备:

12.一种半导体装置,具备:

13.一种半导体装置,具备:

14.一种电力变换装置,具备:

技术总结

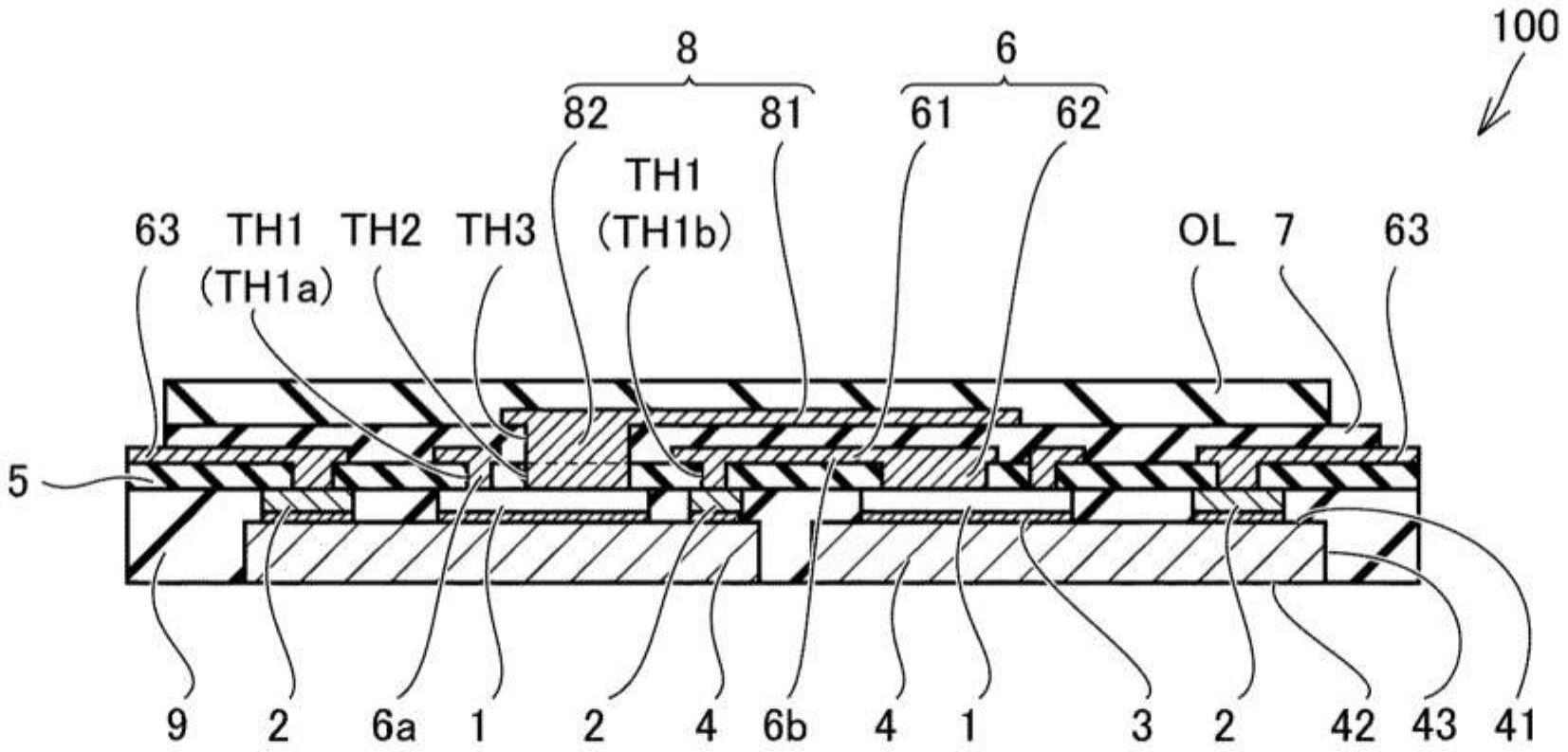

半导体封装(100)具备半导体元件(1)、第1绝缘层(5)、第1布线层(6)、第2绝缘层(7)以及第2布线层(8)。第1绝缘层(5)覆盖半导体元件(1)。第1布线层(6)包括第1层部(61)。第1层部(61)覆盖第1绝缘层(5)。第2绝缘层(7)覆盖第1绝缘层(5)以及第1布线层(6)。第2布线层(8)通过第2贯通孔(TH2)以及第3贯通孔(TH3)与半导体元件(1)电连接。第2布线层(8)包括第2层部(81)。第2层部(81)覆盖第2绝缘层(7)。第2布线层(8)的第2层部(81)具有在夹着第2绝缘层(7)的状态下叠加于第1布线层(6)的第1层部(61)的部分。

技术研发人员:原田耕三,六分一穗隆

受保护的技术使用者:三菱电机株式会社

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!