半导体装置的制作方法

1.本发明涉及半导体装置。

背景技术:

2.在对铝电极进行导线键合时,铝沿超声波振动方向受到排斥。因此,导线与铝电极的接合强度产生波动,所以成为使半导体装置的可靠性降低的一个原因。与此相对,公开了在键合区域,在铝电极之下局部地设置有层间膜的半导体装置(例如,参照专利文献1)。由此,在铝电极的表面产生凹凸,因此能够抑制导线键合时的铝的排斥。

3.专利文献1:日本特开2012

‑

109419号公报

4.有时在铝电极之下形成有阻挡金属层。存在下述问题,即,由于阻挡金属与层间膜之间的密接性差,所以半导体装置的可靠性降低。

技术实现要素:

5.本发明就是为了解决上述这样的课题而提出的,其目的在于,得到能够减小导线键合的接合强度的波动,提高可靠性的半导体装置。

6.本发明涉及的半导体装置具有与导线之间的键合区域,该半导体装置的特征在于,具有:半导体基板;氧化膜,其在所述键合区域设置于所述半导体基板的主面;多晶硅层,其设置于所述氧化膜之上;层间膜,其在所述多晶硅层之上局部地设置;阻挡金属,其直接设置于所述多晶硅层和所述层间膜之上;以及电极,其设置于所述阻挡金属之上。

7.发明的效果

8.在本发明中,在键合区域局部地设置有层间膜,在其上设置有阻挡金属以及铝电极。由此,在导线键合时,层间膜相对于阻挡金属以及铝电极而成为锚,因此能够抑制铝电极的构成金属的排斥。因此,能够减小导线键合的接合强度的波动。另外,在层间膜之下形成多晶硅层。阻挡金属与多晶硅层之间的密接性比阻挡金属与层间膜之间的密接性强。因此,通过多晶硅层对阻挡金属与层间膜之间的密接性的强度进行弥补,从而阻挡金属的密接性提高,因此能够提高半导体装置的可靠性。

附图说明

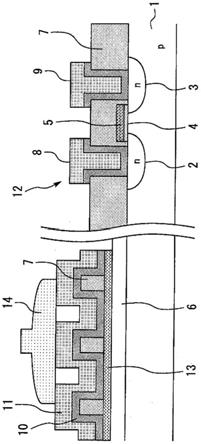

9.图1是表示实施方式1涉及的半导体装置的剖视图。

10.图2是表示实施方式1涉及的半导体装置的键合区域处的层间膜的图案的俯视图。

11.图3是表示实施方式2涉及的半导体装置的键合区域处的层间膜的图案的俯视图。

具体实施方式

12.参照附图,对实施方式涉及的半导体装置进行说明。对相同或者相应的结构要素标注相同的标号,有时省略重复说明。

13.实施方式1.

14.图1是表示实施方式1涉及的半导体装置的剖视图。半导体基板1是p型,在半导体基板1的表层彼此分离地设置有n型的源极区域2以及漏极区域3。在源极区域2与漏极区域3之间的半导体基板1之上隔着栅极绝缘膜4而形成有栅极电极5。栅极电极5被层间膜7覆盖。层间膜7是氧化膜,例如是teos/bpsg/teos的层叠构造。

15.源极电极8经由层间膜7的开口而与源极区域2连接。漏极电极9经由层间膜7的开口而与漏极区域3连接。源极电极8以及漏极电极9由阻挡金属10以及铝电极11构成。阻挡金属10是为了抑制铝电极11与半导体基板1的接触电阻的增大而设置的,例如是ti/tin的层叠构造。这样,在半导体基板1之上构成有mosfet等晶体管12。

16.半导体装置在不对晶体管12或者二极管等半导体元件的电气特性产生影响的无效区域具有与导线14之间的键合区域。在键合区域,在半导体基板1之上设置有膜厚1600nm的氧化膜6。氧化膜6是半导体元件间的分离层,例如是sio2等。在氧化膜6之上设置有膜厚450nm的多晶硅层13。在多晶硅层13之上局部地设置有膜厚1500nm的层间膜7。膜厚100nm的阻挡金属10直接设置于多晶硅层13和层间膜7之上,与多晶硅层13、层间膜7接触。在阻挡金属10之上设置有膜厚13000nm的铝电极11。

17.这里,层间膜7的上方为凸,层间膜7彼此之间的区域的上方为凹。即,铝电极11的表面与层间膜7的图案匹配地成为凹凸形状。在键合区域,导线14被键合于表面为凹凸形状的铝电极11。导线14例如是铜细线。此外,铜细线的硬度高,键合性差,因此,在键合时铝电极11的构成金属容易被排斥。

18.键合区域的铝电极11与晶体管12的源极电极8或者漏极电极9电连接。因此,晶体管12经由导线14而与外部电路连接。

19.在本实施方式中,在键合区域局部地设置有层间膜7,在其上设置有阻挡金属10以及铝电极11。由此,在导线键合时,层间膜7相对于阻挡金属10以及铝电极11而成为锚,因此能够抑制铝电极11的构成金属即铝的排斥。因此,能够减小导线键合的接合强度的波动。另外,在层间膜7之下形成多晶硅层13。阻挡金属10与多晶硅层13之间的密接性比阻挡金属10与层间膜7之间的密接性高。因此,通过多晶硅层13对阻挡金属10与层间膜7之间的密接性的强度进行弥补,从而阻挡金属10的密接性提高,因此能够提高半导体装置的可靠性。

20.多晶硅层13和栅极电极5由相同材质构成。因此,在制造工艺中,能够同时形成两者。但是,多晶硅层13与栅极电极5没有彼此连接。

21.为了使源极电极8以及漏极电极9与半导体基板1接触,对层间膜7进行蚀刻而形成开口。此时,键合区域处的层间膜7也图案化。图2是表示实施方式1涉及的半导体装置的键合区域处的层间膜的图案的俯视图。层间膜7具有在与半导体基板1的主面垂直的俯视观察时呈点状的图案。如果将点的纵横的宽度设为x,将点的间隔设为y,则x、y均为2μm~5μm。在点状的层间膜7之上设置的铝电极11也同样地以点状隆起。因此,导线14与铝电极11的接触面积变小,因而能够抑制铝电极11的铝的排斥的波动。

22.实施方式2.

23.图3是表示实施方式2涉及的半导体装置的键合区域处的层间膜的图案的俯视图。层间膜7具有在与半导体基板1的主面垂直的俯视观察时呈网格状的图案。如果将网格的开口的纵横的宽度设为x,将网格的开口的间隔设为y,则x、y均为2μm~5μm。其它结构与实施方式1相同。

24.层间膜7是网格状,因此与层间膜7是点状的情况相比,导线14与铝电极11的接触面积变大。由此,与点状的情况相比,能够以较弱的力进行键合,因此,减轻了对半导体元件的损伤。但是,铝电极11的铝的排斥稍微波动。

25.此外,半导体基板1不限于由硅形成,也可以由与硅相比带隙大的宽带隙半导体形成。宽带隙半导体例如是碳化硅、氮化镓类材料或者金刚石。由这样的宽带隙半导体形成的半导体装置的容许电流密度高,因此能够减小由导线直径的大口径化或者导线根数的增加引起的接合强度的波动。通过使用该半导体装置,从而组装了该半导体装置的半导体模块也能够小型化、高集成化。另外,半导体装置的耐热性高,因此,能够使散热器的散热鳍片小型化,能够使水冷部空冷化,因而能够使半导体模块进一步小型化。另外,半导体装置的电力损耗低且高效,因此能够使半导体模块高效化。

26.标号的说明

27.1半导体基板,6氧化膜,7层间膜,10阻挡金属,11铝电极,13多晶硅层,14导线

技术特征:

1.一种半导体装置,其具有与导线之间的键合区域,该半导体装置的特征在于,具有:半导体基板;氧化膜,其在所述键合区域设置于所述半导体基板的主面;多晶硅层,其设置于所述氧化膜之上;层间膜,其在所述多晶硅层之上局部地设置;阻挡金属,其直接设置于所述多晶硅层和所述层间膜之上;以及电极,其设置于所述阻挡金属之上。2.根据权利要求1所述的半导体装置,其特征在于,还具有晶体管,该晶体管设置于所述半导体基板,具有栅极电极,所述多晶硅层和所述栅极电极由相同材质构成。3.根据权利要求1或2所述的半导体装置,其特征在于,所述电极的表面与所述层间膜的图案匹配地成为凹凸形状。4.根据权利要求3所述的半导体装置,其特征在于,所述层间膜具有在与所述主面垂直的俯视观察时呈点状的图案。5.根据权利要求3所述的半导体装置,其特征在于,所述层间膜具有在与所述主面垂直的俯视观察时呈网格状的图案。6.根据权利要求1至5中任一项所述的半导体装置,其特征在于,所述半导体基板由宽带隙半导体形成。

技术总结

得到能够减小导线键合的接合强度的波动,提高可靠性的半导体装置。半导体装置具有与导线(14)之间的键合区域。在键合区域,在半导体基板(1)的主面设置有氧化膜(6)。在氧化膜(6)之上设置有多晶硅层(13)。在多晶硅层(13)之上局部地设置有层间膜(7)。在多晶硅层(13)和层间膜(7)之上设置有阻挡金属(10)。在阻挡金属(10)之上设置有电极(11)。(10)之上设置有电极(11)。(10)之上设置有电极(11)。

技术研发人员:平田大介 山本晃央

受保护的技术使用者:三菱电机株式会社

技术研发日:2021.03.18

技术公布日:2021/9/24

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1