中介层及半导体封装的制作方法

本发明涉及一种半导体技术,尤其涉及一种中介层及半导体封装。

背景技术:

1、半导体技术发展非常快,尤其在半导体芯片朝向微型化发展的趋势下,半导体芯片的尺寸越缩越小,因此其上的间距(pitch)也随之变小,然而,在半导体芯片上的输出/输入(i/o)数目不变的情况下,安装半导体芯片的封装基板可以具有细间距(fine pitch)的程度会受到工艺限制,因此半导体芯片及封装基板之间间距不匹配(mismatch)的接合问题会日益严重,进而使半导体封装的信号无法有效传递。因此如何使半导体封装的信号有效传递已成为本领域研究人员的一大挑战。

技术实现思路

1、本发明提供一种中介层及半导体封装,其可以使半导体封装的信号有效传递。

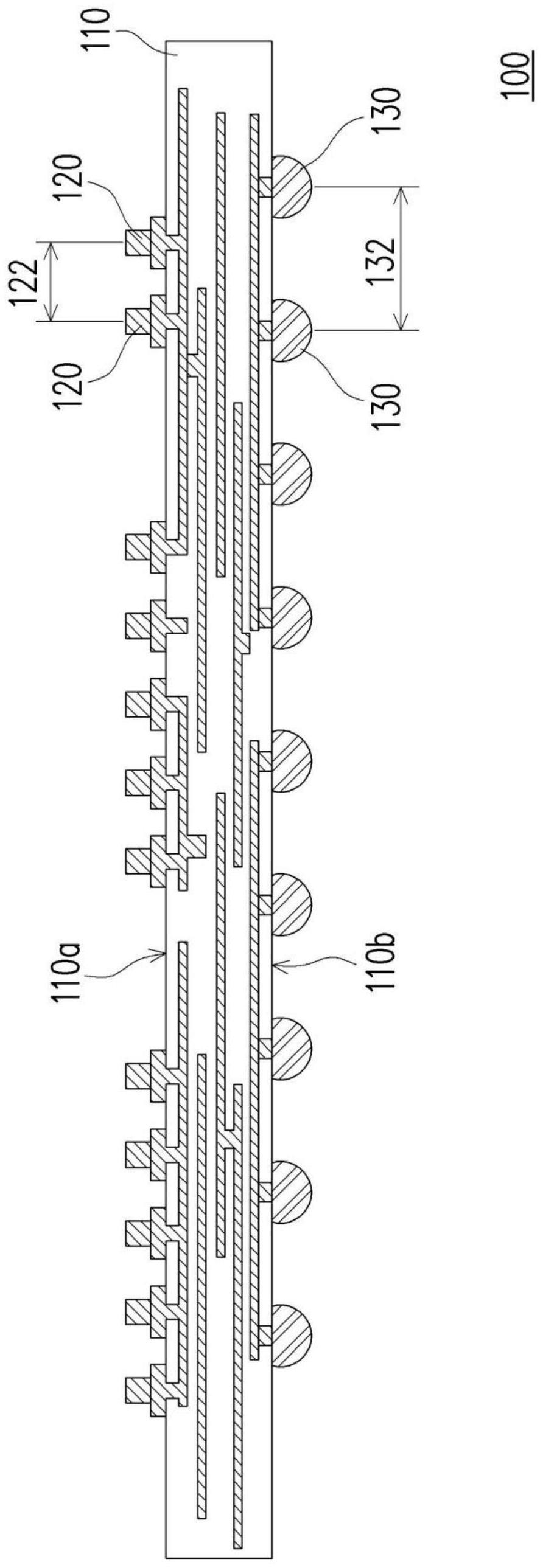

2、本发明的一种中介层,包括重布线结构、多个第一导电端子以及多个第二导电端子。多个第一导电端子设置于第一表面上。多个第一导电端子于重布线结构上的正投影面积皆位于电路范围轮廓内。相邻第一导电端子之间具有第一间距。多个第二导电端子设置于第二表面上。多个第二导电端子的第一部分于重布线结构上的正投影面积位于电路范围轮廓内,多个第二导电端子的第二部分于重布线结构上的正投影面积位于电路范围轮廓外。多个第一导电端子与多个第二导电端子电性连接。相邻第二导电端子之间具有第二间距。第二间距大于第一间距,且部分第二导电端子于重布线结构上的正投影面积位于电路范围轮廓外。

3、在本发明的一实施例中,上述的电路范围轮廓包括相互垂直的第一方向与第二方向,且多个第二导电端子的第二部分于第一方向或第二方向上位于电路范围轮廓外。

4、在本发明的一实施例中,上述的重布线结构以半导体材料为基底所形成或重布线结构以有机材料为基底所形成。

5、在本发明的一实施例中,上述的多个第一导电端子为微凸块的形式,且多个第二导电端子为c4凸块的形式。

6、在本发明的一实施例中,上述的第一间距为相邻第一导电端子之间的最小间距,且第二间距为相邻第二导电端子之间的最小间距。

7、本发明的一种半导体封装,包括封装基板、中介层以及至少一芯片。中介层设置于承载面上,且第二表面面向封装基板。至少一芯片设置于第一表面上,其中至少一芯片通过中介层与封装基板电性连接。

8、在本发明的一实施例中,上述的至少一芯片为多个芯片,且多个芯片并邻排列于中介层上。

9、在本发明的一实施例中,上述的半导体封装为基材上覆晶圆上覆芯片或积体扇出型封装。

10、在本发明的一实施例中,上述的半导体封装用以高速信号传输。

11、基于上述,本发明通过中介层的间距设计以及电路范围轮廓的布局,使中介层中在重布线结构的第二表面上的相邻第二导电端子(靠近封装基板)之间的第二间距大于中介层中在重布线结构的第一表面上的相邻第一导电端子(靠近芯片)之间的第一间距,如此一来,可以通过重布线结构的间距转换改善芯片与封装基板之间间具不匹配的问题,将芯片上细间距配置的接点转换至粗间距配置的封装基板的接点,进而可以使半导体封装的信号有效传递。

12、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

技术特征:

1.一种中介层,其特征在于,包括:

2.根据权利要求1所述的中介层,其特征在于,所述电路范围轮廓包括相互垂直的第一方向与第二方向,且所述多个第二导电端子的所述第二部分于所述第一方向或所述第二方向上位于所述电路范围轮廓外。

3.根据权利要求1所述的中介层,其特征在于:

4.根据权利要求1所述的中介层,其特征在于,所述多个第一导电端子为微凸块的形式,且所述多个第二导电端子为c4凸块的形式。

5.根据权利要求1所述的中介层,其特征在于,所述第一间距为相邻所述第一导电端子之间的最小间距,且所述第二间距为相邻所述第二导电端子之间的最小间距。

6.一种半导体封装,其特征在于,包括:

7.根据权利要求6所述的半导体封装,其特征在于,所述至少一芯片为多个芯片,所述多个芯片并邻排列于所述中介层上。

8.根据权利要求6所述的半导体封装,其特征在于,所述半导体封装为基材上覆晶圆上覆芯片或积体扇出型封装。

9.根据权利要求6所述的半导体封装,其特征在于,所述半导体封装用以高速信号传输。

技术总结

本发明提供一种中介层,包括重布线结构、多个第一导电端子以及多个第二导电端子。多个第一导电端子设置于第一表面上。多个第一导电端子于重布线结构上的正投影面积皆位于电路范围轮廓内。相邻第一导电端子之间具有第一间距。多个第二导电端子设置于第二表面上。多个第二导电端子的第一部分于重布线结构上的正投影面积位于电路范围轮廓内,多个第二导电端子的第二部分于重布线结构上的正投影面积位于电路范围轮廓外。多个第一导电端子与多个第二导电端子电性连接。相邻第二导电端子之间具有第二间距。第二间距大于第一间距。另提供一种半导体封装。

技术研发人员:张育儒,陈佳良,陈俊宏

受保护的技术使用者:创意电子股份有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!