半导体器件、半导体器件的制造方法及存储器与流程

本发明涉及集成电路以及电子元器件制造,具体而言,涉及一种半导体器件、半导体器件的制造方法及存储器。

背景技术:

1、快闪存储器(flash memory)又称为闪存,闪存的主要特点是在不加电的情况下能长期保持存储的信息,且具有集成度高、存取速度快、易于擦除和重写等优点,因此成为非挥发性存储器的主流存储器。根据结构的不同,闪存分为非门闪存(nor flash memory)和与非门闪存(nand flash memory)。相比nor flash memory,nand flash memory能提供及高的单元密度,可以达到高存储密度,并且写入和擦除的速度也更快。

2、随着平面型闪存的发展,半导体的生产工艺取得了巨大的进步。但是目前平面型闪存的发展遇到了各种挑战:物理极限,如曝光技术极限、显影技术极限及存储电子密度极限等。在此背景下,为解决平面型闪存遇到的困难以及追求更低的单位存储单元的生产成本,三维(3d)闪存应用而生,例如3d-nand闪存。

3、相关技术中,3d-nand闪存中字线(word line,简称wl)与字线之间存在电容耦合,影响存储器件的性能。

技术实现思路

1、本发明的目的在于提供一种半导体器件、半导体器件的制造方法及存储器,以解决现有技术中字线之间存在电容耦合的技术问题。

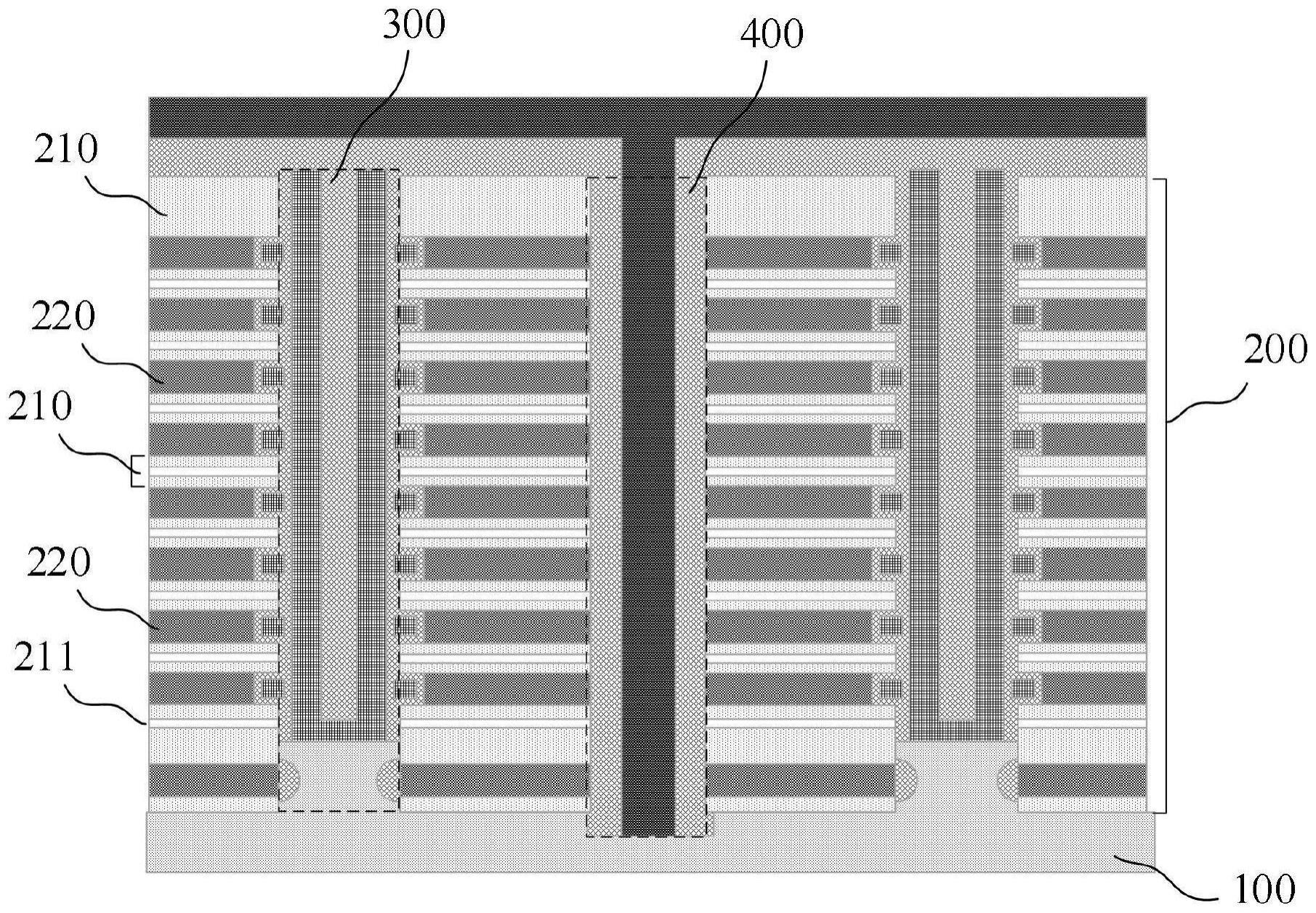

2、根据本申请实施例的第一方面,提供一种半导体器件,包括:

3、半导体衬底;

4、位于所述半导体衬底上的堆叠结构,所述堆叠结构包括交替层叠的若干层绝缘层和若干层导电层;至少部分所述绝缘层中设置有气隙;

5、垂直于所述半导体衬底设置的沟道孔,所述沟道孔贯穿所述堆叠结构;

6、贯穿所述堆叠结构的隔离沟槽,所述隔离沟槽垂直于所述半导体衬底。

7、进一步地,所述堆叠结构中与所述半导体衬底相邻的第一层结构为绝缘层,远离所述半导体衬底的最后一层结构为绝缘层;

8、第一层绝缘层和最后一层绝缘层中未设置气隙,其余绝缘层中均设置有气隙。

9、进一步地,所述气隙的厚度不超过该气隙所在的绝缘层厚度的三分之一。

10、进一步地,所述沟道孔的底部设置有衬底延伸区;所述衬底延伸区的厚度大于第一层绝缘层与第一层导电层的厚度之和。

11、进一步地,所述沟道孔的侧壁上设置有隧道层;所述隧道层向内依次设置有多晶硅沉积层和氧化物沉积层。

12、进一步地,在所述导电层与所述隧道层的交界处,所述导电层与所述隧道层之间依次设置有一层氧化硅-氮化硅-氧化硅复合材质和一层非晶硅材质。

13、进一步地,所述隔离沟槽的侧壁上设置有氧化物沉积层,氧化物沉积层内部填充有金属沉积层。

14、根据本申请实施例的第二方面,提供一种半导体器件的制作方法,包括:

15、在半导体衬底上交替堆叠绝缘层和中间介质层,形成多层的堆叠结构;其中,至少部分绝缘层为支撑层、牺牲层、支撑层的层叠结构;

16、形成贯穿堆叠结构的沟道孔;

17、形成贯穿堆叠结构的隔离沟槽;

18、通过所述隔离沟槽去除所述中间介质层,在原中间介质层的位置形成导电层;

19、通过所述隔离沟槽去除所述绝缘层中的牺牲层,在绝缘层中形成气隙;

20、在隔离沟槽中形成沟槽结构。

21、进一步地,形成贯穿堆叠结构的沟道孔之后,还包括:

22、在沟道孔中形成沟道结构。

23、进一步地,所述在沟道孔中形成沟道结构的步骤包括:

24、从沟道孔的底部向上生长出衬底延伸区;

25、从沟道孔的侧壁向外刻蚀掉一部分中间介质层;

26、在沟道孔的底面和侧壁上依次沉积一层氧化硅-氮化硅-氧化硅复合材料、一层非晶硅材料;

27、将非晶硅材料进行回蚀刻;

28、在非晶硅材料上沉积隧道层,并将隧道层的底部打开;

29、依次进行沟道多晶硅沉积、原子层氧化物沉积,在沟道孔中形成沟道结构。

30、进一步地,所述在原中间介质层的位置形成导电层的步骤包括:

31、向隔离沟槽中填充导电材料,将隔离沟槽和原中间介质层的位置填充满;

32、对导电材料进行回刻蚀,重新刻蚀出隔离沟槽,从而在原中间介质层的位置形成导电层。

33、进一步地,所述在隔离沟槽中形成沟槽结构的步骤包括:

34、进行原子层氧化物沉积,并将底部打开;

35、在剩余空间中填充金属导电材料。

36、根据本申请实施例的第三方面,提供一种存储器,包括如上任意一种实施例所述的半导体器件。

37、进一步地,所述存储器为3d-nand存储器。

38、本申请的实施例提供的技术方案具备以下有益效果:

39、本申请的方案在半导体器件中引入气隙(air gap),从而降低字线与字线之间的电容耦合,提升半导体器件的性能。

40、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述堆叠结构中与所述半导体衬底相邻的第一层结构为绝缘层,远离所述半导体衬底的最后一层结构为绝缘层;

3.根据权利要求2所述的半导体器件,其特征在于,所述气隙的厚度不超过该气隙所在的绝缘层厚度的三分之一。

4.根据权利要求2所述的半导体器件,其特征在于,所述沟道孔的底部设置有衬底延伸区;所述衬底延伸区的厚度大于第一层绝缘层与第一层导电层的厚度之和。

5.根据权利要求4所述的半导体器件,其特征在于,所述沟道孔的侧壁上设置有隧道层;所述隧道层向内依次设置有多晶硅沉积层和氧化物沉积层。

6.根据权利要求5所述的半导体器件,其特征在于,在所述导电层与所述隧道层的交界处,所述导电层与所述隧道层之间依次设置有一层氧化硅-氮化硅-氧化硅复合材质和一层非晶硅材质。

7.根据权利要求1-5任一项所述的半导体器件,其特征在于,所述隔离沟槽的侧壁上设置有氧化物沉积层,氧化物沉积层内部填充有金属沉积层。

8.一种半导体器件的制作方法,其特征在于,包括:

9.根据权利要求8所述的方法,其特征在于,形成贯穿堆叠结构的沟道孔之后,还包括:

10.根据权利要求9所述的方法,其特征在于,所述在沟道孔中形成沟道结构的步骤包括:

11.根据权利要求8-10任一项所述的方法,其特征在于,所述在原中间介质层的位置形成导电层的步骤包括:

12.根据权利要求8-10任一项所述的方法,其特征在于,所述在隔离沟槽中形成沟槽结构的步骤包括:

13.一种存储器,其特征在于,包括权利要求1-7中任一项所述的半导体器件。

14.根据权利要求13所述的存储器,其特征在于,所述存储器为3d-nand存储器。

技术总结

本发明提供了一种半导体器件、半导体器件的制造方法及存储器;该半导体器件包括半导体衬底;位于所述半导体衬底上的堆叠结构,所述堆叠结构包括交替层叠的若干层绝缘层和若干层导电层;至少部分所述绝缘层中设置有气隙;垂直于所述半导体衬底设置的沟道孔,所述沟道孔贯穿所述堆叠结构;贯穿所述堆叠结构的隔离沟槽,所述隔离沟槽垂直于所述半导体衬底。本发明在半导体器件中引入气隙,从而降低字线与字线之间的电容耦合,提升半导体器件的性能。

技术研发人员:郭帅

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!