功率器件及其制备方法、电子设备与流程

本发明涉及半导体,特别涉及一种功率器件及其制备方法、电子设备。

背景技术:

1、目前,在制备功率器件的过程中,衬底进行外延生长的时候,通常是把多个衬底放入反应炉中一起生长,由于生长气体的化学反应产生的外延生长在反应炉内的各个衬底表面基本相同,因此生长出的外延片结构也是相同的,由此制备的功率器件的性能无法达到最优。

技术实现思路

1、本发明要解决的技术问题是为了克服现有技术中的缺陷,提供一种功率器件及其制备方法、电子设备。

2、本发明是通过下述技术方案来解决上述技术问题:

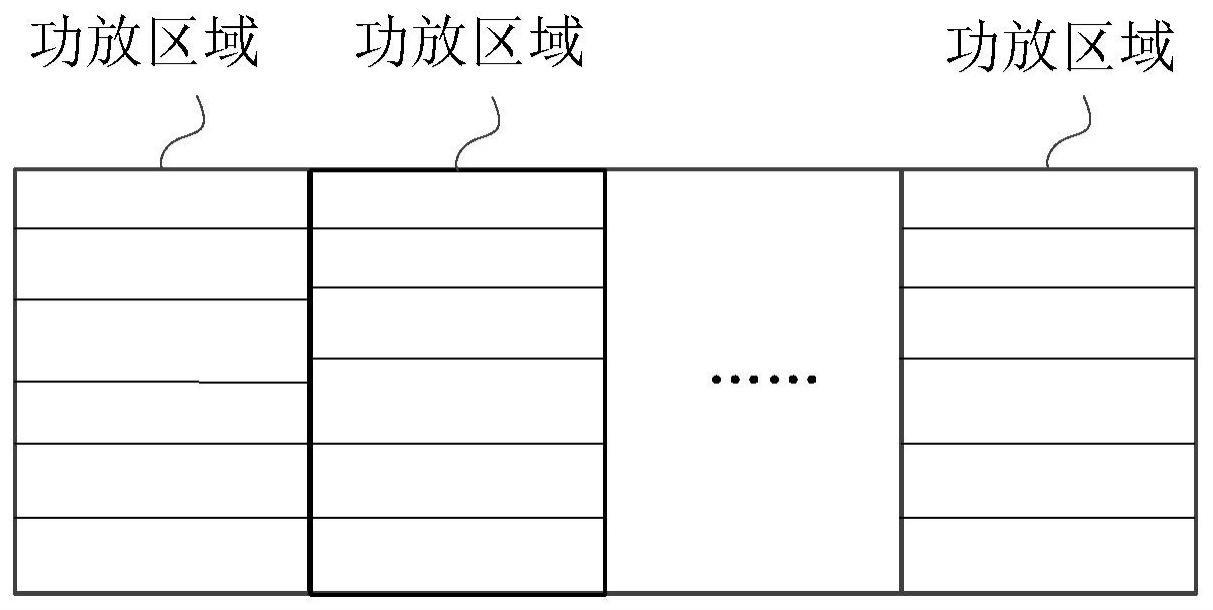

3、本发明的第一方面提供一种功率器件,所述功率器件的外延片包括至少两个功放区域,所述至少两个功放区域的垂直结构不同。

4、可选地,所述至少两个功放区域中位于相同位置的目标层的厚度不同。

5、可选地,所述至少两个功放区域中位于相同位置的目标层的掺杂浓度不同。

6、可选地,所述至少两个功放区域中位于相同位置的目标层的化学组分含量不同。

7、可选地,所述外延片采用hbt(heterojunction bipolar transistor,异质结双极晶体管)结构,所述功率器件为三级功放芯片,所述三级功放芯片包括级联的三个功放区域,所述三个功放区域分别为第一级功放区域、第二级功放区域和第三级功放区域;

8、所述第一级功放区域和所述第二级功放区域中集电极层和/或副集电极层的厚度均低于所述第三级功放区域中集电极层和/或副集电极层的厚度;和/或,

9、所述第一级功放区域和所述第二级功放区域中集电极层和/或副集电极层的掺杂浓度均低于所述第三级功放区域中集电极层和/或副集电极层的掺杂浓度。

10、可选地,所述外延片采用hbt结构,所述功率器件为合成功放芯片,所述合成功放芯片包括两个功放区域,所述两个功放区域分别为载波功放区域和峰值功放区域;

11、所述载波功放区域中集电极层和/或副集电极层的厚度低于所述峰值功放区域中集电极层和/或副集电极层的厚度;和/或,

12、所述载波功放区域中集电极层和/或副集电极层的掺杂浓度低于所述峰值功放区域中集电极层和/或副集电极层的掺杂浓度;和/或,

13、所述载波功放区域中发射极层的厚度低于所述峰值功放区域中发射极层的厚度;和/或,

14、所述载波功放区域中基极层的掺杂浓度高于所述峰值功放区域中基极层的掺杂浓度。

15、可选地,所述外延片采用phemt(pseudomorphic hemt,赝调制掺杂异质结场效应晶体管)结构,所述功率器件为三级功放芯片,所述三级功放芯片包括级联的三个功放区域,所述三个功放区域分别为第一级功放区域、第二级功放区域和第三级功放区域;

16、所述第一级功放区域和所述第二级功放区域中隔离层的厚度均低于所述第三级功放区域中隔离层的厚度;和/或,

17、所述第一级功放区域和所述第二级功放区域中δ掺杂施主层的掺杂浓度均高于所述第三级功放区域中δ掺杂施主层的掺杂浓度;和/或,

18、所述第一级功放区域和所述第二级功放区域中隔离层的目标化学组分含量均低于所述第三级功放区域中隔离层的目标化学组分含量。

19、可选地,所述外延片采用phemt结构,所述功率器件为合成功放芯片,所述合成功放芯片包括两个功放区域,所述两个功放区域分别为载波功放区域和峰值功放区域;

20、所述载波功放区域中隔离层的厚度低于所述峰值功放区域中隔离层的厚度;和/或,

21、所述载波功放区域中δ掺杂施主层的掺杂浓度高于所述峰值功放区域中δ掺杂施主层的掺杂浓度;和/或,

22、所述载波功放区域中隔离层的目标化学组分含量低于所述峰值功放区域中隔离层的目标化学组分含量。

23、本发明的第二方面提供一种功率器件的制备方法,所述功率器件为如第一方面所述的功率器件;所述制备方法包括以下步骤:

24、提供衬底;

25、在所述衬底上外延生长并注入掺杂,形成所述至少两个功放区域;

26、其中,在外延生长和/或注入掺杂的过程中,插入预设的掩膜版,以使阻挡的图形区域无法继续外延生长和/或注入掺杂。

27、本发明的第三方面提供一种电子设备,包括如第一方面所述的功率器件。

28、本发明的积极进步效果在于:功率器件中至少两个功放区域的垂直结构不同,使得至少两个功放区域的性能不同,例如增益、启动阈值、可靠性、饱和功率p-1等性能不同。具体地,通过分别对不同功放区域的垂直结构进行定制可以达到提高功放区域性能的目的,进而可以提高功率器件的性能。

技术特征:

1.一种功率器件,其特征在于,所述功率器件的外延片包括至少两个功放区域,所述至少两个功放区域的垂直结构不同。

2.如权利要求1所述的功率器件,其特征在于,所述至少两个功放区域中位于相同位置的目标层的厚度不同。

3.如权利要求1所述的功率器件,其特征在于,所述至少两个功放区域中位于相同位置的目标层的掺杂浓度不同。

4.如权利要求1所述的功率器件,其特征在于,所述至少两个功放区域中位于相同位置的目标层的化学组分含量不同。

5.如权利要求1所述的功率器件,其特征在于,所述外延片采用hbt结构,所述功率器件为三级功放芯片,所述三级功放芯片包括级联的三个功放区域,所述三个功放区域分别为第一级功放区域、第二级功放区域和第三级功放区域;

6.如权利要求1所述的功率器件,其特征在于,所述外延片采用hbt结构,所述功率器件为合成功放芯片,所述合成功放芯片包括两个功放区域,所述两个功放区域分别为载波功放区域和峰值功放区域;

7.如权利要求1所述的功率器件,其特征在于,所述外延片采用phemt结构,所述功率器件为三级功放芯片,所述三级功放芯片包括级联的三个功放区域,所述三个功放区域分别为第一级功放区域、第二级功放区域和第三级功放区域;

8.如权利要求1所述的功率器件,其特征在于,所述外延片采用phemt结构,所述功率器件为合成功放芯片,所述合成功放芯片包括两个功放区域,所述两个功放区域分别为载波功放区域和峰值功放区域;

9.一种功率器件的制备方法,其特征在于,所述功率器件为如权利要求1-8中任一项所述的功率器件;所述制备方法包括以下步骤:

10.一种电子设备,其特征在于,包括如权利要求1-8中任一项所述的功率器件。

技术总结

本发明公开了一种功率器件及其制备方法、电子设备。其中,所述功率器件的外延片包括至少两个功放区域,所述至少两个功放区域的垂直结构不同。本发明中,功率器件中至少两个功放区域的垂直结构不同,使得至少两个功放区域的性能不同,例如增益、启动阈值、可靠性、饱和功率P‑1等性能不同。具体地,通过分别对不同功放区域的垂直结构进行定制可以达到提高功放区域性能的目的,进而可以提高功率器件的性能。

技术研发人员:殷玉喆,刘伟,何力,黄永锋

受保护的技术使用者:成都挚信电子技术有限责任公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!