半导体超结功率器件的制作方法

本发明属于半导体功率器件,特别是涉及一种半导体超结功率器件。

背景技术:

1、半导体超结功率器件是基于电荷平衡技术,可以降低导通电阻和寄生电容,使得半导体超结功率器件具有极快的开关特性,可以降低开关损耗,实现更高的功率转换效率。现有技术的半导体超结功率器件在开启和关断时,栅漏电容(cgd)会发生突变,这使得半导体超结功率器件的栅极电压震荡严重。

技术实现思路

1、有鉴于此,本发明的目的是提供一种半导体超结功率器件,以解决现有技术中的半导体超结功率器件的栅漏电容突变问题。

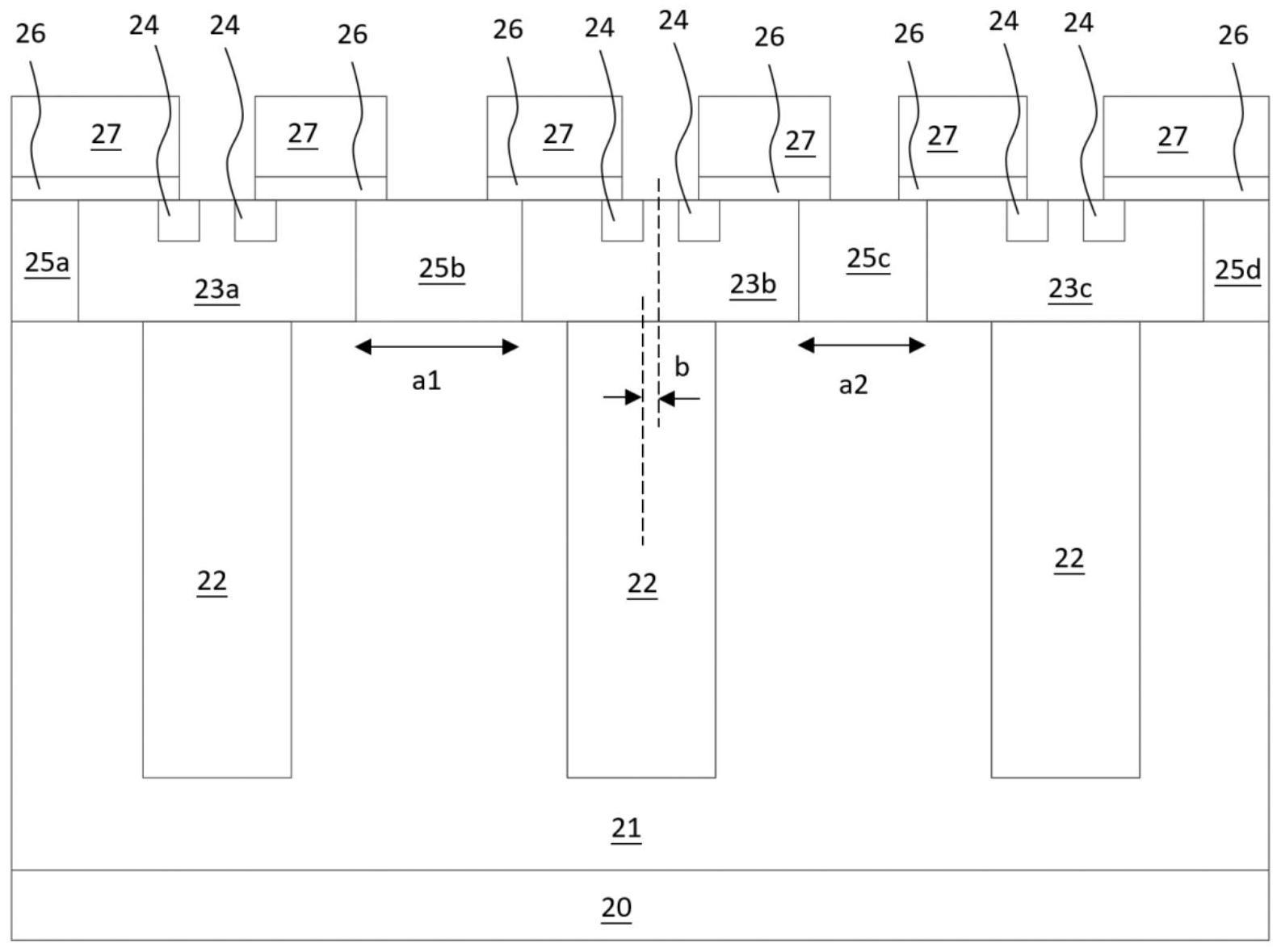

2、本发明实施例提供的一种半导体超结功率器件,包括终端区和元胞区,所述元胞区包括:

3、n型漏区、n型漂移区和多个p型柱,所述多个p型柱中的每个p型柱的宽度相等,且相邻的两个所述p型柱之间的间距相等;

4、所述多个p型柱中的每个所述p型柱的顶部分别设有与所述p型柱一一对应的p型体区,所述p型体区的宽度均相等;

5、所述p型体区内设有n型源区,控制所述n型源区与所述n型漂移区之间的电流沟道的开启和关断的栅极结构;

6、位于所述n型漂移区上方且介于相邻的所述p型体区之间的jfet区,所述jfet区设有两种或两种以上的不同宽度。

7、可选的,所述jfet区的宽度依次设为:c、c+1d、c、c+1d、c、…;或者依次设为:c、c+1d、…、c+nd、c+(n-1)d、…、c、c+1d、…、c+nd、c+(n-1)d、…、c、…;或者依次设为:c、c、…、c+1d、c+1d、…、c+nd、c+nd、…、c+(n-1)d、c+(n-1)d、…、c、c、…,其中:n≥2且n为整数,c为jfet区的基本宽度且c>0;d为jfet区的变化的宽度且d>0。

8、可选的,所述栅极结构包括覆盖电流沟道区和所述jfet区的栅介质层,以及位于所述栅介质层之上的栅极。

9、可选的,所述栅极结构包括覆盖电流沟道区的栅介质层,以及位于所述栅介质层之上的栅极,所述栅极在所述jfet区上方断开。

10、本发明的一种半导体超结功率器件的元胞区内,采用两种或两种以上不同宽度的jfet区结构,能够使得半导体超结功率器件在开启或关断时的栅漏电容突变速度降低,减小了半导体超结功率器件的栅极电压震荡。

技术特征:

1.半导体超结功率器件,其特征在于,包括终端区和元胞区,所述元胞区包括:

2.根据权利要求1所述的半导体超结功率器件,其特征在于,所述jfet区的宽度依次设为:c、c+1d、c、c+1d、c、…;或者依次设为:c、c+1d、…、c+nd、c+(n-1)d、…、c、c+1d、…、c+nd、c+(n-1)d、…、c、…;或者依次设为:c、c、…、c+1d、c+1d、…、c+nd、c+nd、…、c+(n-1)d、c+(n-1)d、…、c、c、…,其中:n≥2且n为整数,c为jfet区的基本宽度且c>0;d为jfet区的变化的宽度且d>0。

3.根据权利要求1所述的半导体超结功率器件,其特征在于,所述栅极结构包括覆盖电流沟道区和所述jfet区的栅介质层,以及位于所述栅介质层之上的栅极。

4.根据权利要求1所述的半导体超结功率器件,其特征在于,所述栅极结构包括覆盖电流沟道区的栅介质层,以及位于所述栅介质层之上的栅极,所述栅极在所述jfet区上方断开。

技术总结

本发明实施例提供的一种半导体超结功率器件,包括n型漏区、n型漂移区、多个p型柱;所述多个p型柱中的每个p型柱的宽度相等,且相邻的两个所述p型柱之间的间距相等;所述多个p型柱中的每个所述p型柱的顶部分别设有与所述p型柱一一对应的p型体区,所述p型体区的宽度均相等;所述p型体区内设有n型源区,控制所述n型源区与所述n型漂移区之间的电流沟道的开启和关断的栅极结构;位于所述n型漂移区上方且介于相邻的所述p型体区之间的JFET区,所述JFET区设有两种或两种以上的不同宽度。本发明可以使得半导体超结功率器件在开启或关断时的栅漏电容突变速度降低,减小半导体超结功率器件的栅极电压震荡。

技术研发人员:刘伟,刘磊,袁愿林,王睿

受保护的技术使用者:苏州东微半导体股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!