半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、随着集成电路制造技术的不断发展,人们对集成电路的集成度和性能的要求变得越来越高。为了提高集成度,降低成本,元器件的关键尺寸不断变小,集成电路内部的电路密度越来越大,这种发展使得晶圆表面无法提供足够的面积来制作所需要的互连线。

2、为了满足关键尺寸缩小过后的互连线所需,目前不同金属层或者金属层与衬底的导通是通过互连结构实现的。随着技术节点的推进,互连结构的尺寸也变得越来越小;相应的,形成互连结构的工艺难度也越来越大,而互连结构的形成质量对后段(back end ofline,beol)电学性能以及器件可靠性的影响很大,严重时会影响半导体器件的正常工作。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法,有利于提高半导体结构的性能。

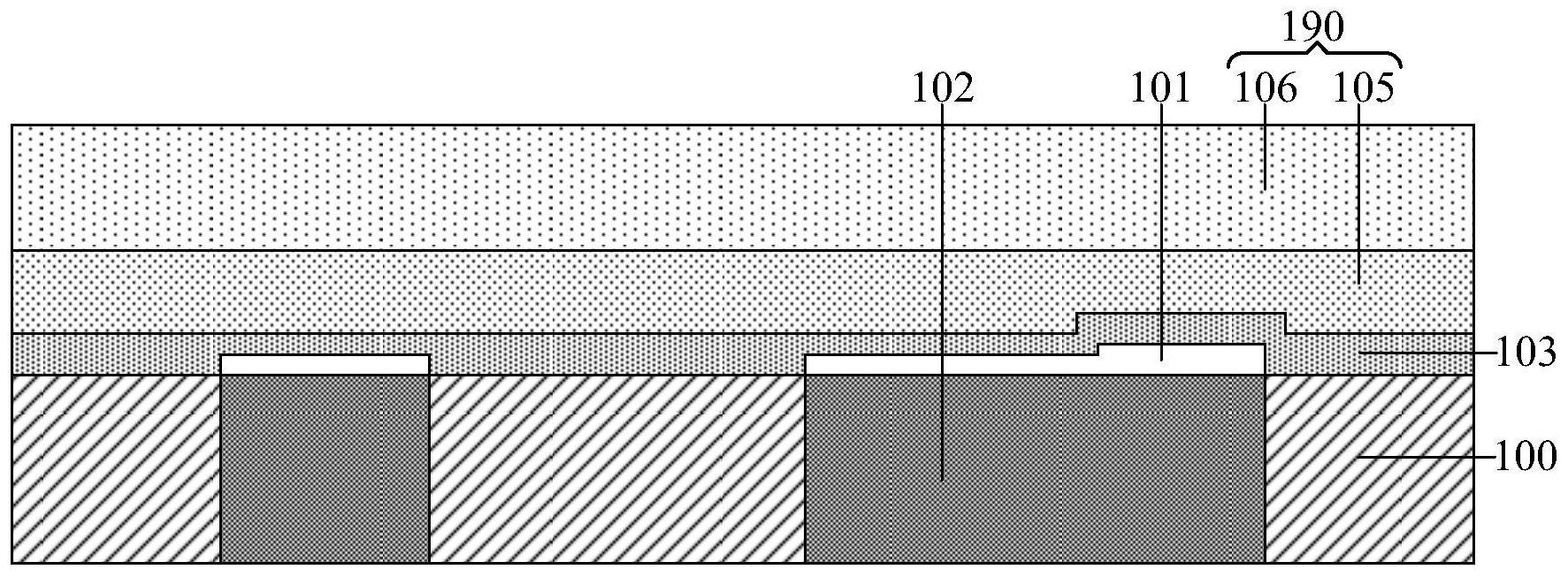

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底,所述基底包括第一介电层;第一互连结构,位于所述第一介电层中,且贯穿所述第一介电层;盖帽层,位于所述第一互连结构的顶部,且所述盖帽层露出所述第一互连结构的部分顶部;应力缓冲层,位于所述第一介电层和盖帽层的顶部;第二介电层,位于所述应力缓冲层的顶部;第二互连结构,位于所述盖帽层露出的所述第一互连结构的顶部,且所述第二互连结构贯穿所述第二介电层和缓冲层,所述第二互连结构的底部与所述第一互连结构的顶部电连接。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底,所述基底包括第一介电层,所述第一介电层中形成有贯穿所述第一介电层的第一互连结构;在所述第一互连结构的顶部形成盖帽层;形成所述盖帽层之后,在所述第一介电层和盖帽层的顶部形成应力缓冲层;在所述应力缓冲层的顶部形成第二介电层;形成所述第二介电层之后,在所述第一互连结构的顶部形成贯穿所述第二介电层、应力缓冲层和盖帽层的第二互连结构,所述第二互连结构的底部与所述第一互连结构的顶部电连接。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供一种半导体结构的形成方法,在所述第一互连结构的顶部形成盖帽层之后,在所述第一介电层和盖帽层的顶部形成应力缓冲层,然后在所述应力缓冲层的顶部形成第二介电层,使得所述应力缓冲层位于所述第一互连结构和盖帽层、以及所述第二介电层之间,在后续形成所述第二介电层的工艺制程中会使用到退火工艺,通过在所述第一互连结构和盖帽层、以及所述第二介电层之间形成应力缓冲层,所述应力缓冲层能够释放或者抵消所述第一互连结构和盖帽层、与所述第二介电层之间产生的热应力,从而对所述第一互连结构和盖帽层、与所述第二介电层之间产生的热应力起到缓冲作用,相应的,降低了所述第一互连结构和盖帽层、与所述第二介电层之间出现分层或者出现空隙的概率,进而提高了所述半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述第二介电层包括刻蚀停止层、以及位于所述刻蚀停止层顶部的金属层间介电层。

3.如权利要求1所述的半导体结构,其特征在于,所述第二互连结构包括第一子互连结构和第二子互连结构,所述第一子互连结构的顶部与所述第二子互连结构的底部相连,所述第一子互连结构的顶部线宽尺寸小于所述第二子互连结构的底部线宽尺寸。

4.如权利要求1所述的半导体结构,其特征在于,所述应力缓冲层的材料热膨胀系数,介于所述第二介电层的材料热膨胀系数和所述盖帽层的材料热膨胀系数之间,且还介于所述第二介电层的材料热膨胀系数和所述第一互连结构的材料热膨胀系数之间。

5.如权利要求1所述的半导体结构,其特征在于,所述应力缓冲层底部材料的热膨胀系数更接近所述盖帽层和第一互连结构材料的热膨胀系数,所述应力缓冲层顶部材料的热膨胀系数更接近所述第一介电层材料的热膨胀系数。

6.如权利要求5所述的半导体结构,其特征在于,所述应力缓冲层的材料中含有金属元素和非金属元素,且沿所述应力缓冲层的底部指向顶部的方向上,所述金属元素和非金属元素的原子含量比值线性降低。

7.如权利要求1所述的半导体结构,其特征在于,所述应力缓冲层材料的热膨胀系数介于3.0x10-6/k至9.8x10-6/k之间。

8.如权利要求1所述的半导体结构,其特征在于,所述应力缓冲层的材料包括aln、al2o3、tio2和zno2中的一种或多种。

9.如权利要求1所述的半导体结构,其特征在于,所述应力缓冲层的厚度为1纳米至3纳米。

10.如权利要求2所述的半导体结构,其特征在于,所述刻蚀停止层的材料包括sicn、sioc、sin、sion、aln和ai2o3中的一种或多种;所述第二介电层的材料包括sio2、sin、sichn、sicn和sion中的一种或多种。

11.如权利要求1所述的半导体结构,其特征在于,所述第一互连结构的材料包括cu、co和ru中的一种或多种。

12.如权利要求1所述的半导体结构,其特征在于,所述盖帽层的材料包括co、ru、cow和w中的一种或多种。

13.一种半导体结构的形成方法,其特征在于,包括:

14.如权利要求13所述的半导体结构的形成方法,其特征在于,所述应力缓冲层的材料热膨胀系数,介于所述第二介电层的材料热膨胀系数和所述盖帽层的材料热膨胀系数之间,且还介于所述第二介电层的材料热膨胀系数和所述第一互连结构的材料热膨胀系数之间。

15.如权利要求13所述的半导体结构的形成方法,其特征在于,所述应力缓冲层底部材料的热膨胀系数更接近所述盖帽层和第一互连结构材料的热膨胀系数,所述应力缓冲层顶部材料的热膨胀系数更接近所述第二介电层材料的热膨胀系数。

16.如权利要求15所述的半导体结构的形成方法,其特征在于,所述应力缓冲层的材料中含有金属元素和非金属元素,且沿所述应力缓冲层的底部指向顶部的方向上,所述金属元素和非金属元素的原子含量比值线性降低。

17.如权利要求16所述的半导体结构的形成方法,其特征在于,采用沉积工艺形成所述应力缓冲层,所述沉积工艺的反应气体包括用于提供金属元素的第一反应气体、以及用于提供非金属元素的第二反应气体,且在沉积的过程中,所述第二反应气体和第一反应气体的气体流量的比值随沉积时间递增。

18.如权利要求13或17所述的半导体结构的形成方法,其特征在于,采用原子层沉积工艺或化学气相沉积工艺形成所述应力缓冲层。

19.如权利要求13所述的半导体结构的形成方法,其特征在于,在所述应力缓冲层的顶部形成第二介电层的步骤包括:在所述应力缓冲层的顶部形成刻蚀停止层;在所述刻蚀停止层的顶部形成金属层间介电层,所述金属层间介电层和所述刻蚀停止层构成所述第二介电层。

20.如权利要求13所述的半导体结构的形成方法,其特征在于,在所述第一互连结构的顶部形成盖帽层的工艺包括选择性沉积工艺。

技术总结

一种半导体结构及其形成方法,方法包括:提供基底,所述基底包括第一介电层,所述第一介电层中形成有贯穿所述第一介电层的第一互连结构;在所述第一互连结构的顶部形成盖帽层;形成所述盖帽层之后,在所述第一介电层和盖帽层的顶部形成应力缓冲层;在所述应力缓冲层的顶部形成第二介电层;形成所述第二介电层之后,在所述第一互连结构的顶部形成贯穿所述第二介电层、应力缓冲层和盖帽层的第二互连结构,所述第二互连结构的底部与所述第一互连结构的顶部电连接。所述应力缓冲层降低了所述第一互连结构和盖帽层、与所述第二介电层之间出现分层或者出现空隙的概率,进而提高了所述半导体结构的性能。

技术研发人员:刘继全

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!