晶体管单元及其阵列、集成电路的制作方法

本公开涉及半导体,尤其涉及一种晶体管单元及其阵列、集成电路。

背景技术:

1、当静电放电(esd,electro static discharge)产生的放电电流在集成电路内流过时,会产生局部发热或电场集中的情况,由此会破坏集成电路,导致集成电路失效。因此,为了防止esd造成的破坏,一般在集成电路的输入/输出接口(i/o)与内部核心电路之间设置esd保护元件。其中,金属氧化物半导体场效应晶体管(mosfet,metal oxidesemiconductor field effect transistor)元件通常用于集成电路中的esd保护,能够将相应的esd放电电流泄放至地,避免损坏所涉及的集成电路中的半导体器件和/或金属互连。

2、然而,相关技术中,用于esd保护的晶体管元件存在放电能力有限,集成度较低的问题。

3、公开内容

4、本公开实施例提出一种晶体管单元及其阵列、集成电路。

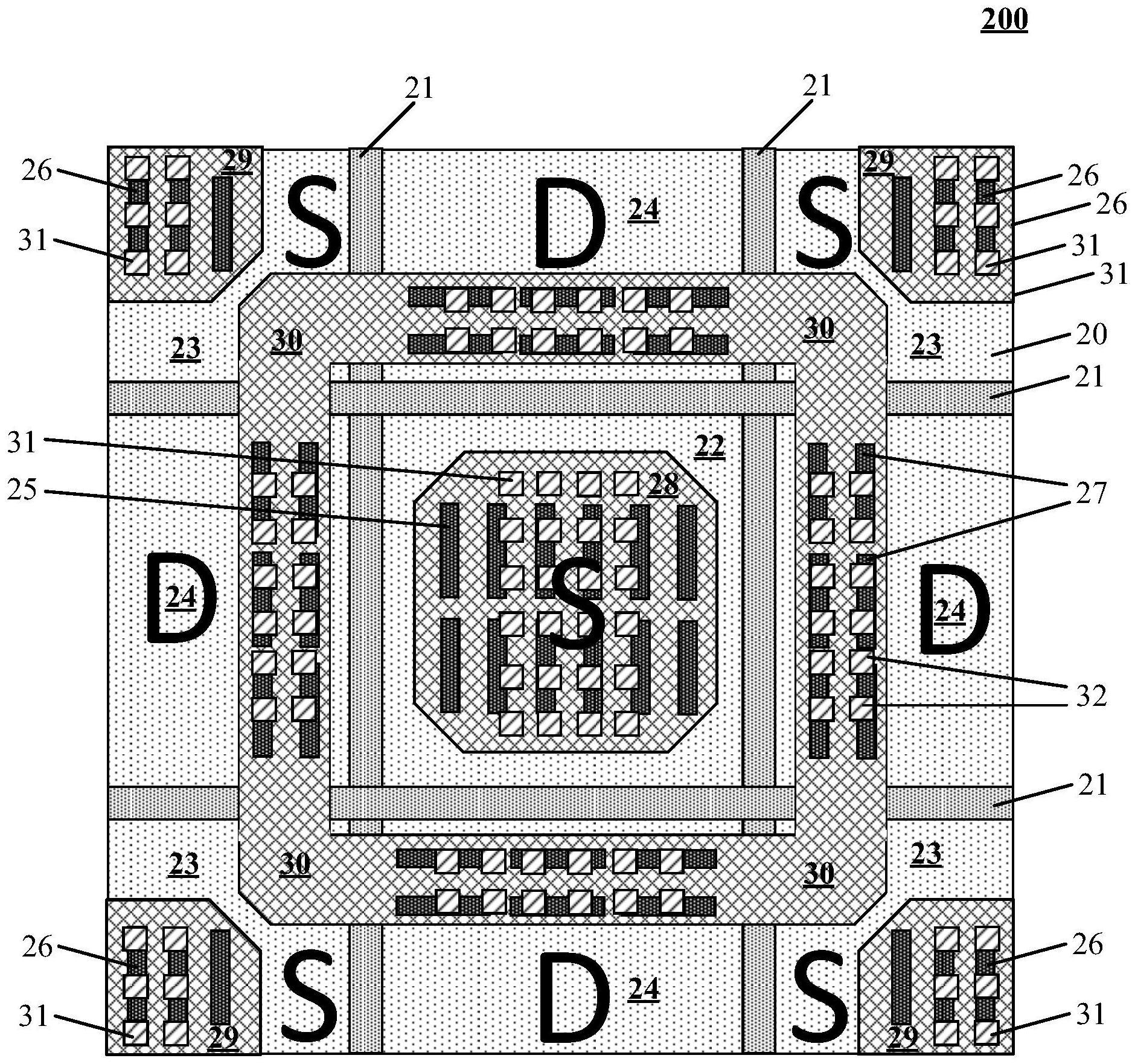

5、本公开实施例提供了一种晶体管单元,包括:

6、衬底;

7、n条栅极,均位于衬底上;n条栅极在衬底表面的投影形成封闭的形状;n为大于2的正整数;

8、第一源区,位于衬底中且在衬底表面的投影位于所述封闭的形状中;所述第一源区被所述n条栅极共用;

9、n个漏区,位于衬底中;n个漏区中的每个均和所述第一源区分居所述n条栅极中相应栅极的两侧;

10、多个第一源端导电插栓,位于所述第一源区上并与所述第一源区电接触;

11、每个所述漏区上设置有多个漏端导电插栓且所述漏端导电插栓与所述漏区电接触;

12、第一源端金属层,位于所述第一源端导电插栓上并与所有的所述第一源端导电插栓电接触;

13、漏端金属层,位于所述漏端导电插栓上并与所有的所述漏端导电插栓电接触。

14、上述方案中,所述晶体管单元还包括:

15、n个第二源区、第二源端导电插栓,以及n个第二源端金属层;其中,

16、所述n个第二源区位于所述衬底中;所述n个第二源区中的每个在所述衬底表面的投影均位于所述封闭的形状外,且与所述漏区分居相应栅极的两侧;

17、位于每个所述第二源区上设置有多个所述第二源端导电插栓且所述第二源端导电插栓与所述第二源区电接触;

18、所述n个第二源端金属层中的每个分别位于n个第二源区中相应第二源区上,并与相应第二源区上的所有第二源端导电插栓电接触。

19、上述方案中,所述n为3、4、5或者6。

20、上述方案中,n=4。

21、上述方案中,所述n条栅极在衬底表面的投影形成的封闭形状为正方形。

22、上述方案中,所述n个第二源区的面积之和等于所述第一源区的面积。

23、上述方案中,所述第一源端导电插栓沿平行于n条栅极中任一栅极的方向相互间隔地对齐排布,构成平行于任一栅极的m个第一源端导电插栓排;

24、针对所述n个第二源区中的每个第二源区,多个第二源端导电插栓沿平行于相应栅极方向相互间隔地对齐排布,构成平行于相应栅极的k个第二源端导电插栓排;

25、针对所述n个漏区每个漏区,多个漏端导电插栓沿平行于相应栅极方向相互间隔地对齐排布,构成平行于相应栅极的p个漏端导电插栓排;

26、其中,m.k.p均为正整数。

27、上述方案中,所述第一源区上第一源端导电插栓的总数量与所述n个第二源区上第二源端导电插栓的总数量相同。

28、上述方案中,所述第一源端导电插栓.所述第二源端导电插栓及所述漏端导电插栓的形状.尺寸均相同。

29、上述方案中,所述第一源端导电插栓.所述第二源端导电插栓及所述漏端导电插栓在衬底表面的正投影均为长条状。

30、上述方案中,所述晶体管还包括多个源端接触,分别位于所述第一源端金属层和所述第二源端金属层上并分别与所述第一源端金属层电接触或所述第二源端金属层电接触;

31、所述晶体管还包括漏端接触,位于所述漏端金属层上并与所述漏端金属层电接触。

32、上述方案中,所述源端接触和所述漏端接触在衬底表面的投影均呈点状分布。

33、上述方案中,所述第一源区在所述衬底所在平面上的正投影覆盖所述第一源端金属层在所述衬底所在平面上正投影;

34、漏端金属层在衬底所在平面上的正投影环绕所述第一源端金属层在所述衬底所在平面上正投影。

35、上述方案中,所述第一源端金属层和所述漏端金属层的几何中心线重合。

36、本公开实施例又提供了一种晶体管单元阵列,包括多个本公开实施例提供的所述的晶体管单元;多个所述晶体管单元呈阵列排布。

37、上述方案中,两个相邻所述晶体管单元的漏区电连接;两个相邻所述晶体管单元的第二源区电连接。

38、本公开实施例又提供了一种集成电路,包括本公开实施例提供的所述的晶体管单元阵列。

39、本公开实施例公开了一种晶体管单元及其阵列、集成电路。其中,所述晶体管单元,包括:衬底;n条栅极,均位于衬底上;n条栅极在衬底表面的投影形成封闭的形状;n为大于2的正整数;第一源区,位于衬底中且在衬底表面的投影位于所述封闭的形状中;所述第一源区被所述n条栅极共用;n个漏区,位于衬底中;n个漏区中的每个均和所述第一源区分居所述n条栅极中相应栅极的两侧;多个第一源端导电插栓,位于所述第一源区上并与所述第一源区电接触;每个所述漏区上设置有多个漏端导电插栓且所述漏端导电插栓与所述漏区电接触;第一源端金属层,位于第一源端导电插栓上并与所有的第一源端导电插栓电接触;漏端金属层,位于漏端导电插栓上并与所有的漏端导电插栓电接触。本公开实施例中,通过将多个晶体管的源极极连接在一起并将该多个晶体管的栅极接成一个封闭的形状的标准单元。可以理解的是,源极的共用使得本公开实施例提供的晶体管单元占用面积较小;同时,共用的源极区域可以提供较大的面积来设置较多的源端导电插栓,较多的源端导电插栓使得本公开实施例提供的晶体管单元的泄放电流的能力较强。

技术实现思路

技术特征:

1.一种晶体管单元,其特征在于,包括:

2.根据权利要求1所述的晶体管单元,其特征在于,所述晶体管单元还包括:n个第二源区、第二源端导电插栓,以及n个第二源端金属层;其中,

3.根据权利要求2所述的晶体管单元,其特征在于,所述n为3、4、5或者6。

4.根据权利要求3所述的晶体管单元,其特征在于,n=4。

5.根据权利要求4所述的晶体管单元,其特征在于,所述n条栅极在衬底表面的投影形成的封闭形状为正方形。

6.根据权利要求2-5任一项所述的晶体管单元,其特征在于,所述n个第二源区的面积之和等于所述第一源区的面积。

7.根据权利要求2所述的晶体管单元,其特征在于,

8.根据权利要求2所述的晶体管单元,其特征在于,所述第一源区上第一源端导电插栓的总数量与所述n个第二源区上第二源端导电插栓的总数量相同。

9.根据权利要求2所述的晶体管单元,其特征在于,所述第一源端导电插栓、所述第二源端导电插栓及所述漏端导电插栓的形状、尺寸均相同。

10.根据权利要求9所述的晶体管单元,其特征在于,所述第一源端导电插栓、所述第二源端导电插栓及所述漏端导电插栓在衬底表面的正投影均为长条状。

11.根据权利要求2所述的晶体管单元,其特征在于,

12.根据权利要求11所述的晶体管单元,其特征在于,所述源端接触和所述漏端接触在衬底表面的投影呈点状分布。

13.根据权利要求1所述的晶体管单元,其特征在于,所述第一源区在所述衬底所在平面上的正投影覆盖所述第一源端金属层在所述衬底所在平面上正投影;

14.根据权利要求1所述的晶体管单元,其特征在于,所述第一源端金属层和所述漏端金属层的几何中心线重合。

15.一种晶体管单元阵列,其特征在于,包括多个权利要求1至14中任一项所述的晶体管单元;多个所述晶体管单元呈阵列排布。

16.根据权利要求15所述的晶体管单元阵列,其特征在于,两个相邻所述晶体管单元的漏区电连接;两个相邻所述晶体管单元的第二源区电连接。

17.一种集成电路,其特征在于,包括权利要求15或16所述的晶体管单元阵列。

技术总结

本公开实施例公开了一种晶体管单元及其阵列、集成电路。其中,晶体管单元包括:衬底;N条栅极,均位于衬底上;N条栅极在衬底表面的投影形成封闭的形状;N为大于2的正整数;第一源区;位于衬底中,且第一源区在衬底表面的投影位于封闭的形状中;第一源区被N条栅极共用;N个漏区;位于衬底中,且N个漏区中的每个漏区均和源区分居N条栅极中相应栅极的两侧;多个第一源端导电插栓,位于第一源区上,并与第一源区电接触;每个漏区设置有多个漏端导电插栓,且多个漏端导电插栓与漏区电接触;第一源端金属层,位于第一源端导电插栓上,并与所有的第一源端导电插栓电接触;漏端金属层,位于漏端导电插栓上,并与所有的漏端导电插栓电接触。

技术研发人员:王宇哲,李新

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!