半导体结构及其形成方法与流程

本发明涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、在数字模块级设计中,需要引入电容元件。这些电容会被连接在电源导电层(vss/vdd),用来实现稳压滤波的功能。通常这些电容单元会在模块级逻辑功能的布局布线完成后,通过软件自动填充进模块的空隙之中。

2、在现有技术中,需要单独设计电容元件的半导体结构,且电容的调节只能是电容元件的电容值的整数倍。

3、然而,在上述方法中,随着节点尺寸的减小,单独电容元件半导体结构变得难以实现。

技术实现思路

1、本发明解决的技术问题是一种半导体结构及其形成方法,仅需要通过增加导电插塞,把电源导电层与已经存在的冗余金属电连接,就能调整整个半导体结构的电容值,并且通过电连接的冗余金属的面积来控制整个电路的电容值。

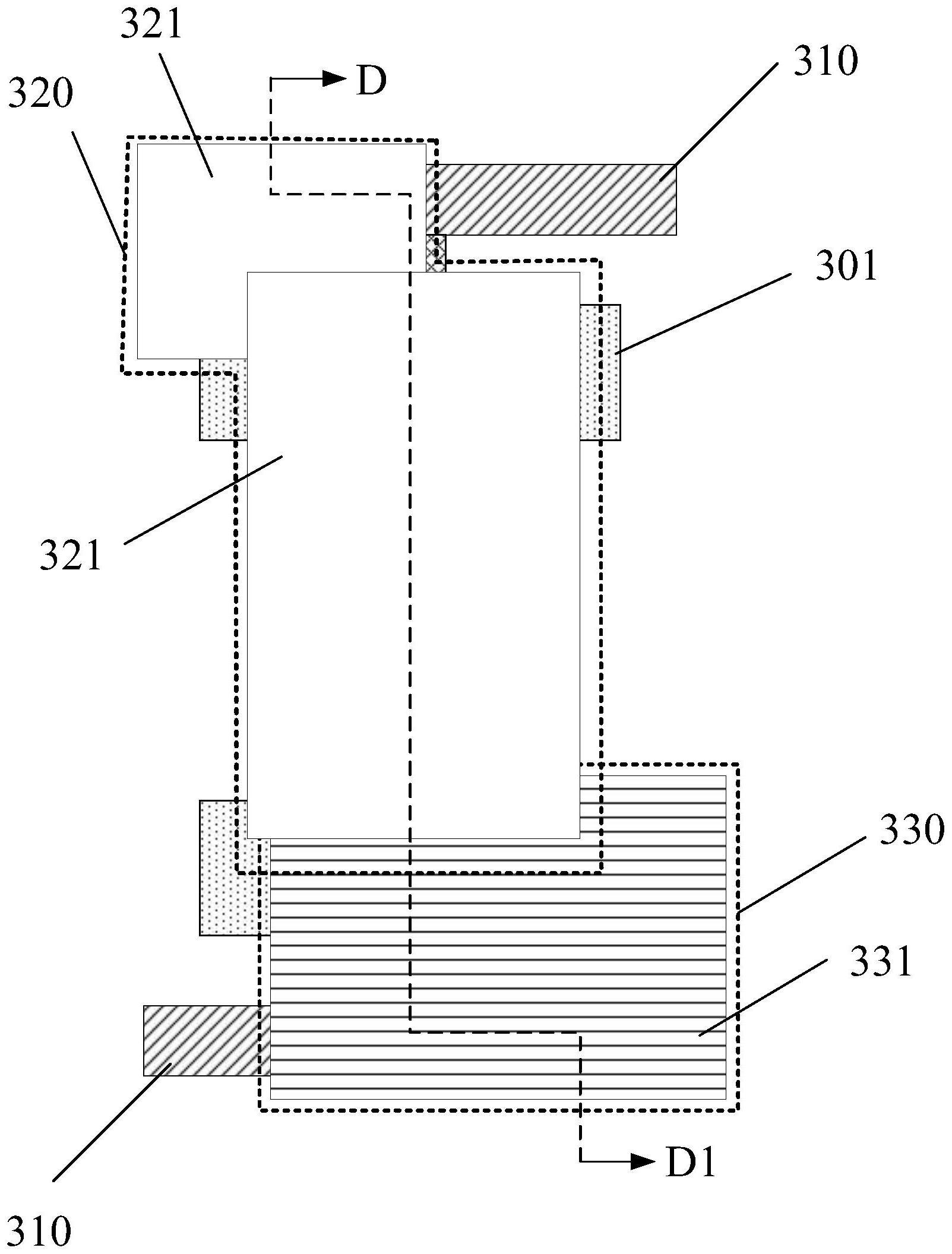

2、为解决上述技术问题,本发明的技术方案提供一种半导体结构,包括:衬底,所述衬底包括若干单元区;位于所述单元区上的至少2个电源导电层;位于所述电源导电层上的第一导电结构以及第二导电结构,所述第一导电结构与所述第二导电结构相互分立,所述第一导电结构通过第一导电插塞与电源导电层电连接,所述第二导电结构通过第二导电插塞与电源导电层电连接。

3、可选的,所述第一导电结构包括至少一层第一导电层,所述第一导电层的材料包括:金属。

4、可选的,当所述第一导电层的数量大于1时,相邻两层所述第一导电层之间均具有第一导电插塞。

5、可选的,还包括:与至少一层所述第一导电层位于同一层的若干第一互连层,所述第一互连层的材料包括:金属。

6、可选的,所述第二导电结构包括至少一层第二导电层,所述第二导电层的材料包括:金属。

7、可选的,当所述第二导电层的数量大于1时,相邻两层所述第二导电层之间均具有第二导电插塞。

8、可选的,当所述第一导电层的数量大于1且所述第二导电层的数量大于或等于1时,或者当所述第二导电层的数量大于1且所述第一导电层的数量大于或等于1时,所述第一导电结构在所述衬底上的投影图形与所述第二导电结构在所述衬底上的投影图形重叠。

9、可选的,还包括:与至少一层所述第二导电层位于同一层的若干第二互连层,所述第二互连层的材料包括:金属。

10、可选的,还包括:位于所述单元区上的栅极结构。

11、可选的,还包括:位于衬底上的第四介质层;位于所述第四介质层上的第一介质层,所述电源导电层位于所述第一介质层内;位于所述第一介质层上的第二介质层,至少部分所述第一导电插塞位于所述第二介质层内,至少部分所述第二导电插塞位于所述第二介质层内;位于所述第二介质层上的第三介质层,所述第一导电结构和所述第二导电结构位于所述第三介质层内。

12、相应的,本发明的技术方案还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括若干单元区;在所述单元区上形成至少2个电源导电层;在所述电源导电层上形成第一导电结构以及第二导电结构,所述第一导电结构与所述第二导电结构相互分立,所述第一导电结构通过第一导电插塞与电源导电层电连接,所述第二导电结构通过第二导电插塞与电源导电层电连接。

13、可选的,所述第一导电结构包括至少一层第一导电层,所述第一导电层的材料包括:金属。

14、可选的,当所述第一导电层的数量大于1时,相邻两层所述第一导电层之间均具有第二导电插塞。

15、可选的,当所述第一导电层的数量大于1且所述第二导电层的数量大于或等于1时,或者当所述第二导电层的数量大于1且所述第一导电层的数量大于或等于1时,所述第一导电结构在所述衬底上的投影图形与所述第二导电结构在所述衬底上的投影图形重叠。

16、可选的,还包括:在与至少一层所述第一导电层位于同一层内形成若干第一互连层,所述第一互连层的材料包括:金属。

17、可选的,所述第二导电结构包括至少一层第二导电层,所述第二导电层的材料包括:金属。

18、可选的,当所述第二导电层的数量大于1时,相邻两层所述第二导电层之间均具有第一导电插塞。

19、可选的,还包括:在与至少一层所述第二导电层位于同一层内形成若干第二互连层,所述第二互连层的材料包括:金属。

20、可选的,还包括:在所述单元区上形成栅极结构。

21、可选的,还包括:在衬底上形成第四介质层;在所述第四介质层上形成第一介质层,所述电源导电层位于所述第一介质层内;在所述第一介质层上形成第二介质层,至少部分所述第一导电插塞位于所述第二介质层内,至少部分所述第二导电插塞位于所述第二介质层内;在所述第二介质层上形成第三介质层,所述第一导电结构和所述第二导电结构位于所述第三介质层内。

22、与现有技术相比,本发明的技术方案具有以下有益效果:

23、本发明技术方案提供的一种半导体结构,第一导电结构通过第一导电插塞与电源导电层电连接,第二导电结构通过第二导电插塞与电源导电层电连接,并且所述第一导电结构与所述第二导电结构相互分立。由于所述第一导电结构和所述第二导电结构是为了增加金属密度、解决化学机械抛光过度抛光的问题原本就在所述半导体结构中存在的,不会造成额外面积增加。本发明技术方案实现容易,只需要通过在所述电源导电层与所述第一导电结构和所述第二导电结构之间增加所述第一导电插塞和所述第二导电插塞,就能调整所述半导体结构的电容值。

24、进一步,所述第一导电结构包括至少一层第一导电层,相邻两层所述第一导电层之间均具有所述第一导电插塞;所述第二导电结构包括至少一层第二导电层,相邻两层所述第二导电层之间均具有所述第二导电插塞。只要通过控制所述第一导电插塞和所述第二导电插塞的数量,就能调整所述第一导电结构和所述第二导电结构的总覆盖面积。由于金属的电容计算简单,金属的电容值与其面积成正比,因此只需要通过控制所述第一导电结构与所述第二导电结构的总覆盖面积,就能获得所需电容值的半导体结构。通过调整所述第一导电插塞和所述第二导电插塞的数量,就能控制所述半导体结构的电容值范围。因此,本发明技术方案的半导体结构的电容值调节范围大,其最小值为0ff,且向上数值连续可调。

25、相应的,本发明技术方案提供的一种半导体结构的形成方法,在电源导电层上形成第一导电结构以及第二导电结构,所述第一导电结构与所述第二导电结构相互分立,所述第一导电结构通过第一导电插塞与电源导电层电连接,所述第二导电结构通过第二导电插塞与电源导电层电连接。由于所述第一导电结构和所述第二导电结构是为了增加金属密度、解决化学机械抛光过度抛光的问题原本就在所述半导体结构中存在的,不会造成额外面积增加。本发明技术方案实现容易,只需要通过在所述电源导电层与所述第一导电结构和所述第二导电结构之间增加所述第一导电插塞和所述第二导电插塞,就能调整所述半导体结构的电容值。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述第一导电结构包括至少一层第一导电层,所述第一导电层的材料包括:金属。

3.如权利要求2所述的半导体结构,其特征在于,当所述第一导电层的数量大于1时,相邻两层所述第一导电层之间均具有第一导电插塞。

4.如权利要求2所述的半导体结构,其特征在于,还包括:与至少一层所述第一导电层位于同一层的若干第一互连层,所述第一互连层的材料包括:金属。

5.如权利要求2所述的半导体结构,其特征在于,所述第二导电结构包括至少一层第二导电层,所述第二导电层的材料包括:金属。

6.如权利要求5所述的半导体结构,其特征在于,当所述第二导电层的数量大于1时,相邻两层所述第二导电层之间均具有第二导电插塞。

7.如权利要求5所述的半导体结构,其特征在于,当所述第一导电层的数量大于1且所述第二导电层的数量大于或等于1时,或者当所述第二导电层的数量大于1且所述第一导电层的数量大于或等于1时,所述第一导电结构在所述衬底上的投影图形与所述第二导电结构在所述衬底上的投影图形重叠。

8.如权利要求5所述的半导体结构,其特征在于,还包括:与至少一层所述第二导电层位于同一层的若干第二互连层,所述第二互连层的材料包括:金属。

9.如权利要求1所述的半导体结构,其特征在于,还包括:位于所述单元区上的栅极结构。

10.如权利要求1所述的半导体结构,其特征在于,还包括:位于衬底上的第四介质层;位于所述第四介质层上的第一介质层,所述电源导电层位于所述第一介质层内;位于所述第一介质层上的第二介质层,至少部分所述第一导电插塞位于所述第二介质层内,至少部分所述第二导电插塞位于所述第二介质层内;位于所述第二介质层上的第三介质层,所述第一导电结构和所述第二导电结构位于所述第三介质层内。

11.一种半导体结构的形成方法,其特征在于,包括:

12.如权利要求11所述的半导体结构的形成方法,其特征在于,所述第一导电结构包括至少一层第一导电层,所述第一导电层的材料包括:金属。

13.如权利要求12所述的半导体结构的形成方法,其特征在于,当所述第一导电层的数量大于1时,相邻两层所述第一导电层之间均具有第一导电插塞。

14.如权利要求12所述的半导体结构的形成方法,其特征在于,还包括:在与至少一层所述第一导电层位于同一层内形成若干第一互连层,所述第一互连层的材料包括:金属。

15.如权利要求12所述的半导体结构的形成方法,其特征在于,所述第二导电结构包括至少一层第二导电层,所述第二导电层的材料包括:金属。

16.如权利要求15所述的半导体结构的形成方法,其特征在于,当所述第二导电层的数量大于1时,相邻两层所述第二导电层之间均具有第二导电插塞。

17.如权利要求15所述的半导体结构的形成方法,其特征在于,当所述第一导电层的数量大于1且所述第二导电层的数量大于或等于1时,或者当所述第二导电层的数量大于1且所述第一导电层的数量大于或等于1时,所述第一导电结构在所述衬底上的投影图形与所述第二导电结构在所述衬底上的投影图形重叠。

18.如权利要求15所述的半导体结构的形成方法,其特征在于,还包括:在与至少一层所述第二导电层位于同一层内形成若干第二互连层,所述第二互连层的材料包括:金属。

19.如权利要求11所述的半导体结构的形成方法,其特征在于,还包括:在所述单元区上形成栅极结构。

20.如权利要求11所述的半导体结构的形成方法,其特征在于,还包括:在衬底上形成第四介质层;在所述第四介质层上形成第一介质层,所述电源导电层位于所述第一介质层内;在所述第一介质层上形成第二介质层,至少部分所述第一导电插塞位于所述第二介质层内,至少部分所述第二导电插塞位于所述第二介质层内;在所述第二介质层上形成第三介质层,所述第一导电结构和所述第二导电结构位于所述第三介质层内。

技术总结

半导体结构及其形成方法,其中一种半导体结构,包括:衬底,所述衬底包括若干单元区;位于所述单元区上的至少2个电源导电层;位于所述电源导电层上的第一导电结构以及第二导电结构,所述第一导电结构与所述第二导电结构相互分立,所述第一导电结构通过第一导电插塞与电源导电层电连接,所述第二导电结构通过第二导电插塞与电源导电层电连接。仅需要通过增加所述第一导电插塞和所述第二导电插塞的数量,就能调整电容值。

技术研发人员:郁扬,蔡燕飞,王俊,张程,王代平

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!