裸片到裸片的互连电路中半导体组件、集成电路封装方法与流程

1.本发明涉及芯片封装技术领域,尤其涉及一种裸片到裸片的互连电路中半导体组件、集成电路封装方法。

背景技术:

2.随着进入后摩时代,chiplet成为一个越来越重要和广泛的解决方案,chiplet的概念其实很简单,就是硅片级别的重用,从系统端出发,首先将复杂功能进行分解,然后开发出多种具有单一特定功能、可相互进行模块化组装的裸芯片,如实现数据存储、计算、信号处理、数据流管理等功能,并最终以此为基础,建立一个chiplet的芯片网络。

3.chiplet里多颗芯片需要集成裸片到裸片(简称die-die)的互连电路,一般而言,该互连电路由集成电路和/或半导体器件组成,具体连接方式可以根据实际需求进行确定,不同实际情况下互连电路中所包含的具体元器件和元器件的具体连接方式不同,一个互连电路可以称为一个ip。chiplet通常采用多芯片模块(multi-chip module,简称mcm)、扇出封装(fanout package,简称fop)和芯片在晶圆在封装上(chip on wafer on package,简称cowos)等多种合封方式,不同封装方式所需要的连线宽度、线与线之间的距离、凸点或微凸点的尺寸以及两个相邻凸点球心之间的间距均不相同,这样需要多颗die-die互连ip来满足不同合封方式应用,影响芯片开发进度和开发成本。

技术实现要素:

4.本发明提供一种裸片到裸片的互连电路中半导体组件、集成电路封装方法,其主要目的在于在一个互连电路上实现多种不同的封装方式,提高芯片开发进度降低开发成本。

5.本发明实施例提供一种裸片到裸片的互连电路中半导体组件、集成电路封装方法,包括:

6.对于目标互连电路中的硬核中的任一模块,若所述任一模块使用cowos或fop封装,则所述任一模块在封装过程中使用微凸点,并且水平方向任意两个相邻微凸点之间的球心距离不小于40um。

7.优选地,竖直方向任意两个相邻微凸点之间的球心距离为80um。

8.优选地,所述任一模块传输52个信号,其中包括2个差分时钟信号。

9.优选地,采用单倍数据速率的传输模式,传输速率2.5gbps。

10.优选地,若所述任一模块使用mcm封装方式,则所述任一模块传输26个信号,在所述任一模块cowos或fop封装基础上,在所述任一模块上设置若干个锡球,所述锡球设置在对应微凸点上面,且所述锡球与对应微凸点中表示信号的微凸点通过再布线连接,并且,所述锡球的个数与所述任一模块中剩余表示信号的微凸点个数之和为26,所述任意两个锡球球心之间的距离为160um。

11.优选地,所述锡球为覆晶反扣焊法锡球。

12.优选地,所述任一模块中有2个差分时钟信号。

13.优选地,采用双倍数据速率的传输模式,传输速率5gbps。

14.优选地,所述任一模块由半导体组件构和/或集成电路构成。

15.本发明提出的一种裸片到裸片的互连电路中半导体组件、集成电路封装方法,对于同一个ip,可以在不改变ip结构的前提下,在该ip上实现cowos或fop封装,一个工艺只需要做一种die-die互连ip来满足不同封装方式,降低芯片开发进度以及开发成本。

附图说明

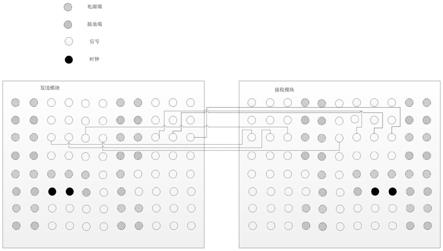

16.图1为本发明实施例中裸片到裸片的互连电路结构示意图;

17.图2为本发明实施例中采用cowos或fop封装的示意图;

18.图3为本发明实施例中采用mcm封装方式的示意图;

19.图4为本发明实施例中采用mcm封装方式时bump pitch示意图。

20.本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

21.应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

22.图1为本发明实施例中裸片到裸片的互连电路结构示意图,如图1所示,本发明实施例中,一个裸片包括多个ip,ip结构包括数字控制模块和硬核,硬核包括发送模块、io校准模块和接收模块,发送模块、io校准模块和接收模块均分别与数字控制模块连接,可以与数字模块之间进行通信。一般而言,数字控制模块由芯片设计项目开发集成,本发明实施例中针对的主要是硬核的封装方式。

23.需要说明的是,本发明实施例中数字控制模块和硬核,可以是单独由半导体组件构成的电路,也可以是集成电路裸片,也可以是由半导体组件和集成电路裸片组合而成。

24.图2为本发明实施例中采用cowos或fop封装的示意图,如图2所示,该方法包括:

25.对于目标互连电路中的硬核中的任一模块,若所述任一模块使用cowos或fop封装,则所述任一模块在封装过程中使用微凸点,并且水平方向任意两个相邻微凸点之间的球心距离不小于40um。

26.本发明实施例中以接收模块、发送模块为任一模块进行说明,图中表示发送模块和接收模块的采用cowos封装或fop封装的示意图,发送模块和接收模块上在焊接时使用的凸点为微凸点,微凸点即为图中的圈圈,共有4中含义,分别表示电源端、接地端、信号端和时钟信号端,其中,微凸点即为micro-bump,在水平方向上,任意两个相邻的微凸点球心之间的距离最小为40um,即micro-bump pitch为40um。只要满足该条件,就能对发送模块、接收模块进行cowos封装或fop封装。micro-bump pitch可以基于封装走线要求进行微调,以满足不同项目的规格要求。

27.还需要说明的是,cowos封装或fop封装是,图中连接两个微凸点之间的线的宽度、线和线之间的距离可以根据实际需要进行调整。

28.本发明提出的一种裸片到裸片的互连电路中半导体组件、集成电路封装方法,对于同一个ip,可以在不改变ip结构的前提下,在该ip上实现cowos或fop封装,一个工艺只需要做一种die-die互连ip来满足不同封装方式,降低芯片开发进度以及开发成本。

29.在上述实施例的基础上,优选地,竖直方向任意两个相邻微凸点之间的球心距离为80um。

30.在竖直方向上,任意两个相邻的微凸点之间的球心距离为80um。

31.在上述实施例的基础上,优选地,所述任一模块传输52个信号,其中包括2个差分时钟信号。

32.参考发送模块和接收模块,每个表示信号的微凸点传输一个信号,也就是图中接收模块或发送模块中白色圈圈,白色圈圈一共有52个,并且其中有2个微凸点表示差分时钟信号,也就是图中接收模块或发送模块中黑色圈圈。

33.在上述实施例的基础上,优选地,采用单倍数据速率的传输模式,传输速率2.5gbps。

34.具体地,模块在进行数据传输时采用单倍数据速率的传输模块,其传输速率是2.5gbps。

35.图3为本发明实施例中采用mcm封装方式的示意图,如图3所示,在上述实施例的基础上,优选地,若所述任一模块使用mcm封装方式,则所述任一模块传输26个信号,在所述任一模块cowos或fop封装基础上,在所述任一模块上设置若干个锡球,所述锡球设置在对应微凸点上面,且所述锡球与对应微凸点中表示信号的微凸点通过再布线连接,并且,所述锡球的个数与所述任一模块中剩余表示信号的微凸点个数之和为26,所述任意两个锡球球心之间的距离为160um。

36.本发明实施例中,如果发送模块或接收模块要使用mcm封装方式,则直接在原来的cowos或fop封装基础上进行修改即可,具体为在该模块上添加一定数量的锡球,图中白色大圈圈即为锡球,该锡球与信号端可以通过再布线实现连接,并且,锡球的个数加上未连接的信号端个数一共为26个,每个锡球和每个未连接的信号端单独传输一个信号,此处,未连接的信号端是指未与锡球连接的信号端。并且,图4为本发明实施例中采用mcm封装方式时bump pitch示意图,如图4所示,任意相邻的两个锡球的球心之间的距离为160um,即图中的bump pitch为160um。

37.本发明实施例中,当需要实现mcm封装时,只需要在cowos或fop封装上添加一定数量和排列符合一定要求的锡球即可,并不需要重新修改ip结构,使得通过一个ip就可以实现常见的cowos、fop和mcm封装。

38.在上述实施例的基础上,优选地,所述锡球为覆晶反扣焊法锡球。

39.具体地,该锡球为覆晶反扣焊法锡球,覆晶反扣焊法为controlled collapsed chip connection,简称c4,锡球为solderbump,覆晶反扣焊法锡球即为c4锡球。在具体实施时,采用fanout技术将裸片扩大,使用再布线连接信号端与c4锡球。

40.在上述实施例的基础上,优选地,所述任一模块中有2个差分时钟信号。

41.同样地,该封装方式中也有2个差分时钟信号,即为图中黑色圈圈。

42.在上述实施例的基础上,优选地,采用双倍数据速率的传输模式,传输速率5gbps。

43.本发明实施例中,bump pitch可以基于封装走线要求进行微调,以满足不同项目的规格要求。

44.为了提高高速速率die-die互连可靠性,ip需要支持以及设计集成如下功能:

45.ip支持io输出阻抗档位可调,可调范围20~50ohm。

46.ip支持io片上端接(on die termination,简称odt)档位可调,可调范围60~480ohm。

47.ip支持自动校准计算。

48.ip支持per-bit deskew功能,支持粗细调节以及自动调节。

49.封装走线进行等长控制,且根据尽量走短线以及走线少过孔。

50.封装走线需要进行si仿真,仿真优化迭代走线的宽度和间距,确保信号质量。

51.本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的计算机程序可存储于一非易失性计算机可读取存储介质中,该计算机程序在执行时,可包括如上述各方法的实施例的流程。其中,本技术所提供的各实施例中所使用的对存储器、存储、数据库或其它介质的任何引用,均可包括非易失性和/或易失性存储器。非易失性存储器可包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)或闪存。易失性存储器可包括随机存取存储器(ram)或者外部高速缓冲存储器。作为说明而非局限,ram以多种形式可得,诸如静态ram(sram)、动态ram(dram)、同步dram(sdram)、双数据率sdram(ddrsdram)、增强型sdram(esdram)、同步链路(synchlink)dram(sldram)、存储器总线(rambus)直接ram(rdram)、直接存储器总线动态ram(drdram)、以及存储器总线动态ram(rdram)等。

52.所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,仅以上述各功能单元、模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能单元、模块完成,即将所述装置的内部结构划分成不同的功能单元或模块,以完成以上描述的全部或者部分功能。

53.以上所述实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1