一种高可靠性高效率SSOP24L封装引线框架的制作方法

一种高可靠性高效率ssop24l封装引线框架

技术领域

1.本实用新型涉及芯片封装技术领域,尤其涉及一种高可靠性高效率ssop24l封装引线框架。

背景技术:

2.集成电路(ic)主要由芯片、引线框架和塑封体三部分组成。其中引线框架的主要功能是为芯片提供机械支撑载体,并作为导电介质连接ic外部电路,传送电信号,并与塑封体一起,在芯片工作时将产生的热量散发出去,成为ic中极为关键的零部件,随着集成电路封装行业竞争的加剧,提高生产效率成为降低成本的重要方法。

3.当前使用的ssop24l引线框架的基岛(芯片载体)尺寸为100*150mil2,适用于承载小于2.5*2.0mm2尺寸的芯片。当芯片尺寸为小于1.0*1.0mm2时,键合时的焊材消耗和效率有较大增加,导致无法进一步降低成本,有待改进。

技术实现要素:

4.本实用新型的目的在于提供一种高可靠性高效率ssop24l封装引线框架。

5.本实用新型是这样实现的:一种高可靠性高效率ssop24l封装引线框架,用于封装小于1.0*1.0mm2的芯片,由多个框架单元阵列而成,所述框架单元包括基岛和多个引脚,所述基岛用于承载芯片,所述基岛的尺寸为60

×

70mil2,所述基岛表面为裸铜面,所述引脚表面为镀银面。

6.其中,所述引线框架还包括左连筋和右连筋,所述左连筋和右连筋分别用于连接基岛的左右二边。

7.其中,所述基岛上下左右四侧的引脚数量均为6个。(此处是指引脚的内侧端与基岛的布局图,并不是指引脚的外侧端与基岛的布局图,引脚外侧端和现有技术一样,只有二个方向设有引脚)。

8.本实用新型的有益效果为:所述高可靠性高效率ssop24l封装引线框架,用于封装小于等于1.0*1.0mm2的芯片,本申请人对基岛尺寸进行了重新设计,从原来尺寸100

×

150mil2缩小至60

×

70mil2,能满足尺寸小于1.0*1.0mm2芯片的粘片及焊线的工艺要求,引脚的形状做出适应性的改变,保持引脚与基岛之间的距离基本不变,由于基岛尺寸变小,基岛中心位置与引脚的距离大幅度减少,键合线的长度随之变短,键合线用量减少,能够降低成本,还能减小键合时的线材损耗和提高键合效率,在后序的塑封工艺中,由于键合线变短,冲丝风险降低,可减少冲丝造成的产品短路问题,基岛尺寸变小还可减小金属和塑封料结合面积比例,增加集成电路抗分层能力,另外,基岛区域裸铜处理(原有设计为镀银处理),减少了引线框架镀银层的总面积,可以增加与塑封体的结合能力,进一步增加集成电路抗分层能力,提高了产品可靠性。

附图说明

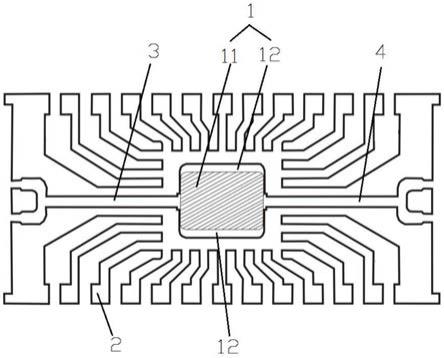

9.图1是现有技术中ssop24l封装引线框架的框架单元结构示意图;

10.图2是本实用新型所述高可靠性高效率ssop24l封装引线框架的框架单元结构示意图。

11.1、基岛;11、裸铜区域;12、镀银区域;2、引脚;3、左连筋;4、右连筋。

具体实施方式

12.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

13.作为本实用新型所述高可靠性高效率ssop24l封装引线框架的实施例,如图2所示,用于封装小于1.0*1.0mm2的芯片,由多个框架单元阵列而成,所述框架单元包括基岛1和多个引脚2,所述基岛1用于承载芯片,所述基岛1的尺寸为60

×

70mil2,所述基岛1表面为裸铜面,所述引脚2表面为镀银面。

14.在本实施例中,所述引线框架还包括左连筋3和右连筋4,所述左连筋3和右连筋4分别用于连接基岛1的左右二边,用于支撑基岛1。

15.所述高可靠性高效率ssop24l封装引线框架,用于封装小于等于1.0*1.0mm2的芯片,本申请人对基岛1尺寸进行了重新设计,从原来尺寸100

×

150mil2缩小至60

×

70mil2,能满足尺寸小于1.0*1.0mm2芯片的粘片及焊线的工艺要求,引脚2的形状做出适应性的改变,保持引脚2与基岛1之间的距离基本不变,由于基岛1尺寸变小,基岛1中心位置与引脚2的距离大幅度减少,键合线的长度随之变短,键合线用量减少,能够降低成本,还能减小键合时的线材损耗和提高键合效率,在后序的塑封工艺中,由于键合线变短,冲丝风险降低,可减少冲丝造成的产品短路问题,基岛1尺寸变小还可减小金属和塑封料结合面积比例,增加集成电路抗分层能力,另外,基岛区域裸铜处理(原有设计为镀银处理),减少了引线框架镀银层的总面积,可以增加与塑封体的结合能力(塑封料与裸铜结合的效果明显强于镀银),进一步增加集成电路抗分层能力,提高了产品可靠性。

16.由于部分产品区域地线连接,所以为了解决导电性的问题,特别在把基岛1中部大部分区域设计为裸铜区域11,即裸铜处理(原有设计为镀银处理),两边很窄的一部分区域设计为镀银区域12,以适应此类产品的特殊要求。

17.在本实施例中,所述基岛1上下左右四侧的引脚2数量均为6个。键合线分布均匀,布局合理,方便键合操作。在小尺寸的基岛上键合多根金属线,均匀布置是最优的方案。

18.本实用新型所述的引线框架结构是在原有基岛、加强筋、引脚保持原有加工工艺不变的情况下进行的处理,着重处理引线框架的基岛、引脚尺寸,以及基岛进行的裸铜处理,目的是降低成本、提高生产效率,减少产品塑封冲丝短路风险和增强产品抗分层能力。

19.与现有技术相比,本申请基岛在x方向缩短比例为32.4%,在y方向缩短比例为27.6%,在键合工序的键合效率数据如下表:

20.引线框架根线/秒每小时产出(粒)每天运行小时每天产出60*70mil1023002250600100*150mil818002239600

21.通过上表可以看出,本申请的技术方案生产效率得到有效提升,从而能进一步降低生产成本。

22.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

技术特征:

1.一种高可靠性高效率ssop24l封装引线框架,用于封装小于1.0*1.0mm2的芯片,由多个框架单元阵列而成,所述框架单元包括基岛和多个引脚,所述基岛用于承载芯片,其特征在于,所述基岛的尺寸为60

×

70mil2,所述基岛表面为裸铜面,所述引脚表面为镀银面。2.根据权利要求1所述的高可靠性高效率ssop24l封装引线框架,其特征在于,所述引线框架还包括左连筋和右连筋,所述左连筋和右连筋分别用于连接基岛的左右二边。3.根据权利要求1所述的高可靠性高效率ssop24l封装引线框架,其特征在于,所述基岛上下左右四侧的引脚数量均为6个。

技术总结

本实用新型涉及一种高可靠性高效率SSOP24L封装引线框架,用于封装小于1.0*1.0mm2的芯片,由多个框架单元阵列而成,框架单元包括基岛和多个引脚,基岛用于承载芯片,基岛尺寸为60

技术研发人员:陈侠 叱晓鹏 贾家扬 潘廷宏 袁威

受保护的技术使用者:深圳电通纬创微电子股份有限公司

技术研发日:2021.04.21

技术公布日:2021/12/3

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1