芯片高密度封装引线框架的制作方法

1.本实用新型涉及芯片封装技术的改进,具体涉及一种芯片高密度封装引线框架的改进。

背景技术:

2.引线框架作为集成电路的芯片载体,是一种借助于键合材料(金丝、铝丝、铜丝)实现芯片内部电路引出端与外引线的电气连接,形成电气回路的关键结构件,它起到了和外部导线连接的桥梁作用,绝大部分的半导体集成块中都需要使用引线框架,是电子信息产业中重要的基础材料。

3.引线框架用于芯片封装,主要的功能是为芯片提供机械支撑的载体,并作为导电介质内外连接芯片电路而形成电路信号通路。由于当前设备精度及技术能力限制,引线框架通过划分多个block的形式来弥补设备精度及技术上的不足。因此引线框架基本采用了两个block及两个以上的方式,使引线框架的利用率得不到充分发挥。特别多芯片之间的排列问题,空间利用率低,使得制造成本高、产能低下。

4.dfn1.1

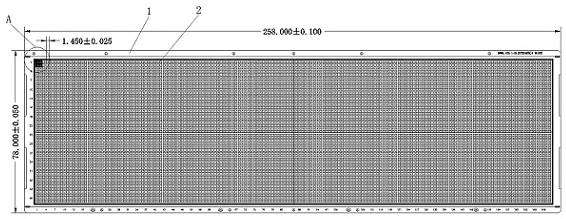

×

1.11block封装形式是一种目前市面上较为常见的封装形式,市场范围广。现有的半导体基于引线框架dfn1.1

×

1.14block框架封装产品中,框架长的长度多为250mm,宽度为70mm。单条引线框架上仅有5920个引线框单元,所有引线框单元呈40行37列4block矩阵式排列,生产效率低,成本高。

技术实现要素:

5.本实用新型的目的在于针对现有技术的缺陷和不足,提供一种新型芯片封装引线框架,它可以提高引线框架的利用率,使得引线框架得到更高的利用率,提高多芯片之间的空间利用率,可以降低制造成本、提高产能。

6.为实现上述目的,本实用新型采用以下技术方案是:它采用高密度dfn1.1

×

1.1 1block封装引线框架排布方式,采用1block的引线框架,每47个引线框单元2为一列,所述引线框单元共有171列,整齐排列在基板1上,基板1的长度为258.000

±

0.100mm,宽度为78.000

±

0.100mm,基板1上每个引线框单元2列之间的步距为1.450

±

0.025mm。

7.所述的引线框单元2与上下左右相邻的引线框单元2之间采用脚位连筋连接。

8.本实用新型采用高密度dfndfn1.1

×

1.1 1block封装引线框架,采用1block排列方式,从而提高了引线框架上引线框单元的结构密度,最终实现生产一种高密度dfn1.1

×

1.1 1block引线框架,总共能够包含8037个引线框单元,呈47行171列矩阵式排列,相较于现有的5920个引线框单元的引线框架生产效率可提升1.35倍多,相应的引线框架为1block同时降低了封装成本。

9.本实用新型采用单个block的排列形式,相比现有的分两个及两个以上block排列结构,大大提高了生产效率,最大化增加了引线框架的使用空间,从而降低生产成本、提高产能。

10.本实用新型的有益效果是:本引线框架合理地将框架分成多个相同的安装单元,尺寸分布合理,最大化增加了引线框架的使用空间,增加了框架密度,提高了设备效率,降低成本;且由于该引线框架分区合理,各个区域都留有间隔尺寸,有利于引线框单元的焊接和安装;本实用新型提高了资源利用率,框架利用率大大提高。

附图说明

11.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

12.图1是本实用新型基板1的整体结构示意图;

13.图2是图1的a部放大图。

14.附图标记说明:基板1、引线框单元2。

具体实施方式

15.参看图1-2所示,本具体实施方式采用的技术方案是:它采用高密度dfn1.1

×

1.1 1block封装引线框架排布方式,采用1block的引线框架,每47个引线框单元2为一列,所述引线框单元共有171列,整齐排列在基板1上,基板1的长度为258.000

±

0.100mm,宽度为78.000

±

0.100mm,基板1上每个引线框单元2列之间的步距为1.450

±

0.025mm。

16.所述的引线框单元2与上下左右相邻的引线框单元2之间采用脚位连筋连接。

17.本实用新型采用高密度dfndfn1.1

×

1.1 1block封装引线框架,采用1block排列方式,从而提高了引线框架上引线框单元的结构密度,最终实现生产一种高密度dfn1.1

×

1.1 1block引线框架,总共能够包含8037个引线框单元,呈47行171列矩阵式排列,相较于现有的5920个引线框单元的引线框架生产效率可提升1.35倍多,相应的引线框架为1block同时降低了封装成本。

18.本实用新型采用单个block的排列形式,相比现有的分两个及两个以上block排列结构,大大提高了生产效率,最大化增加了引线框架的使用空间,从而降低生产成本、提高产能。

19.本实用新型的有益效果是:本引线框架合理地将框架分成多个相同的安装单元,尺寸分布合理,最大化增加了引线框架的使用空间,增加了框架密度,提高了设备效率,降低成本;且由于该引线框架分区合理,各个区域都留有间隔尺寸,有利于引线框单元的焊接和安装;本实用新型提高了资源利用率,框架利用率大大提高。

20.以上所述,仅用以说明本实用新型的技术方案而非限制,本领域普通技术人员对本实用新型的技术方案所做的其它修改或者等同替换,只要不脱离本实用新型技术方案的精神和范围,均应涵盖在本实用新型的权利要求范围当中。

技术特征:

1.芯片高密度封装引线框架,其特征在于:它用高密度dfn1.1

×

1.1 1block封装引线框架排布方式,采用1block的引线框架,每47个引线框单元(2)为一列,所述引线框单元共有171列,整齐排列在基板(1)上,基板(1)的长度为258.000

±

0.100mm,宽度为78.000

±

0.100mm,基板(1)上每个引线框单元(2)列之间的步距为1.450

±

0.025mm。2.根据权利要求1所述的芯片高密度封装引线框架,其特征在于:所述的引线框单元(2)与上下左右相邻的引线框单元(2)之间采用脚位连筋连接。

技术总结

芯片高密度封装引线框架,它涉及芯片封装技术的改进,具体涉及一种芯片高密度封装引线框架的改进。它采用高密度DFN1.1

技术研发人员:刘轶亮 曾长春

受保护的技术使用者:贵州中芯微电子科技有限公司

技术研发日:2021.11.29

技术公布日:2022/6/28

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1