一种半导体封装结构及测试系统的制作方法

1.本实用新型涉及半导体封装结构及测试系统,属于封装领域。

背景技术:

2.传统凸块工艺过程泄露监控方法:根据欧姆定律i=u/r,挑选两个底部不导通的凸块,设定额定电压使用仪表测量漏电流。根据漏电流值的大小可以判断凸块与凸块之间的电性能状况,从而可以判别凸块制程中的腐蚀以及等离子刻蚀的工艺能力是否稳定,如图1所示。

3.漏电流产生的原因:采用溅镀工艺制作凸块时,金属粒子向外扩散至再钝化表面,形成金属残留,如果被测凸块之间由于金属残留而导通,则会产生漏电流。

4.此方法必须挑选两个底部不导通的凸块进行测量。但凸块端无芯片设计相关信息,需要跟客户沟通获取。部分情况下无法采取该方案:

5.1)保密产品,客户不同意提供芯片设计信息;

6.2)特殊产品,整颗芯片底部金属全部导通;

7.所以,不需要挑选底部不导通的凸块,并且能避开芯片内部线路进行测量。

技术实现要素:

8.发明目的:为了克服现有技术中存在的不足,本实用新型提供一种半导体封装结构,不需要挑选底部不导通的凸块,能避开芯片内部线路进行测量,对漏电流更敏感,测量范围更广。

9.技术方案:为解决上述技术问题,本实用新型的一种半导体封装结构,所述芯片包含芯片本体,包括芯片本体,包括晶圆衬底、金属层、与金属层相连的焊盘及钝化层;

10.至少覆盖所述钝化层和焊盘的pi层;

11.所述pi层表面设置有两组梳状不导通的导线,每组导线引出至少一个进行漏电流测试凸块。

12.作为优选,所述导线为窄铜线。

13.作为优选,所述导线的梳齿之间的间距不小于2um且不大于30um。

14.作为优选,所述凸块的直径不小于5um。

15.作为优选,所述两个凸块之间的间距不小于100um。

16.作为优选,所述两组导线的梳齿交错分布。

17.作为优选,相邻梳齿之间的间距不小于30um。

18.一种半导体封装结构测试系统,包括上述半导体封装结构以及测试设备;

19.所述测试设备包括:电流测试装置、连接线以及探针,所述探针与半导体封装结构中的凸块电性连接。

20.有益效果:本实用新型的半导体封装结构,有效避开了芯片内部线路干扰、不需要客户提供产品设计信息,并且能够在边缘无效芯片上进行测量,不需要挑选底部不导通的

凸块,能避开芯片内部线路进行测量,对漏电流更敏感,测量范围更广。

附图说明

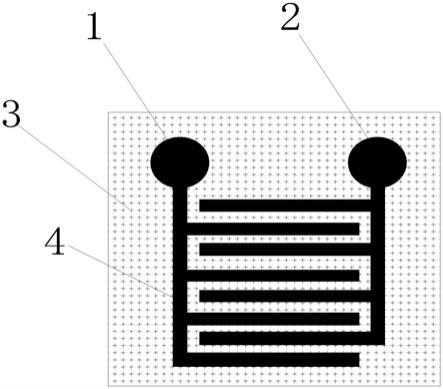

21.图1为现有的结构示意图。

22.图2为本发明的结构示意图。

23.图3为工艺异常的示意图。

24.图4为本发明的主视示意图。

具体实施方式

25.下面结合附图对本实用新型作更进一步的说明。

26.如图2至图4所示,本实用新型的一种半导体封装结构,所述芯片包含芯片本体,芯片本体硅层、金属层钝化层、pi层、焊盘,凸块连接在焊盘上,在芯片本体的表面设有至少两个凸块,分别为第一凸块1和第二凸块2,所述芯片本体表面3设有两组梳状不导通的导线4,每组导线与一个凸块连接。即第一凸块1与第一导线连通,第二凸块2与第二导线连通,第一导线和第二导线为梳状,优选梳齿为三个,第一导线和第二导线不导通。

27.在本实用新型中,所述导线为窄铜线。所述导线的梳齿之间的间距不小于2um。所述凸块的直径不小于5um。所述两组导线的梳齿交错分布。

28.本实用新型的生产工艺包含以下步骤:

29.1、在来料晶圆表面完成再钝化;

30.2、在再钝化表面完成溅射工艺;

31.3、将光刻胶均匀的旋涂在晶圆表面;

32.4、在曝光以及显影时,通过特殊设计的光刻板,将再钝化表面曝出开口;

33.5、完成电镀(去胶、腐蚀),再钝化表面将出现梳状重布线层铜线以及两个凸块,分别为第一凸块1、第二凸块2。

34.一种半导体封装结构测试系统,包括上述半导体封装结构以及测试设备;所述测试设备包括:电流测试装置、连接线以及探针,所述探针与半导体封装结构中的凸块电性连接。

35.使用测试系统测试时,正常工艺情况,两根探针分别扎在第一凸块1和第二凸块2测出的漏电流小于2na;当出现异常工艺情况a,两根探针分别扎在第一凸块1和第二凸块2测出的漏电流会远大于2na;当出现异常工艺情况b,两根探针分别扎在第一凸块1和第二凸块2测出的漏电流会大于2na,此设计对异常b的侦测更敏感。即漏电流大于2na,即为存在异常。

36.以上所述仅是本实用新型的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本实用新型原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本实用新型的保护范围。

技术特征:

1.一种半导体封装结构,其特征在于:包括晶圆衬底、金属层、与金属层相连的焊盘及钝化层,以及至少覆盖所述钝化层和焊盘的pi层;所述pi层表面设置有重布线层,所述重布线层至少包括两组梳状不导通的导线,每组导线引出至少一个进行漏电流测试的凸块。2.根据权利要求1所述的半导体封装结构,其特征在于:所述导线为窄铜线。3.根据权利要求1所述的半导体封装结构,其特征在于:所述导线的梳齿之间的间距不小于2 um且不大于30um。4.根据权利要求1所述的半导体封装结构,其特征在于:所述凸块的直径不小于5 um。5.根据权利要求1所述的半导体封装结构,其特征在于:所述两个凸块之间的间距不小于100um。6.根据权利要求1所述的半导体封装结构,其特征在于:所述两组导线的梳齿交错分布。7.根据权利要求6所述的半导体封装结构,其特征在于:相邻梳齿之间的间距不小于30um。8.一种半导体封装结构测试系统,包括:权利要求1~7中任一项所述的半导体封装结构以及测试设备;所述测试设备包括:电流测试装置、连接线以及探针,所述探针与半导体封装结构中的凸块电性连接。

技术总结

本实用新型公开了一种半导体封装结构,所述芯片包含芯片本体,在芯片本体的表面设有至少两个凸块,所述芯片本体表面设有两组梳状不导通的导线,每组导线与一个凸块连接。本实用新型的半导体封装结构,有效避开了芯片内部线路干扰、不需要客户提供产品设计信息,并且能够在边缘无效芯片上进行测量,不需要挑选底部不导通的凸块,能避开芯片内部线路进行测量,对漏电流更敏感,测量范围更广。测量范围更广。测量范围更广。

技术研发人员:龙欣江 张国栋 梅万元 张中 陈文军

受保护的技术使用者:江苏芯德半导体科技有限公司

技术研发日:2021.12.13

技术公布日:2022/4/20

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1