半导体装置的制作方法

1.本公开涉及半导体装置。

背景技术:

2.专利文献1公开了一种半导体装置,其具备:具有第一电极和第二电极的绝缘基板;在第一电极上利用烧结金属层接合的半导体元件;由在半导体元件上设置的烧结铜层和将烧结铜层的表面覆盖的含金属层构成的接合部;在第二电极上设置的金属烧结层;以及金属引线,其一端侧与接合部接合且另一端侧经由金属烧结层与第二电极接合。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2018-147967号公报

技术实现要素:

6.用于解决课题的方案

7.本公开的一实施方式的半导体装置包含:半导体芯片,其具有形成有元件结构的元件形成面;第一导电层,其形成在半导体芯片的元件形成面上;第二导电层,其形成在第一导电层上;第一引线,其与第二导电层连接,且由以铜为主成分的材料构成;以及第三导电层,其形成在第一导电层与第二导电层之间,且包含比铜硬的材料。

附图说明

8.图1是本公开第一实施方式的半导体装置的示意性俯视图。

9.图2是图1的半导体装置的局部放大图。

10.图3是图1的半导体装置的局部放大图。

11.图4是表示图2的iv-iv剖面的图。

12.图5是表示图3的v-v剖面的图。

13.图6是用于对第一引线的接合状态进行说明的图。

14.图7是用于对第二引线的接合状态进行说明的图。

15.图8a和图8b是表示所述半导体装置的制造工序的一部分的图。

16.图9a和图9b是分别表示图8a和图8b的后续工序的图。

17.图10a和图10b是分别表示图9a和图9b的后续工序的图。

18.图11a和图11b是分别表示图10a和图10b的后续工序的图。

19.图12a和图12b是分别表示图11a和图11b的后续工序的图。

20.图13a和图13b是分别表示图12a和图12b的后续工序的图。

21.图14a和图14b是分别表示图13a和图13b的后续工序的图。

22.图15a和图15b是分别表示图14a和图14b的后续工序的图。

23.图16a和图16b是分别表示图15a和图15b的后续工序的图。

24.图17a和图17b是分别表示图16a和图16b的后续工序的图。

25.图18a和图18b是分别表示图17a和图17b的后续工序的图。

26.图19是本公开第二实施方式的半导体装置的示意性剖视图。

具体实施方式

27.<本公开的实施方式>

28.首先列出本公开的实施方式进行说明。

29.本公开的一实施方式的半导体装置包含:半导体芯片,其具有形成有元件结构的元件形成面;第一导电层,其形成在所述半导体芯片的所述元件形成面上;第二导电层,其形成在所述第一导电层上;第一引线,其与所述第二导电层连接,且由以铜为主成分的材料构成;以及第三导电层,其形成在所述第一导电层与所述第二导电层之间,且包含比铜硬的材料。

30.根据该结构,可利用第三导电层来缓和在向第二导电层接合第一引线时施加的力。由此,能够缓和元件结构上的应力负荷,从而能够提供一种可靠性高的半导体装置。

31.本公开的一实施方式的半导体装置可以还包含第四导电层,该第四导电层形成在所述半导体芯片与所述第一导电层之间,且包含比铜硬的材料。

32.根据该结构,通过从半导体芯片侧起依次形成第四导电层、第一导电层、第三导电层和第二导电层,从而能够使作用于半导体芯片的应力(例如膜应力)减轻。由此,能够缓和半导体芯片的翘曲,从而能够提供一种可靠性高的半导体装置。

33.在本公开的一实施方式的半导体装置中,所述第四导电层可以包含与所述第三导电层相同的材料。

34.在本公开的一实施方式的半导体装置中,所述第三导电层的厚度可以为所述第四导电层的厚度以下。

35.根据该结构,通过使第三导电层和第四导电层中的、更接近第二导电层(第一引线的接合部)的第三导电层的厚度至少与第四导电层的厚度相同、或者相对而言较薄,从而能够使第三导电层容易因第一引线的接合时的冲击而破损。由此,能够使第一引线的接合时的应力分散,从而能够提供一种可靠性更高的半导体装置。

36.在本公开的一实施方式的半导体装置中,可以是,所述元件结构包含:凹部,其形成于所述半导体芯片;以及导电性的埋入体,其埋入于所述凹部,所述第一导电层覆盖所述凹部。

37.若在元件结构形成有凹部,则存在该凹部的形状被第一导电层和第二导电层接继的可能性。由此,与凹部未被接继的情况相比,存在第一引线的接合时的应力所引起的负荷较大的问题。本实施方式的半导体装置对于这种由应力引起的负荷容易增大的结构也具有效果,其结果,能够提供一种可靠性高的半导体装置。

38.在本公开的一实施方式的半导体装置中,可以是,所述元件结构包含分别在所述凹部露出的第一导电型的第一区域和与所述第一区域相接的第二导电型的第二区域,所述埋入体与所述第一区域及所述第二区域电连接。

39.可以是,本公开的一实施方式的半导体装置还具备:绝缘层,其形成在所述半导体芯片与所述第一导电层之间;凹部,其贯通所述绝缘层,并到达所述半导体芯片的厚度方向

中途;第四导电层,其仿照所述凹部的内表面和所述绝缘层的上表面而形成,且包含比铜硬的材料;以及导电性的埋入体,其经由所述第四导电层埋入于所述凹部。

40.若在半导体芯片形成有凹部,则存在该凹部的形状被第一导电层和第二导电层接继的可能性。由此,与凹部未被接继的情况相比,存在第一引线的接合时的应力所引起的负荷较大而导致绝缘层产生裂纹的问题。本实施方式的半导体装置对于这种由应力引起的负荷容易增大的结构也具有效果,其结果为,能够提供一种可靠性高的半导体装置。

41.另外,通过从半导体芯片侧起依次形成第四导电层、第一导电层、第三导电层和第二导电层,从而能够使作用于半导体芯片的应力(例如膜应力)减轻。由此,能够缓和半导体芯片的翘曲。

42.在本公开的一实施方式的半导体装置中,以1μm以下的间距排列有多个所述凹部。

43.在以1μm以下的间距排列有多个凹部的精密化结构中,虽然第一引线的接合时的应力所引起的负荷容易增大,但是若为本实施方式的半导体装置,则能够解决该问题。

44.本公开的一实施方式的半导体装置可以包含:第五导电层,其形成在所述半导体芯片的所述元件形成面上,且与所述第一导电层分离;第六导电层,其形成在所述第五导电层上;第二引线,其与所述第六导电层连接;以及第七导电层,其形成在所述第五导电层与所述第六导电层之间,且包含比铜硬的材料。

45.在本公开的一实施方式的半导体装置中,所述第二引线的直径可以与所述第一引线的直径相同。

46.根据该结构,能够使用相同的键合装置将第一引线和第二引线分别与第二导电层和第六导电层接合。其结果,能够提供一种可低成本且高效地制造的半导体装置。

47.在本公开的一实施方式的半导体装置中,所述第二引线可以包含由以铜为主成分的材料构成的引线。

48.在本公开的一实施方式的半导体装置中,可以是,所述元件结构包含:栅极电极;以及第一杂质区域及第二杂质区域,其形成于所述半导体芯片,且经由通过向所述栅极电极施加电压而形成的沟道导通,所述第一引线经由所述第二导电层及所述第一导电层与所述第一杂质区域电连接,所述第二引线经由所述第六导电层及所述第五导电层与所述栅极电极电连接。

49.在本公开的一实施方式的半导体装置中,所述第三导电层可以至少包含ti和w中的一方。

50.在本公开的一实施方式的半导体装置中,所述第三导电层的厚度可以为以下。

51.在本公开的一实施方式的半导体装置中,所述第一导电层和所述第二导电层可以由相同的材料形成。

52.在本公开的一实施方式的半导体装置中,所述第一导电层和所述第二导电层可以包含alcu。

53.在本公开的一实施方式的半导体装置中,所述第二导电层的厚度可以为2μm以上且4.5μm以下。

54.在本公开的一实施方式的半导体装置中,所述第二导电层可以在与所述第一引线的接合部具有第一厚度,并在所述接合部的周围具有比所述第一厚度大的第二厚度。

55.<本公开实施方式的详细说明>

56.接下来参照附图对本公开的实施方式进行详细说明。此外,在以下的详细说明中,附加序数的名称的构成要素有多个,但是该序数不一定与权利要求所述的构成要素的序数一致。

57.[第一实施方式]

[0058]

图1是本公开第一实施方式的半导体装置1的示意性俯视图。在图1中为了清楚而以虚拟线(虚线)表示封装4并以实线表示其他结构。

[0059]

半导体装置1包含导线框2、半导体元件3和封装4。

[0060]

导线框2形成为金属制的板状。导线框2由俯视呈矩形的cu等的薄金属板构成,并通过冲裁加工、切取加工、弯曲加工等而形成。因此,导线框2的原材料的主要成分为cu。此外,导线框2的原材料不限于此。

[0061]

导线框2可以包含管芯焊垫部21、第一导线部22、第二导线部23和第三导线部24。在本实施方式中,也可以将第一导线部22、第二导线部23和第三导线部24分别称为源极导线部、栅极导线部和漏极导线部。另外,第一导线部22、第二导线部23和第三导线部24从封装4露出,且具有与半导体装置1的外部电路连接的部分,因此也可以称为第一端子(源极端子)、第二端子(栅极端子)和第三端子(漏极端子)。

[0062]

俯视来看,管芯焊垫部21呈四边形状而具有:在第一方向x上延伸的一对第一边211a、211b;以及在与第一方向x交叉的方向(在本实施方式中为正交的方向)上延伸的一对第二边212a、212b。

[0063]

第一导线部22、第二导线部23和第三导线部24配置在管芯焊垫部21的周围。在本实施方式中,第一导线部22、第二导线部23和第三导线部24与管芯焊垫部21的第一边211a、211b相邻配置。更具体而言,第一导线部22和第二导线部23与管芯焊垫部21的一个第一边211a相邻配置,第三导线部24与管芯焊垫的另一个第一边211b相邻配置。即,第一导线部22和第二导线部23隔着管芯焊垫部21配置于第三导线部24的相反侧。

[0064]

第一导线部22形成为与管芯焊垫部21分离。第一导线部22可以包含第一焊垫部221和第一导线222。第一焊垫部221形成为俯视来看沿着管芯焊垫部21的第一边211a较长的大致长方形状。第一导线222与第一焊垫部221一体地形成,并从第一焊垫部221起在与第一焊垫部221的长边方向交叉的方向上延伸。第一导线222形成有多个(在本实施方式中为三个)。多个第一导线222沿着共用的第一焊垫部221的长边方向彼此空开间隔排列,并与该共用的第一焊垫部221连接。

[0065]

第二导线部23形成为与管芯焊垫部21和第一导线部22分离。第二导线部23可以包含第二焊垫部231和第二导线232。第二焊垫部231形成为沿着管芯焊垫部21的第一边211a较长的大致长方形状。第二导线232与第二焊垫部231一体地形成,并从第二焊垫部231起在与第二焊垫部231的长边方向交叉的方向上延伸。第二导线232相对于第二焊垫部231一对一地连接。在本实施方式中,第二导线部23配置在管芯焊垫部21的一个第一边211a的一端部(管芯焊垫部21的一个角部)附近,第一导线部22从该端部朝向另一端部沿着管芯焊垫部21的第一边211a延伸。

[0066]

第三导线部24与第一导线部22和第二导线部23不同,该第三导线部24与管芯焊垫部21一体地形成。第三导线部24从管芯焊垫部21的另一个第一边211b起在与该第一边211b

交叉的方向上延伸。第三导线部24形成有多个(在本实施方式中为四个)。多个第三导线部24沿着管芯焊垫部21的第一边211b彼此空开间隔排列。

[0067]

半导体元件3配置在导线框2的管芯焊垫部21上而被管芯焊垫部21支撑。俯视来看,半导体元件3呈比管芯焊垫部21小的四边形状而具有:一对第一边31a、31b和一对第二边32a、32b。在本实施方式中,半导体元件3在管芯焊垫部21上配置为:第一边31a、31b与管芯焊垫部21的第一边211a、211b平行,且第二边32a、32b与管芯焊垫部21的第二边212a、212b平行。管芯焊垫部21的第一边211a、211b与半导体元件3的第一边31a、3b之间的第一距离d1比管芯焊垫部21的第二边212a、212b与半导体元件3的第二边32a、32b之间的第二距离d2狭窄。例如,第一距离d1可以为第二距离d2的1/2以下。

[0068]

在半导体元件3的一面(在本实施方式中为上表面)形成有导电区域5和绝缘区域6。导电区域5被绝缘区域6部分地覆盖。在图1中,导电区域5中的被绝缘区域6覆盖的部分用影线区域表示,导电区域5的从绝缘区域6露出的部分用白色区域表示。导电区域5是连接后述的第一引线8和第二引线10的区域,也可以称为电极区域。

[0069]

导电区域5形成于半导体元件3上表面的大致整个区域。导电区域5可以包含第一导电区域51和第二导电区域52。第一导电区域51和第二导电区域52形成为彼此分离。

[0070]

第一导电区域51形成有多个。多个第一导电区域51形成为在沿着半导体元件3的第二边32a、32b的方向上彼此相邻,在相邻的第一导电区域51之间形成有间隙区域61。另外,第一导电区域51周围的区域可以是外周区域63。即,在将第一导电区域51的形成区域称为有源区域的情况下,外周区域63可以是将该有源区域围绕的外周区域63。在本实施方式中,各第一导电区域51形成为俯视沿着半导体元件3的第一边31a、31b较长的长方形状。第一导电区域51的一部分作为第一焊垫7而从绝缘区域6露出。

[0071]

在第一焊垫7连接有第一引线8。在本实施方式中,第一引线8由以cu为主成分的所谓cu引线构成。作为以cu为主成分的引线,例如可举出:由cu单质(例如cu的纯度为99.99%以上)构成的引线、使cu与其他合金成分合金化而成的cu合金的引线、cu单质引线或cu合金引线被导电层覆盖而成的引线等。作为cu合金引线的合金成分,例如可举出ag、au、al、ni、be、fe、ti、pd、zn、sn等。另外,作为导电层覆盖cu引线的覆盖成分,例如可举出pd等。此外,作为变形例,第一引线8也可以使用au引线、al引线。当作为键合引线而采用au引线时,au由于高价且价格波动而成本不稳定,且在高温环境下因金与铝之间的化合物生成而容易发生引线剥离。另外,当作为键合引线而采用al引线时,铝的熔点较低,在高温环境下容易发生再结晶。通过将cu引线用作第一引线8,能够提供与采用au引线或al引线时相比可靠性高的半导体装置。第一引线8例如在cu引线的情况下可以具有φ118μm以上且φ150μm以下的直径。

[0072]

第一引线8将第一焊垫7与第一导线部22的第一焊垫部221连接。第一引线8可以包含:长引线81、和比长引线81短的短引线82。长引线81可以与相邻的一对第一焊垫7中的远离第一导线部22的一侧的第一焊垫7连接。另一方面,短引线82可以与该一对第一焊垫7中的接近第一导线部22的一侧的第一焊垫7连接。

[0073]

长引线81和短引线82可以分别设置有多个,并沿着第一焊垫部221的长边方向交替地配置。另外,长引线81的第一焊垫部221侧的键合部811、和短引线82的第一焊垫部221侧的键合部821分别相对于第一焊垫部221的长边方向而言在一侧和另一侧偏置配置。由

此,长引线81的键合部811与短引线82的键合部821相互错开配置,能够防止相互接触。其结果为,能够实现第一导线部22的省空间化。

[0074]

第二导电区域52可以一体地包含焊垫区域521和指形区域522。在本实施方式中,焊垫区域521形成于外周区域63,且配置于半导体元件3的一个角部。指形区域522从焊垫区域521起沿着半导体元件3的周缘部形成于外周区域63。在本实施方式中,指形区域522以将第一导电区域51围绕的方式沿着半导体元件3的第一边31a、31b和第二边32a、32b形成。另外,指形区域522也可以形成于相邻的第一导电区域51之间的间隙区域61。由此,各第一导电区域51分别被指形区域522围绕。

[0075]

指形区域522被绝缘区域6覆盖,另一方面,焊垫区域521的一部分则作为第二焊垫9从绝缘区域6露出。

[0076]

在第二焊垫9连接有第二引线10。第二引线10可以由与第一引线8相同的材料形成。即,在本实施方式中,第二引线10也可以由以cu为主成分的所谓cu引线构成,但是作为变形例,也可以使用au引线、al引线。另外,第二引线10可以具有与第一引线8相同的直径。即,第二引线10例如在cu引线的情况下可以具有φ218μm以上且φ250μm以下的直径。

[0077]

第二引线10将第二焊垫9与第二导线部23的第二焊垫部231连接。第二引线10可以具有比第一引线8的短引线82短的长度。

[0078]

封装4将半导体元件3、第一引线8、第二引线10和导线框2的一部分覆盖,且可以称为封固树脂。封装4由具有绝缘性的原材料构成。在本实施方式中,封装4例如由黑色的环氧树脂构成。

[0079]

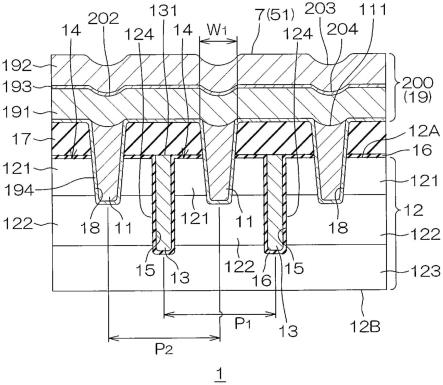

图2是表示图1的第一焊垫7下方的平面结构的局部放大图。图3是表示图1的第二焊垫9下方的平面结构的局部放大图。图4是表示图2的iv-iv剖面的图。图5是表示图3的v-v剖面的图。在图3中为了清楚而将第一导电区域51和第二导电区域52用双点划线或虚线表示。

[0080]

半导体装置1具备:半导体芯片12、第一杂质区域121(源极)、第二杂质区域122(体区)、第三杂质区域123(漏极)、栅极沟槽15(第一凹部)、栅极绝缘膜16、栅极电极13(第一埋入体)、层间绝缘膜17(绝缘层)、源极沟槽18(第二凹部)、接触销11(第二埋入体)、导电层19、以及绝缘膜62。

[0081]

半导体芯片12形成了半导体元件3的外形,例如是由单晶的半导体材料形成为芯片状(长方体形状)而成的结构体。半导体芯片12由si、sic等半导体材料形成。半导体芯片12具有:第一主面12a、和第一主面12a的相反侧的第二主面12b。第一主面12a是形成功能器件的器件面。第二主面12b是不形成功能器件的非器件面。在本实施方式中,半导体芯片12可以包含半导体基板和外延层中的至少一方。

[0082]

如图4和图5所示,第一杂质区域121是在第一导电区域51下方选择性地在半导体芯片12的第一主面12a的表层部形成的p型的杂质区域。第一杂质区域121的p型杂质浓度可以为1

×

10

18

cm

-3

以上且1

×

10

20

cm

-3

以下。另外,在本实施方式中,第一杂质区域121也可以称为p型的源极区域。

[0083]

第二杂质区域122是在半导体芯片12的第一主面12a的表层部形成的n型的杂质区域。第二杂质区域122在第二主面12b侧与第一主面12a空开间隔形成为与第一杂质区域121相接。即,第二杂质区域122隔着第一杂质区域121与第一主面12a对置。第二杂质区域122的

n型杂质浓度可以为1

×

10

15

cm

-3

以上且1

×

10

19

cm

-3

以下。另外,在本实施方式中,第二杂质区域122也可以称为n型的体区域。另外,如图5所示,第二杂质区域122在第二导电区域52下方从半导体芯片12的第一主面12a露出。

[0084]

第三杂质区域123是在半导体芯片12的第二主面12b的表层部形成的p型的杂质区域。第三杂质区域123以与第二杂质区域122相接方式形成于第二主面12b的表层部的整个区域,并从第二主面12b露出。第三杂质区域123的p型杂质浓度比第一杂质区域121的p型杂质浓度低,例如可以为1

×

10

18

cm

-3

以上且1

×

10

21

cm

-3

以下。第三杂质区域123的厚度可以为1μm以上500μm以下。另外,在本实施方式中,第三杂质区域123也可以被称为p型的漂移区域或p型的漏极区域。

[0085]

栅极沟槽15(第一凹部)是贯通第一杂质区域121和第二杂质区域122并到达第三杂质区域123的槽部。如图2和图3所示,栅极沟槽15将第一杂质区域121、第二杂质区域122和第三杂质区域123围绕,从而区划了包含这些区域121、122、123的晶体管单元14。在本实施方式中,如图2和图3所示,晶体管单元14避开了第二导电区域52的下方区域,在第一导电区域51的下方区域选择性地形成。即,晶体管单元14被第一导电区域51覆盖而没有被第二导电区域52覆盖。

[0086]

在图2和图3中,晶体管单元14的排列图案呈交错状。虽然没有图示,但是晶体管单元14的排列图案也可以为矩阵状、条带状。如图2和图3所示,俯视来看,各晶体管单元14形成为四边形状,且在本实施方式中形成为长方形状。

[0087]

栅极沟槽15在以上述方式排列的多个晶体管单元14之间形成。如图4所示,相邻的栅极沟槽15的间距p1例如为1μm以下。如图2和图3所示,在栅极沟槽15以将多个晶体管单元14分别围绕的方式相连的情况下,栅极沟槽15的间距p1例如可以是隔着一个晶体管单元14对置的栅极沟槽15之间的距离。

[0088]

如图4和图5所示,栅极绝缘膜16将栅极沟槽15的内表面覆盖。另外,栅极绝缘膜16将半导体芯片12的第一主面12a覆盖。栅极绝缘膜16例如由包括sio2、sin等在内的具有绝缘性的材料形成。

[0089]

栅极电极13收纳于栅极沟槽15。通过采用这种结构,与平面结构相比而言能够实现精细化和低导通电阻化。另外,栅极电极13利用栅极绝缘膜16而与半导体芯片12绝缘,从而防止产生漏电流。栅极电极13是包括多晶硅等在内的具有导电性的材料。由于多晶硅和单晶硅的熔点大致相等,因此通过将多晶硅用作栅极电极13,从而在栅极电极13形成后的工艺中消除了温度对工艺的限制。

[0090]

栅极电极13隔着栅极绝缘膜16与第二杂质区域122对置。在第二杂质区域122中,与栅极电极13对置的栅极沟槽15的侧面部是沟道区域124。通过向栅极电极13施加电压,能够在沟道区域124中诱发载流子(在本实施方式中为电子),使第一杂质区域121与第三杂质区域123之间导通。即,在半导体装置1中由晶体管单元14和栅极电极13形成了元件结构。

[0091]

如图4所示,栅极电极13可以在第一导电区域51下方具有与半导体芯片12的第一主面12a表面一致或者向第二主面12b侧凹陷的上表面131。另一方面,如图5所示,栅极电极13可以在第二导电区域52下方具有与半导体芯片12的第一主面12a表面一致或者向第二主面12b侧凹陷的上表面132。

[0092]

在半导体芯片12的第一主面12a上以将栅极绝缘膜16和栅极电极13覆盖的方式形

成有层间绝缘膜17。层间绝缘膜17使栅极电极13与第一导电层191绝缘。因此,栅极电极13成为被栅极绝缘膜16和层间绝缘膜17覆盖的结构。层间绝缘膜17是包括sio2、sin等在内的具有绝缘性的材料。

[0093]

参照图2和图3,在各晶体管单元14形成有源极沟槽18(第二凹部)。在本实施方式中,在各晶体管单元14逐一形成有源极沟槽18,但是也可以在各晶体管单元14形成有多个。俯视来看,源极沟槽18形成沿着俯视呈长方形状的晶体管单元14的长边方向较长的长方形状。

[0094]

参照图4和图5,源极沟槽18是贯通层间绝缘膜17、栅极绝缘膜16和第一杂质区域121并到达第二杂质区域122的槽部。源极沟槽18形成为朝向源极沟槽18的深度方向而开口宽度w1逐渐变窄的锥状。另外,如图4所示,相邻的源极沟槽18的间距p2与栅极沟槽15的间距p1相同,例如为1μm以下。

[0095]

接触销11隔着第一势垒层194埋入源极沟槽18。通过采用这种结构,能够提供缓和了栅极沟槽15底部的电场集中并提高了可靠性的半导体装置1。

[0096]

第一势垒层194抑制了形成接触销11的材料向层间绝缘膜17扩散。在本实施方式中,接触销11可以包含w(钨),第一势垒层194可以含有含ti材料(例如ti的单一层结构、或是ti和tin的层叠结构)。第一势垒层194的厚度例如为以上且以下。

[0097]

第一势垒层194的一面和另一面仿照源极沟槽18的内表面和层间绝缘膜17的上表面而形成,取得了第一杂质区域121和第二杂质区域122的直接导通。另外,第一势垒层194横切相邻的晶体管单元14的边界即栅极沟槽15的上方区域而连续。

[0098]

接触销11经由第一势垒层194取得了第一杂质区域121和第二杂质区域122的导通。接触销11具有相对于层间绝缘膜17的上表面而言向半导体芯片12的第一主面12a侧凹陷的上表面111。

[0099]

另外,在层间绝缘膜17上形成有第二势垒层198。第二势垒层198可以是含ti材料(例如ti的单一层结构、或是ti和tin的层叠结构)。第二势垒层198的厚度与第一势垒层194的厚度相同,例如为以上且以下。

[0100]

第二势垒层198的一面和另一面仿照层间绝缘膜17的上表面而形成,在未图示的位置取得了与栅极电极13的直接导通。另外,如图5所示,第二势垒层198在层间绝缘膜17上具有与第一势垒层194的端缘26空开间隔对置的端缘27。

[0101]

导电层19形成在层间绝缘膜17上。导电层19在层间绝缘膜17上具有彼此分离的多个部分。在本实施方式中,作为该多个部分而言,导电层19可以包含第一导电部200和第二导电部201。第一导电部200和第二导电部201分别具有作为前述的第一导电区域51和第二导电区域52形成的上表面。另外,第一导电部200和第二导电部201基于各自的电连接对象而也可以被称为源极电极层和栅极电极层、或者源极电极膜和栅极电极膜,也可以使用序数而被称为第一电极和第二电极。

[0102]

如图4和图5所示,第一导电部200具有从层间绝缘膜17起依次层叠的多个层。在本实施方式中,第一导电部200可以包含第一导电层191、第二导电层192和第三导电层193。第一导电层191、第二导电层192和第三导电层193在与第一导电部200的层叠方向正交的面内方向上形成于第一导电部200的整个区域,且分别在第一导电部200的端面28露出。即,在该

端面28露出了:第一导电层191、第二导电层192和第三导电层193的边界。另外,端面28可以与第一势垒层194的端缘26表面一致。

[0103]

第一导电层191以将接触销11覆盖的方式形成在层间绝缘膜17上。第一导电层191在源极沟槽18上与接触销11的上表面111相接,且在层间绝缘膜17上与第一势垒层194相接。因此,第一势垒层194的一部分被夹在层间绝缘膜17与第一导电层191之间。第一导电层191经由第一势垒层194和接触销11取得了第一杂质区域121和第二杂质区域122的导通。第一导电层191例如由含al材料构成,在本实施方式中是由alcu构成。另外,第一导电层191的厚度例如可以为2.5μm以下。

[0104]

第二导电层192隔着第三导电层193形成在第一导电层191上。第二导电层192是构成第一导电部200的最外侧表面的表面导电层,且为连接前述的第一引线8的层。因此,第二导电层192的上表面作为第一焊垫7露出。第二导电层192经由第一势垒层194、接触销11、第三导电层193和第一导电层191取得了第一杂质区域121和第二杂质区域122的导通。第二导电层192由与第一导电层191相同的材料(例如含al材料)构成,在本实施方式中是由alcu构成。另外,第二导电层192的厚度可以比第一导电层191的厚度小,例如可以为2μm以上且4.5μm以下。

[0105]

第三导电层193在第一导电层191与第二导电层192之间形成而被第一导电层191和第二导电层192夹持。第三导电层193例如由至少包含ti和w中的一方的比cu(铜)硬的材料构成,在本实施方式中,第三导电层193由从与第一导电层191的边界起依次层叠ti和tin而成的层叠结构(ti/tin)构成。第三导电层193的厚度为第一势垒层194的厚度以下,例如为以下。

[0106]

如上所述,接触销11的上表面111相对于层间绝缘膜17的上表面而言凹陷。因此,可以在第一导电层191的上表面、且在第一导电部200的层叠方向上、且在与上表面111对置的位置形成有凹部202。另外,可以在第二导电层192的上表面、且第一导电部200的层叠方向上、且在与上表面111对置的位置形成有凹部203。另外,可以在第三导电层193的上表面、且在第一导电部200的层叠方向上、且在与上表面111对置的位置形成有凹部204。

[0107]

换言之,第一导电层191和第三导电层193的边界面的一部分可以朝向源极沟槽18选择性地突出。另外,第三导电层193和第二导电层192的边界面的一部分朝向源极沟槽18选择性地突出。

[0108]

这样,第一导电部200具有在第一导电层191和第二导电层192之间夹持第三导电层193的结构。因此,在本实施方式中,可以将第三导电层193称为第一中间层,将第一导电层191称为第一下侧导电层,将第二导电层192称为第二上侧导电层。另外,第三导电层193如后述那样缓和了向第二导电层192连接cu引线时的应力而也可以被称为第一缓和层(缓冲层)或者第一应力缓和层。

[0109]

如图5所示,第二导电部201具有从层间绝缘膜17起依次层叠的多个层。在本实施方式中,第二导电部201可以包含第四导电层195、第五导电层196和第六导电层197。第四导电层195、第五导电层196和第六导电层197在与第二导电部201的层叠方向正交的面内方向上形成于第二导电部201的整个区域,且分别在第二导电部201的端面29露出。即,在该端面29露出了第四导电层195、第五导电层196和第六导电层197的边界。另外,端面29可以与第二势垒层198的端缘27表面一致。另外,第二导电部201的端面29空开空间与第一导电部200

的端面28对置。

[0110]

第四导电层195形成在层间绝缘膜17上。第四导电层195在未图示的位置与栅极电极13相接,且在层间绝缘膜17上与第二势垒层198相接。因此,第二势垒层198的一部分被夹在层间绝缘膜17和第四导电层195之间。第四导电层195经由第二势垒层198取得了与栅极电极13的导通。第四导电层195例如由含al材料构成,在本实施方式中是由alcu构成。另外,第四导电层195的厚度与第一导电层191的厚度相同,例如可以为2.5μm以下。

[0111]

第五导电层196隔着第六导电层197形成在第四导电层195上。第五导电层196是构成第二导电部201的最外侧表面的表面导电层,且为连接前述的第二引线10的层。因此,第五导电层196的上表面作为第二焊垫9露出。第五导电层196经由第二势垒层198、第四导电层195和第六导电层197取得了与栅极电极13的导通。第五导电层196由与第四导电层195相同的材料(例如含al材料)构成,在本实施方式中是由alcu构成。另外,第五导电层196的厚度比第四导电层195的厚度小,例如可以为2μm以上且4.5μm以下。另外,第五导电层196的厚度可以与第二导电层192的厚度相同。

[0112]

第六导电层197在第四导电层195与第五导电层196之间形成而被第四导电层195和第五导电层196夹持。第六导电层197例如由至少包含ti和w中的一方的比cu(铜)硬的材料构成,在本实施方式中,第六导电层197由从与第四导电层195的边界起依次层叠ti和tin而成的层叠结构(ti/tin)构成。第六导电层197的厚度为第二势垒层198的厚度以下,例如为以下。另外,第六导电层197的厚度可以与第三导电层193的厚度相同。

[0113]

这样,第二导电部201具有在第四导电层195和第五导电层196之间夹持第六导电层197的结构。因此,在本实施方式中,可以将第六导电层197称为第二中间层,将第四导电层195称为第二下侧导电层,将第五导电层196称为第二上侧导电层。另外,第六导电层197如后述那样缓和了向第五导电层196连接cu引线时的应力而也可以被称为第二缓和层(缓冲层)或者第二应力缓和层。

[0114]

另外,第四导电层195、第五导电层196和第六导电层197分别与第一导电层191、第二导电层192和第三导电层193不同,可以具有在上表面没有形成凹部202~204的平坦的上表面。

[0115]

绝缘膜62以覆盖导电层19的方式形成在层间绝缘膜17上。在第一导电部200和第二导电部201的边界部将第一导电部200的端面28、第一势垒层194的端缘26、层间绝缘膜17的上表面、第二势垒层198的端缘27和第二导电部201的端面29一体地覆盖。绝缘膜62例如由包括sin等在内的具有绝缘性的材料形成。绝缘膜62是对半导体芯片12的最外侧表面进行保护的膜,因此例如也可以被称为表面保护膜或表面绝缘膜。绝缘膜62具有作为前述的绝缘区域6形成的上表面。另外,在绝缘膜62形成有:使第一导电部200的一部分作为第一焊垫7露出的第一开口621、和使第二导电部201的一部分作为第二焊垫9露出的第二开口622。第一焊垫7可以包含第二导电层192的凹部203。

[0116]

图6是表示本公开第一实施方式的半导体装置1的第一引线8的接合状态的图。图7是表示发明第一实施方式的半导体装置1的第二引线10的接合状态的图。在图6和图7中为了清楚而仅示出了图4和图5所示结构中的对于说明第一引线8和第二引线10的接合状态而言必要的结构。

[0117]

参照图6对第一实施方式的半导体装置1的第一引线8的接合状态进行说明。

[0118]

在第二导电层192接合有第一引线8。第一引线8具有与第二导电层192相接的接合部83。接合部83通过所谓球形键合而形成。接合部83在第一导电部200的层叠方向上与第二导电层192和第三导电层193的边界85空开间隔与第二导电层192接合。因此,在接合部83的接合面84与边界85之间夹有第二导电层192的一部分,接合部83不与第三导电层193直接接触。

[0119]

另外,第一引线8的接合面84具有比第一引线8的直径φ1大的直径φ3。接合面84的直径φ3例如为150μm以上且160μm以下。由此,在第一导电部200的层叠方向上,第一引线8的接合面84可以覆盖100个以上200个以下的接触销11(源极沟槽18)。此外,在图6中为了清楚而相对于第一引线8而言以较大的比例表示源极沟槽18。

[0120]

另外,第二导电层192的与第一引线8的接合面84相接的区域选择性地凹陷且其周围选择性地隆起。在本实施方式中,第二导电层192可以包含:在第一引线8的接合面84和第三导电层193之间被夹持的接合部86、以及在接合部86的周围形成的隆起部87。接合部86的厚度t1(从边界85到接合面84的距离)比隆起部87的厚度t2(从边界85到隆起部87的顶部的距离)小。

[0121]

接下来,参照图7对第一实施方式的半导体装置1的第二引线10的接合状态进行说明。

[0122]

在第五导电层196接合有第二引线10。第二引线10具有与第五导电层196相接的接合部88。接合部88通过所谓球形键合而形成。接合部88在第二导电部201的层叠方向上与第五导电层196和第六导电层197的边界89空开间隔与第五导电层196接合。因此,在接合部88的接合面90与边界89之间夹有第五导电层196的一部分,接合部88不与第六导电层197直接接触。

[0123]

另外,第二引线10的接合面90具有比第二引线10的直径φ2大的直径φ4。接合面90的直径φ4例如为150μm以上且160μm以下。

[0124]

另外,第五导电层196的与第二引线10的接合面90相接的区域选择性地凹陷且其周围选择性地隆起。在本实施方式中,第五导电层196可以包含:在第二引线10的接合面90和第六导电层197之间被夹持的接合部91、以及在接合部91的周围形成的隆起部92。接合部91的厚度t3(从边界89到接合面90的距离)比隆起部92的厚度t4(从边界89到隆起部92的顶部的距离)小。

[0125]

以上,根据半导体装置1,作为第一引线8而使用了cu引线。例如,当作为键合引线而采用au引线时,au由于高价且价格波动而成本不稳定,且在高温环境下因金与铝之间的化合物生成而容易发生引线剥离。另外,当作为键合引线而采用al引线时,铝的熔点较低,在高温环境下容易发生再结晶。通过将cu引线用作第一引线,能够提供与采用au引线或al引线时相比可靠性高的半导体装置。

[0126]

另一方面,第一引线8相对于第二导电层192例如通过固层扩散接合、摩擦压接、超声波接合等固层接合而接合。因此,由于第一引线8(cu引线)与第二导电层192进行固层接合时的热和在导电层19的层叠方向上施加的载荷、在与导电层19的层叠方向垂直的方向上施加的振动所引起的负荷而会在包含晶体管单元14的元件结构上作用应力。

[0127]

关于这一点,在本实施方式中,在第一导电区域51的下方,在第一导电层191与第二导电层192之间形成有第三导电层193。由此,可利用第三导电层193缓和当向第二导电层

192接合第一引线8(cu引线)时作用的力。由此,能够使包含晶体管单元14的元件结构上的应力的负荷缓和,从而能够提供可靠性高的半导体装置1。

[0128]

并且,当如本实施方式这样在半导体芯片12的第一主面12a形成有源极沟槽18等凹部时,则存在该凹部的形状被第一导电层191和第二导电层192接继的可能性。例如,如图4和图5所示那样,有时在通过向源极沟槽18埋入导电材料而形成的接触销11形成凹陷的上表面111。并且,存在该上表面111的形状在第一导电层191被作为凹部202接继、以及在第二导电层192被作为凹部203接继的可能性。如果这样形成凹部202、203,则与没有形成凹部的情况相比,存在cu引线的接合时的应力所引起的负荷较大而导致在导电层19正下的层间绝缘膜17等产生裂纹的问题。本实施方式的半导体装置1对于这种由应力引起的负荷容易增大的结构也具有效果,其结果为,能够提供可靠性高的半导体装置1。

[0129]

此外,在按照1μm以下的间距p2排列有多个源极沟槽18的精密化结构中,虽然cu引线的接合时的应力所引起的负荷容易增大,但是若为本实施方式的半导体装置1,则能够解决该问题。

[0130]

另外,对于比cu(铜)硬的多个导电层即第三导电层193和第一势垒层194的厚度而言,与第一引线8的接合面84相对较近的上层的第三导电层193形成为比与第三导电层193相比而言远离接合面84的下层的第一势垒层194薄。由此,能够使第三导电层193容易因第一引线8的接合时的冲击而破损。其结果,能够使第一引线8的接合时的应力向第一导电层191的整体分散,从而能够提供一种可靠性更高的半导体装置。

[0131]

另外,在半导体装置1中,半导体芯片12上的导电层具有第一势垒层194(ti/tin)、第一导电层191(alcu)、第三导电层193(ti/tin)和第二导电层192(alcu)依次层叠而成的层叠结构。即,相对于半导体芯片12交替地层叠有由两种导电材料构成的层。由此,能够在这些导电层内使应力相互抵消,从而能够使作用于半导体芯片12的应力(例如膜应力)减轻。由此,能够缓和半导体芯片12的翘曲,从而能够提供可靠性高的半导体装置1。

[0132]

同样地,在第二导电区域52的下方也在第四导电层195与第五导电层196之间形成有第六导电层197。由此,能够利用第六导电层197缓和当向第五导电层196接合第二引线10(cu引线)时作用的力。

[0133]

接下来,参照图8a、8b~图18a、18b对半导体装置1的制造方法进行说明。图8a、8b~图18a、18b是按照工序顺序表示半导体装置1的制造工序的一部分的纵剖视图。图8a~图18a是与图2的iv-iv线对应的局部纵剖视图。图8b~图18b是与图3的v-v线对应的局部纵剖视图。

[0134]

参照图8a和图8b,在制造半导体装置1时首先准备半导体晶圆(未图示)。接下来,在该半导体晶圆形成p型的外延层60。外延层的第一主面和其相反侧的第二主面可以分别与第一主面12a和第二主面12b对应。接下来,向外延层60的第一主面12a的表层部选择性地注入p型杂质和n型杂质,形成p型的第一杂质区域121和n型的第二杂质区域122。另外,在外延层60的剩余区域形成p型的第三杂质区域123。由此,形成包含外延层60的半导体芯片12。

[0135]

接下来,参照图9a和图9b,形成栅极沟槽15。例如在半导体芯片12的第一主面12a上形成光刻胶(未图示),并通过经由该光刻胶的蚀刻而选择性地形成栅极沟槽15。

[0136]

接下来,参照图10a和图10b,例如通过热氧化法等热处理使半导体芯片12的第一主面12a和栅极沟槽15的内表面氧化。由此,在第一主面12a和栅极沟槽15的内表面形成栅

极绝缘膜16。

[0137]

接下来,参照图11a和图11b,形成栅极电极13。例如通过cvd法在栅极绝缘膜16上形成多晶硅膜。之后,通过蚀刻等将多晶硅膜的不需要的部分除去,从而形成栅极电极13。

[0138]

接下来,参照图12a和图12b,例如通过cvd法以将栅极绝缘膜16和栅极电极13覆盖的方式在第一主面12a上形成层间绝缘膜17。

[0139]

接下来,参照图13a和图13b,对层间绝缘膜17、栅极绝缘膜16、第一杂质区域121和第二杂质区域122部分地进行蚀刻,从而形成源极沟槽18。

[0140]

接下来,参照图14a和图14b,形成第一势垒材料层300。例如采用溅射法等来堆积电极材料,从而形成第一势垒材料层300。第一势垒材料层300例如含有含ti材料。作为第一势垒材料层300而言,可以首先通过溅射法形成ti膜,并在ti膜上通过溅射法形成tin膜而成为ti膜和tin膜的层叠结构。第一势垒材料层300以与源极沟槽18的内表面和层间绝缘膜17的上表面相接的方式在它们之间连续形成。

[0141]

接下来,参照图15a和图15b,在源极沟槽18内形成接触销11。例如采用cvd法等在第一势垒材料层300上堆积电极材料。之后,通过蚀刻等将该电极材料的不需要的部分除去,从而使源极沟槽18中残留的电极材料形成为接触销11。接触销11例如含有含w材料。

[0142]

接下来,参照图16a和图16b,形成第一导电材料层301。例如采用溅射法等在第一势垒材料层300和接触销11上堆积电极材料,从而形成第一导电材料层301。第一导电材料层301例如可以包含alcu。

[0143]

接下来,参照图17a和图17b,形成第二势垒材料层302。第二势垒材料层302例如含有含ti材料。作为第二势垒材料层302而言,可以首先通过溅射法形成ti膜,并在ti膜上通过溅射法形成tin膜而成为ti膜和tin膜的层叠结构。作为第二势垒材料层302而言,通过采用与第一势垒材料层300相同的材料而能够灵活运用材料,提高半导体装置1的生产率。

[0144]

接下来,参照图18a和图18b,形成第二导电材料层303。例如采用溅射法等在第二势垒材料层302上堆积电极材料,从而形成第二导电材料层303。第二导电材料层303例如可以包含alcu。作为第二导电材料层303而言,通过采用与第一导电材料层301相同的材料而能够灵活运用材料,提高半导体装置1的生产率。

[0145]

接下来,参照图18b,对第二导电材料层303、第二势垒材料层302、第一导电材料层301和第一势垒材料层300选择性地进行蚀刻,从而使这些层300~303分离为多个区域。由此,形成导电层19的第一导电部200和第二导电部201。之后,以覆盖导电层19的方式堆积绝缘材料,并对该绝缘材料选择性地进行蚀刻,从而形成具有第一开口621和第二开口622的绝缘膜62。

[0146]

接下来,通过蒸镀法、溅射法、电镀法等在半导体晶圆的背面形成漏极电极层(未图示),之后从半导体晶圆切出多个半导体装置1。经过包含以上内容的工序来制造半导体装置1。

[0147]

[第二实施方式]

[0148]

接下来,参照图19对本公开第二实施方式的半导体装置20的剖面结构进行说明。图19是本公开第二实施方式的半导体装置20的示意性剖视图。

[0149]

前述的第一实施方式的半导体装置1具有作为元件结构而具有沟槽栅极结构的misfet,但是半导体装置20具有的misfet具有平坦栅极结构。

[0150]

在半导体装置20中,第二杂质区域122在第一导电区域51下方选择性地形成于半导体芯片12的第一主面12a的表层部。多个第二杂质区域122彼此空开间隔而形成。第一杂质区域121在第二杂质区域122的内侧与第二杂质区域122的周缘空开间隔形成于第二杂质区域122的表层部。第一杂质区域121例如形成为环状。经由第一杂质区域121的中央部,第二杂质区域122的一部分作为接触部125从第一主面12a露出。另外,在第二杂质区域122中,第一杂质区域121的周缘与第二杂质区域122的周缘之间的区域是沟道区域126。

[0151]

这样,由各第二杂质区域122和该第二杂质区域122内的第一杂质区域121形成了半导体装置20的晶体管单元25。该晶体管单元25的排列图案也与第一实施方式同样地可以为交错状、矩阵状、条带状等。

[0152]

第三杂质区域123以与第二杂质区域122相接的方式形成于半导体芯片12的第二主面12b的表层部。另外,第三杂质区域123的一部分经由相邻的第二杂质区域122之间从第一主面12a露出。

[0153]

栅极绝缘膜16以覆盖沟道区域126的方式形成于半导体芯片12的第一主面12a。栅极绝缘膜16横跨相邻的第二杂质区域122。栅极电极13形成在栅极绝缘膜16上,并隔着栅极绝缘膜16与沟道区域126对置。

[0154]

层间绝缘膜17以覆盖栅极电极13的方式形成于半导体芯片12的第一主面12a。在层间绝缘膜17形成有使第一杂质区域121和第二杂质区域122(接触部125)露出的接触孔127。

[0155]

第一势垒层194的一面和另一面仿照接触孔127的内表面和层间绝缘膜17的上表面而形成,取得了第一杂质区域121和第二杂质区域122的直接导通。

[0156]

第一导电层191形成在第一势垒层194上。第一导电层191经由第一势垒层194取得了第一杂质区域121和第二杂质区域122的导通。

[0157]

第二导电层192隔着第三导电层193形成在第一导电层191上。第二导电层192是构成第一导电部200的最外侧表面的表面导电层,且为连接前述的第一引线8的层。因此,第二导电层192的上表面作为第一焊垫7露出。第二导电层192经由第一势垒层194、第三导电层193和第一导电层191取得了与第一杂质区域121和第二杂质区域122的导通。

[0158]

第三导电层193形成在第一导电层191和第二导电层192之间而被第一导电层191和第二导电层192夹持。

[0159]

如上所述,在层间绝缘膜17形成有接触孔127。因此,可以在第一导电层191的上表面、且在第一导电部200的层叠方向上、且在与接触孔127对置的位置形成凹部205。另外,可以在第二导电层192的上表面、且在第一导电部200的层叠方向上、且在与接触孔127对置的位置形成有凹部206。另外,可以在第三导电层193的上表面、且在第一导电部200的层叠方向上、且在与上表面111对置的位置形成有凹部207。

[0160]

以上在本半导体装置20中,也是在第一导电区域51下方,在第一导电层191和第二导电层192之间形成有第三导电层193。由此,可利用第三导电层193缓和当向第二导电层192接合第一引线8(cu引线)时作用的力。由此,能够使包含晶体管单元25的元件结构上的应力的负荷缓和,从而能够提供可靠性高的半导体装置20。

[0161]

另外,当在第一导电部200形成有凹部205~207时,则与没有形成凹部的情况相比,存在cu引线的接合时的应力所引起的负荷较大而导致在导电层19正下方的层间绝缘膜

17等产生裂纹的问题。本实施方式的半导体装置20对于这种由应力引起的负荷容易增大的结构也具有效果,其结果,能够提供可靠性高的半导体装置20。

[0162]

另外,在半导体装置20中,半导体芯片12上的导电层具有第一势垒层194(ti/tin)、第一导电层191(alcu)、第三导电层193(ti/tin)和第二导电层192(alcu)依次层叠而成的层叠结构。即,相对于半导体芯片12交替地层叠有由两种导电材料构成的层。由此,能够在这些导电层内使应力相互抵消,从而能够使作用于半导体芯片12的应力(例如膜应力)减轻。由此,能够缓和半导体芯片12的翘曲,从而能够提供可靠性高的半导体装置20。

[0163]

以上对本公开一实施方式进行了说明,但是本公开也可以通过其他方式实施。

[0164]

例如也可以采用使半导体装置1、20的各半导体部分的导电型翻转而成的结构。例如在半导体装置1、20中也可以是p型的部分为n型,且n型的部分为p型。

[0165]

另外,在前述的实施方式中,作为半导体装置1、20的元件结构的一例而举出misfet,但是半导体装置1、20的元件结构例如也可以是igbt(insulated gate bipolar transistor;绝缘栅双极晶体管)、pn二极管、肖特基势垒二极管等。

[0166]

此外,在权利要求书记载的事项范围内可以实施多种设计变更。

[0167]

本技术对应于2020年7月27日向日本专利局提出的专利申请特愿2020-126710号,并将该申请的全部公开内容引用于此。

[0168]

符号说明

[0169]

1—半导体装置;3—半导体元件;8—第一引线;10—第二引线;11—接触销;12—半导体芯片;12a—第一主面;12b—第二主面;13—栅极电极;14—晶体管单元;15—栅极沟槽;16—栅极绝缘膜;17—层间绝缘膜;18—源极沟槽;19—导电层;20—半导体装置;25—晶体管单元;51—第一导电区域;52—第二导电区域;83—接合部;84—接合面;85—边界;86—接合部;87—隆起部;88—接合部;89—边界;90—接合面;91—接合部;92—隆起部;111—上表面;121—第一杂质区域;122—第二杂质区域;123—第三杂质区域;124—沟道区域;126—沟道区域;191—第一导电层;192—第二导电层;193—第三导电层;194—第一势垒层;195—第四导电层;196—第五导电层;197—第六导电层;198—第二势垒层;200—第一导电部;201—第二导电部;202—凹部;203—凹部;204—凹部;205—凹部;206—凹部;207—凹部;p1—间距;p2—间距;t1—厚度;t2—厚度;t3—厚度;t4—厚度;φ1—直径;φ2—直径;φ3—直径;φ4—直径。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1