集成电路组件的制作方法

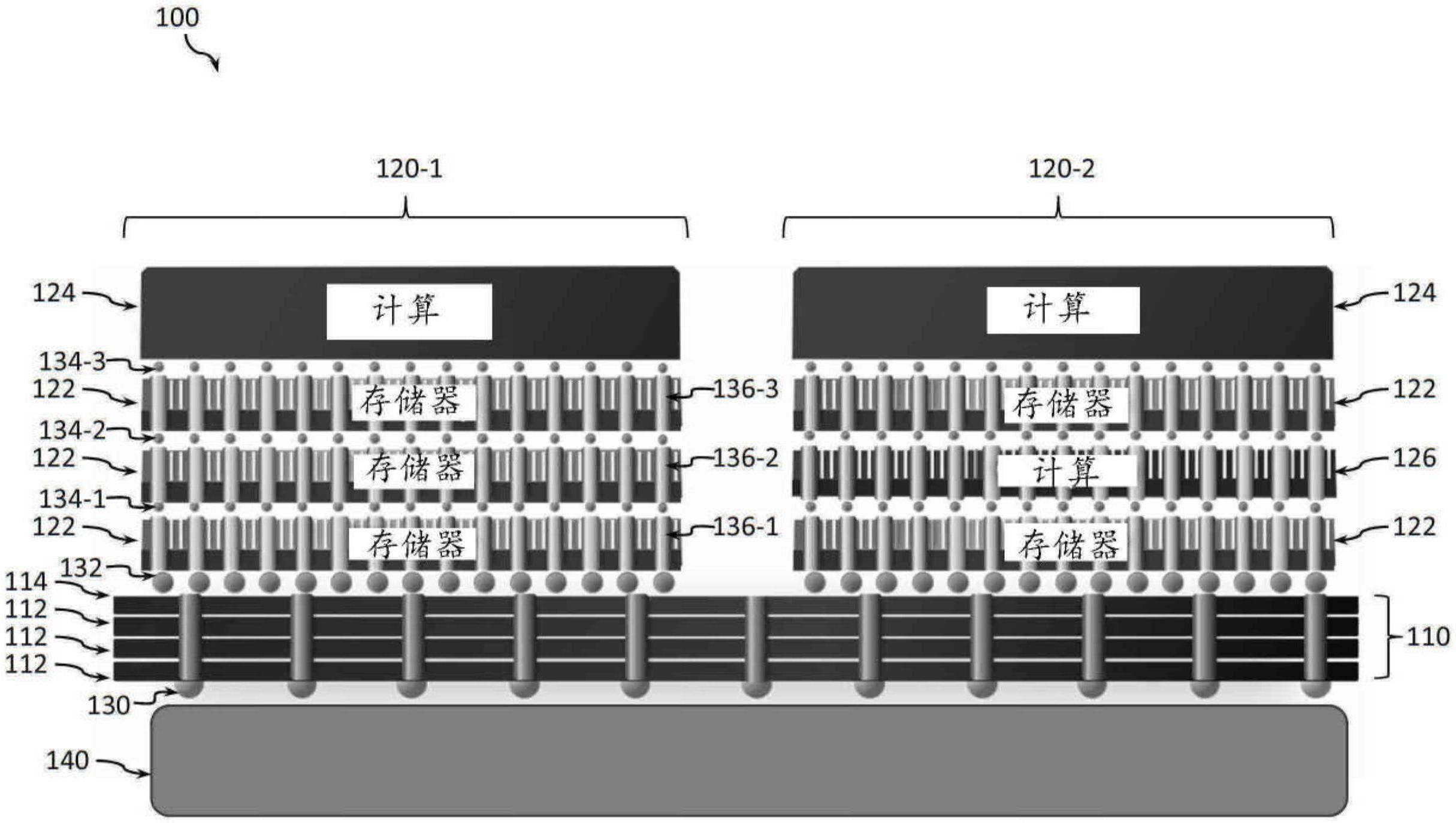

本公开一般涉及半导体器件的领域,并且更特别地,涉及包括具有存储器和计算逻辑的ic结构的微电子组件的集成电路(ic)组件,以及相关的器件、封装和方法。

背景技术:

1、在过去的几十年里,ic中的特征的缩放已经成为不断增长的半导体工业背后的驱动力。缩放到越来越小的特征使得能够在半导体芯片的有限占用面积(real estate)上增加功能单元的密度。例如,缩小晶体管尺寸允许在芯片上并入增加数量的存储器或逻辑器件,从而有助于制造具有增加容量的产品。然而,对不断增加的容量的驱动不是没有问题。优化每个ic管芯和包括一个或多个管芯的每个ic封装的性能的必要性变得越来越重要。

技术实现思路

技术特征:

1.一种微电子组件,包括:

2.根据权利要求1所述的微电子组件,其中,所述多个存储器单元包括动态随机存取存储器单元。

3.根据权利要求1所述的微电子组件,其中,所述堆叠存储器管芯包括多个静态随机存取存储器单元。

4.根据权利要求1所述的微电子组件,其中,所述基底存储器结构包括非分层存储器。

5.根据权利要求1所述的微电子组件,其中,所述堆叠存储器管芯包括分层存储器。

6.根据权利要求1所述的微电子组件,其中,所述基底存储器管芯的多个存储器单元的后端晶体管耦合成多对后端晶体管,其中,对于所述多对中的对:

7.根据权利要求6所述的微电子组件,其中,所述第一后端晶体管的所述栅极接触部和所述第二后端晶体管的所述栅极接触部在所述沟道材料的部分上方,所述沟道材料的所述部分在所述沟道材料的与所述第一后端晶体管的第一s/d接触部导电接触的部分和所述沟道材料的与所述第二后端晶体管的第一s/d接触部导电接触的部分之间。

8.根据权利要求1-7中任一项所述的微电子组件,其中,所述基底存储器管芯与所述基底计算管芯之间的所述接合界面是混合接合界面。

9.根据权利要求1-7中任一项所述的微电子组件,其中,所述电源通孔的间距在约10微米与25微米之间,并且所述信号通孔的间距在约2微米与12微米之间。

10.根据权利要求1-7中任一项所述的微电子组件,其中,所述电源通孔的横截面尺寸在约7微米与11微米之间,并且所述信号通孔的横截面尺寸在约2微米与4微米之间。

11.根据权利要求1所述的微电子组件,还包括玻璃载体结构和接合材料,其中:

12.根据权利要求11所述的微电子组件,其中,所述玻璃载体结构是石英衬底。

13.根据权利要求11或12所述的微电子组件,其中,所述基底存储器管芯的厚度小于所述玻璃载体的厚度。

14.根据权利要求11或12所述的微电子组件,其中,所述接合材料包括硅、氮和碳。

15.一种微电子组件,包括:

16.根据权利要求15所述的微电子组件,其中,所述第一线基本平行于所述存储器阵列的边缘。

17.根据权利要求15或16所述的微电子组件,其中,所述第二线基本平行于所述数据块的边缘。

18.根据权利要求15或16所述的微电子组件,其中:

19.一种微电子组件,包括:

20.根据权利要求19所述的微电子组件,其中:所述拼接导电线基本垂直于所述第一导电线的至少子集或所述第二导电线的至少子集。

技术总结

本公开的各个方面阐述IC管芯、微电子组件以及相关器件和封装。一个方面涉及分解3D单片存储器和计算功能以实现紧密耦合以用于高带宽下的快速存储器存取。另一方面涉及:微电子组件,涉及具有3D单片存储器的纳米TSV。其它方面涉及管芯拼接和在微电子组件中使用玻璃载体结构。本文中公开的各个方面有利地提供一组鲁棒的实施方式,其可以在优化个别IC管芯、包括这种管芯中的一个或多个的微电子组件以及包括这种微电子组件中的一个或多个的IC封装和器件的性能方面实现显著的改进。

技术研发人员:W·戈梅斯,A·A·夏尔马,V·H·勒,D·B·英格利

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!