半导体装置的制作方法

本发明涉及半导体装置。并且,本发明涉及具有半导体装置的系统。

背景技术:

1、以往,已知具有mos界面(金属氧化物与半导体的界面)的半导体装置。例如,在专利文献1中提出一种具有ga2o3系半导体层和以接触所述半导体层的方式配置的栅极绝缘膜的半导体装置。在这种结构的情况下,所述半导体层若为p型半导体层,则具有下述问题:电洞从所述半导体层被注入至以接触方式配置的栅极绝缘膜而导致栅极绝缘膜的膜寿命降低或特性变动。

2、另外,作为半导体,已知例如包含碳化硅(silicon carbide)、氮化镓(galliumnitride)、氮化铟(gallium indium)、氮化铝(galliumalminium)及它们的混晶的氮化镓氮化物半导体。并且,作为可实现高耐压、低损失及高耐热的下一代结晶性氧化物半导体材料,使用了能隙比上述半导体材料的能隙大的氧化镓(ga2o3)的半导体装置正受到瞩目。包含能隙大的结晶性氧化物半导体的半导体装置作为开关元件而被期待应用于反向器等电力用半导体装置。因为具有宽能隙,氧化镓也被期待应用为led或传感器等收发光装置。

3、已知氧化镓中存在α、β、γ、δ、ε这五种晶体结构。其中,具有刚玉结构的氧化镓的能隙高,作为适用于下一代的功率器件的半导体材料而受到瞩目。然而,氧化镓的最稳定相为β-gallia结构,因此也具有下述课题:对于包含具有作为准稳定相的刚玉结构的氧化镓的结晶膜而言,若不使用特殊成膜法则难以成膜这样的课题;以及其结晶膜在半导体装置中的热行为等不清楚这样的课题。相对于此,目前包含具有刚玉结构的结晶性半导体的成膜,对包含氧化镓及/或其混晶的结晶性氧化物半导体膜进行了一些研究。例如,在专利文献2中记载有可通过氧化镓与铟和铝分别或组合进行混晶来进行能隙控制,而且形成inalgao系半导体。此处inalgao系半导体表示inxalygazo3(0≤x≤2,0≤y≤2,0≤z≤2,x+y+z=1.5~2.5),可将其视为包含氧化镓在内的同一材料系统。

4、然而,例如在使用了宽能隙的氧化镓和氧化铝镓混晶等氧化物半导体的半导体装置中,具有与p型半导体层(沟道层)或n-型半导体层(漂移层)接触的栅极绝缘膜的膜寿命降低或特性变动的问题。在这种包含inalgao系半导体等氧化物半导体的半导体装置中,期待一种能够防止栅极绝缘膜的特性劣化等而可靠性优良的半导体装置。

5、专利文献1:国际公开第2013/035843号

6、专利文献2:国际公开第2014/050793号

技术实现思路

1、本发明的目的之一是提供一种防止栅极绝缘膜的特性劣化而可靠性优良的半导体装置。

2、本发明人为了达成上述目的而进行了深入研究,其结果得到如下见解:半导体装置至少包含栅极绝缘膜、以接触所述栅极绝缘膜的方式配置的电洞阻挡层(hole-blockinglayer)和以接触所述电洞阻挡层的方式配置的氧化物半导体层,通过所述电洞阻挡层配置于所述栅极绝缘膜与所述氧化物半导体层之间,由此得到能够防止栅极绝缘膜的特性劣化而可靠性优良的半导体装置,并且发现能够一举解决上述以往的问题。

3、并且,本发明人在得到上述见解后进一步反复研讨,进而完成了本发明。

4、也就是,本发明涉及以下的技术方案。

5、[1]一种半导体装置,包含栅极绝缘膜、以接触所述栅极绝缘膜的方式配置的电洞阻挡层及以接触所述电洞阻挡层的方式配置的氧化物半导体层,所述电洞阻挡层设置于所述栅极绝缘膜与所述氧化物半导体层之间。

6、[2]根据前述[1]所述的半导体装置,其中,所述电洞阻挡层具有第一导电类型,所述氧化物半导体层具有与所述第一导电类型不同的第二导电类型。

7、[3]根据前述[1]或[2]所述的半导体装置,其中,所述电洞阻挡层的能隙与所述氧化物半导体层的能隙不同。

8、[4]根据前述[1]至[3]中任一项所述的半导体装置,其中,所述电洞阻挡层为氧化物层。

9、[5]根据前述[1]至[4]中任一项所述的半导体装置,其中,所述栅极绝缘膜、所述电洞阻挡层和所述氧化物半导体层具有俯视时在水平方向上并排配置的部分。

10、[6]根据前述[1]至[5]中任一项的所述的半导体装置,其中,所述电洞阻挡层具有n型导电类型,所述氧化物半导体层具有p型导电类型。

11、[7]根据前述[5]或[6]所述的半导体装置,其中,所述氧化物半导体层3包含选自镓、铱、镍、铑及铬中的至少一种金属。

12、[8]根据前述[5]至[7]中任一项所述的半导体装置,其中,所述氧化物半导体层与所述电洞阻挡层的界面为阻挡来自所述氧化物半导体层的电洞注入的势垒。

13、[9]根据前述[5]至[8]中任一项所述的半导体装置,其中,在所述氧化物半导体层与所述电洞阻挡层的界面中对电洞的势垒高度为1.0ev以上。

14、[10]根据前述[1]至[4]中任一项所述的半导体装置,其中,所述氧化物半导体层具有n型导电类型。

15、[11]根据前述[10]所述的半导体装置,其中,所述电洞阻挡层具有p型导电类型。

16、[12]根据前述[10]或[11]所述的半导体装置,其中,所述氧化物半导体层7包含选自镓、铝及铟中的至少一种金属。

17、[13]根据前述[10]至[12]中任一项所述的半导体装置,其中,所述栅极绝缘膜与所述电洞阻挡层的界面为阻挡来自所述氧化物半导体层的电洞注入的势垒。

18、[14]根据前述[10]至[13]中任一项所述的半导体装置,其中,在所述栅极绝缘膜与所述电洞阻挡层的界面中对电洞的势垒高度为1.0ev以上。

19、[15]根据前述[5]至[14]中任一项所述的半导体装置,其中,所述半导体装置还包含以接触所述氧化物半导体层的方式配置的n型氧化物层。

20、[16]根据前述[5]至[14]中任一项所述的半导体装置,其中,所述半导体装置还包含以接触所述所述氧化物层的方式配置的p型氧化物层。

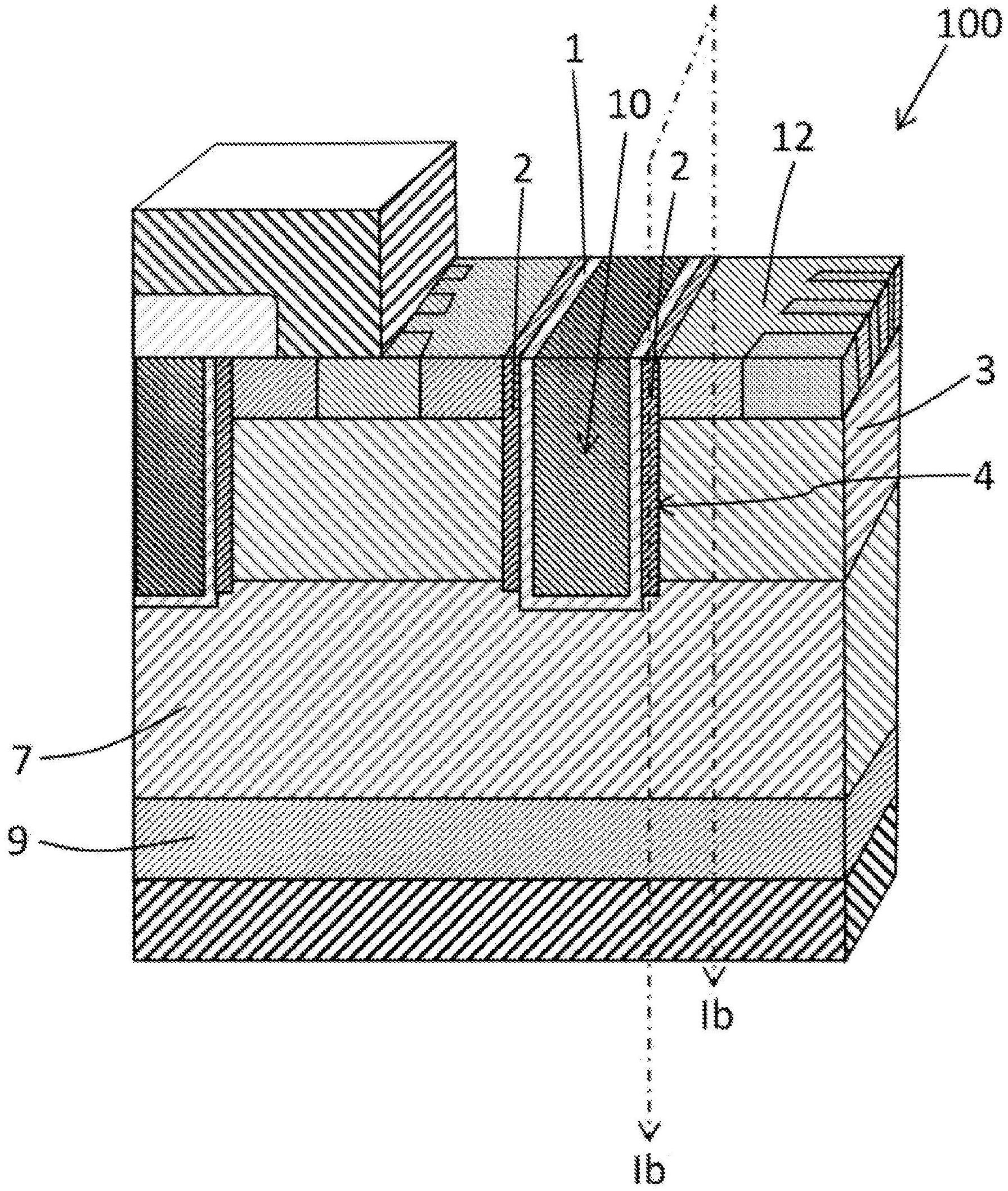

21、[17]一种半导体装置,包含:栅极绝缘膜;n型电洞阻挡层,以接触所述栅极绝缘膜1的方式配置;p型氧化物层,以接触所述n型电洞阻挡层的方式配置;p型电洞阻挡层,以接触所述栅极绝缘膜的至少一部分的方式配置;及n型氧化物层,以接触所述p型电洞阻挡层的方式配置,所述p型电洞阻挡层与所述p型氧化物层部分接触。

22、[18]一种系统,至少具有电路及与所述电路电连接的半导体装置,其中,所述半导体装置为前述[1]至[17]中任一项所述的半导体装置。

23、根据本发明的实施方式,能够提供一种可防止栅极绝缘膜的特性劣化而可靠性优良的半导体装置。

技术特征:

1.一种半导体装置,包含栅极绝缘膜、以接触所述栅极绝缘膜的方式配置的电洞阻挡层及以接触所述电洞阻挡层的方式配置的氧化物半导体层,所述电洞阻挡层设置于所述栅极绝缘膜与所述氧化物半导体层之间。

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1或2所述的半导体装置,其中,

4.根据权利要求1至3中任一项所述的半导体装置,其中,

5.根据权利要求1至4中任一项所述的半导体装置,其中,

6.根据权利要求1至5中任一项所述的半导体装置,其中,

7.根据权利要求5或6所述的半导体装置,其中,

8.根据权利要求5至7中任一项所述的半导体装置,其中,

9.根据权利要求5至8中任一项所述的半导体装置,其中,

10.根据权利要求1至4中任一项所述的半导体装置,其中,

11.根据权利要求10所述的半导体装置,其中,

12.根据权利要求10或11所述的半导体装置,其中,

13.根据权利要求10至12中任一项所述的半导体装置,其中,

14.根据权利要求10至13中任一项所述的半导体装置,其中,

15.根据权利要求5至14中任一项所述的半导体装置,其中,

16.根据权利要求5至14中任一项所述的半导体装置,其中,

17.一种半导体装置,包含:

18.一种系统,至少具有电路及与所述电路电连接的半导体装置,其中,

技术总结

本发明的目的之一是提供一种防止电洞注入栅极绝缘膜的结构。本发明的半导体装置包含栅极绝缘膜、以接触所述栅极绝缘膜的方式配置的电洞阻挡层及以接触所述电洞阻挡层的方式配置的氧化物半导体层,所述电洞阻挡层设置于所述栅极绝缘膜与所述氧化物半导体层之间。

技术研发人员:樋口安史,四户孝

受保护的技术使用者:株式会社FLOSFIA

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!