具有贯穿衬底过孔的结构及其形成方法与流程

该领域涉及具有贯穿衬底过孔的结构及其形成方法。

背景技术:

1、诸如集成器件裸片或芯片等半导体元件可以安装或堆叠在其他元件上。例如,半导体元件可以安装到载体,诸如封装衬底、中介层、重构的晶片或元件、或其他半导体元件。作为另一示例,半导体元件可以堆叠在另一半导体元件之上,例如,第一集成器件裸片可以堆叠在第二集成器件裸片上。在一些布置中,贯穿衬底过孔(tsv)可以垂直延伸穿过半导体元件的厚度,以通过半导体元件传输电信号,例如,从半导体元件的第一表面传输到半导体元件的相对的第二表面。仍然需要用于形成tsv的改进的方法。

技术实现思路

技术特征:

1.一种微电子结构,包括:

2.根据权利要求1所述的微电子器件,还包括在所述体半导体部分上的电介质层,所述第二导电过孔部分延伸穿过所述电介质层,使得所述第二导电过孔部分的端部与所述电介质层的上表面齐平或从所述电介质层的上表面凹陷。

3.根据权利要求2所述的微电子器件,其中所述电介质层包括平坦化电介质接合层,所述平坦化电介质接合层被配置用于直接接合到另一元件。

4.根据权利要求3所述的微电子器件,其中所述电介质层还包括在所述体半导体部分上的电介质阻挡层,所述平坦化电介质接合层设置在所述电介质阻挡层上。

5.根据权利要求1至4中任一项所述的微电子器件,其中所述第二阻挡层包括第二部分,所述第二部分在所述第一阻挡层与所述第二导电过孔部分之间沿着所述第一阻挡层延伸。

6.根据权利要求1至5中任一项所述的微电子器件,其中所述第一导电过孔部分的第一金属纹理不同于所述第二导电过孔部分的第二金属纹理。

7.根据权利要求6所述的微电子器件,其中所述第二金属纹理具有沿着不平行于接合界面的111晶面而取向的晶粒。

8.根据权利要求1至7中任一项所述的微电子器件,其中所述第一导电过孔部分和所述第二导电过孔部分包括铜,所述第一导电过孔部分的所述铜中具有杂质材料。

9.根据权利要求8所述的微电子器件,其中所述第一导电过孔部分具有比所述第二导电过孔部分高的杂质浓度。

10.根据权利要求8所述的微电子器件,其中所述第一导电过孔部分还包括一种或多种合金元素,所述一种或多种合金元素包括铍(be)、铟(in)、镓(ga)、锰(mn)和镍(ni)中的一种或多种。

11.根据权利要求8所述的微电子器件,其中所述杂质材料包括硫、氧、碳或氮中的一种或多种。

12.根据权利要求1至11中任一项所述的微电子器件,其中所述第一导电过孔部分和所述第二导电过孔部分包括不同金属或不同合金。

13.根据权利要求1至12中任一项所述的微电子器件,其中所述第二表面包括有源表面,所述有源表面包括形成在所述第二表面中或所述第二表面上的有源集成电路系统。

14.一种接合结构,包括根据权利要求1至13中任一项所述的微电子器件,其中所述微电子器件在没有介入粘合剂的情况下直接接合到另一元件。

15.根据权利要求14所述的接合结构,其中所述第二导电过孔部分的端表面在没有介入粘合剂的情况下直接接合到所述另一元件的接触焊盘。

16.根据权利要求14或15所述的接合结构,其中所述微电子元件和所述另一元件的非导电接合区域在没有介入粘合剂的情况下直接接合。

17.根据权利要求1至16中任一项所述的微电子器件,还包括第二过孔结构,所述第二过孔结构具有第一导电过孔部分、第二导电过孔部分、沿着所述第一导电过孔部分的侧壁延伸的第一阻挡层、和第二阻挡层,所述第二阻挡层包括第一部分,所述第一部分设置在所述第一导电过孔部分与所述第二导电过孔部分之间,其中所述过孔结构的所述第二导电过孔部分沿着与所述第二过孔结构的所述第二导电过孔部分的长度不同的长度延伸。

18.一种微电子结构,包括:

19.根据权利要求18所述的微电子器件,还包括沿着所述第一导电部分和所述第二导电部分的侧壁延伸的阻挡层。

20.根据权利要求18至19中任一项所述的微电子器件,还包括在所述体半导体部分上的电介质层,所述第二导电过孔部分延伸穿过所述电介质层,使得所述第二导电过孔部分的端部与所述电介质层的上表面齐平或凹陷到所述电介质层的上表面下方。

21.根据权利要求20所述的微电子器件,其中所述电介质层包括平坦化电介质接合层,所述平坦化电介质接合层被配置用于直接接合到另一元件。

22.根据权利要求21所述的微电子器件,其中所述电介质层还包括在所述体半导体部分上的电介质阻挡层,所述平坦化电介质接合层设置在所述电介质阻挡层上。

23.根据权利要求18至22中任一项所述的微电子器件,其中所述第一导电过孔部分的第一金属纹理不同于所述第二导电过孔部分的第二金属纹理。

24.根据权利要求23所述的微电子器件,其中所述第二金属纹理具有沿着111晶面而取向的晶粒。

25.根据权利要求18至24中任一项所述的微电子器件,其中所述第一导电过孔部分和所述第二导电过孔部分包括铜,所述第一导电过孔的所述铜中具有杂质材料。

26.根据权利要求25所述的微电子器件,其中所述第一导电过孔部分包括一种或多种合金元素,所述一种或多种合金元素包括铍(be)、铟(in)、镓(ga)、锰(mn)和镍(ni)中的一种或多种。

27.根据权利要求25所述的微电子器件,其中所述杂质材料包括硫、氧、碳或氮中的一种或多种。

28.根据权利要求18至27中任一项所述的微电子器件,其中所述第一导电过孔部分和所述第二导电过孔部分包括不同金属或不同合金。

29.一种接合结构,包括根据权利要求18至28中任一项所述的微电子器件,其中所述微电子器件在没有介入粘合剂的情况下直接接合到另一元件。

30.根据权利要求29所述的接合结构,其中所述第二导电过孔部分的端表面在没有介入粘合剂的情况下直接接合到所述另一元件的接触焊盘。

31.根据权利要求29或30所述的接合结构,其中所述微电子元件和所述另一元件的非导电接合区域在没有介入粘合剂的情况下直接接合。

32.一种微电子结构,包括:

33.根据权利要求32所述的微电子器件,还包括沿着所述第一导电部分和所述第二导电部分的侧壁延伸的阻挡层。

34.根据权利要求32或33所述的微电子器件,其中所述第一导电过孔部分的第一金属纹理不同于所述第二导电过孔部分的第二金属纹理。

35.根据权利要求34所述的微电子器件,其中所述第二金属纹理具有沿着111晶面而取向的晶粒。

36.根据权利要求35所述的微电子器件,其中所述第一金属纹理具有在垂直方向30°以内取向的第一比例的111平面,其中所述第二金属纹理具有在垂直方向30°以内取向的第二比例的111平面,所述第二比例大于所述第一部分。

37.根据权利要求32至36中任一项所述的微电子器件,其中所述第一导电过孔部分和所述第二导电过孔部分包括铜,所述第一导电过孔的所述铜中具有杂质材料。

38.根据权利要求32至37中任一项所述的微电子器件,其中与所述第二导电过孔部分相比,所述第一导电部分具有较高百分比的合金元素。

39.一种接合结构,包括根据权利要求32至38中任一项所述的微电子器件,其中所述微电子器件在没有介入粘合剂的情况下直接接合到另一元件。

40.根据权利要求39所述的接合结构,其中所述第二导电过孔部分的端表面在没有介入粘合剂的情况下直接接合到所述另一元件的接触焊盘。

41.根据权利要求39或40所述的接合结构,其中所述微电子元件和所述另一元件的非导电接合区域在没有介入粘合剂的情况下直接接合。

42.一种形成微电子结构的方法,所述方法包括:

43.根据权利要求42所述的方法,其中提供所述填充结构包括:从所述后表面在所述第一导电过孔部分之上在所述开口中提供第二导电过孔部分。

44.根据权利要求43所述的方法,还包括:在露出之后,使所述第一导电过孔部分从所述后表面凹陷。

45.根据权利要求44所述的方法,还包括:在提供所述第一导电过孔部分之后但在提供所述第二导电过孔部分之前,在所述第一导电过孔部分之上提供第二阻挡层。

46.根据权利要求45所述的方法,还包括:沿着所述第一导电过孔部分的侧壁提供第一阻挡层。

47.根据权利要求46所述的方法,还包括:在提供所述第一导电过孔部分之前提供所述第一阻挡层。

48.根据权利要求46或47所述的方法,其中提供所述第二阻挡层包括:在所述第一阻挡层与所述第二导电过孔部分之间沿着所述第一阻挡层提供所述第二阻挡层。

49.根据权利要求43至48中任一项所述的方法,还包括:在所述体半导体部分上提供电介质层,所述电介质层至少部分地限定所述衬底的所述后表面,所述第二导电过孔部分延伸穿过所述电介质层,使得所述第二导电过孔部分的端部与所述衬底的所述后表面齐平或从所述衬底的所述后表面凹陷。

50.根据权利要求49所述的方法,还包括:制备所述电介质层以用于直接接合到另一元件。

51.根据权利要求50所述的方法,还包括:在所述体半导体部分上提供电介质阻挡层,所述电介质接合层设置在所述电介质阻挡层上。

52.根据权利要求50或51所述的方法,还包括:在没有介入粘合剂的情况下将所述电介质层直接接合到另一元件。

53.根据权利要求52所述的方法,还包括:在没有介入粘合剂的情况下将所述第二导电过孔部分的端表面直接接合到所述另一元件的接触焊盘。

54.根据权利要求42所述的方法,其中提供所述填充结构包括:在所述第一导电过孔部分之上在凹部中提供电介质层。

55.根据权利要求54所述的方法,还包括:从所述后表面去除所述衬底的一部分,使得所述第一导电过孔部分从所述衬底的所述后表面突出,以及去除所述电介质层以暴露所述导电过孔。

56.根据权利要求55所述的方法,其中去除所述衬底的所述部分包括:蚀刻所述衬底的所述后表面。

57.根据权利要求56所述的方法,还包括:至少在所述衬底的所蚀刻的后表面和所述电介质层的设置在所述凹部中的一部分之上提供第二背面电介质层。

58.根据权利要求57所述的方法,还包括:去除所述第二背面电介质层的至少部分,所述至少部分覆盖设置在所述凹部中的所述电介质层的所述部分。

59.根据权利要求57或58所述的方法,还包括:平坦化所述第二背面电介质层,并且使所述第一导电过孔部分相对于所述第二背面电介质层凹陷。

60.一种形成微电子结构的方法,所述方法包括:

61.根据权利要求60所述的方法,其中用所述填充结构重新填充所述开口的所述部分包括:从所述后表面在所述第一导电过孔部分之上在所述开口中提供第二导电过孔部分。

62.根据权利要求61所述的方法,还包括:在露出之后,使所述第一导电部分凹陷,以限定所述开口的所述部分。

63.根据权利要求62所述的方法,还包括:在凹陷之后和在重新填充之前,在所述第一导电过孔部分上沉积第二阻挡层。

64.根据权利要求63所述的方法,还包括:在填充之前,沉积第一阻挡层,以对所述开口进行加衬。

65.根据权利要求64所述的方法,其中沉积所述第二阻挡层包括:在所述开口的所述部分中、在所述第一阻挡层上沉积所述第二阻挡层。

66.根据权利要求60所述的方法,其中用所述填充结构重新填充所述开口的所述部分包括:在所述第一导电过孔部分之上、在凹部中提供电介质层。

67.根据权利要求66所述的方法,还包括:从所述后表面去除所述衬底的一部分,使得所述第一导电过孔部分从所述衬底的所述后表面突出,以及去除所述电介质层以暴露所述导电过孔。

68.根据权利要求67所述的方法,其中去除所述衬底的所述部分包括:蚀刻所述衬底的所述后表面。

69.根据权利要求68所述的方法,还包括:至少在所述衬底的所蚀刻的后表面和所述电介质层的设置在所述凹部中的一部分之上提供第二背面电介质层。

70.根据权利要求69所述的方法,还包括:去除所述第二背面电介质层的至少部分,所述至少部分覆盖布置在所述凹部中的所述电介质层的所述部分。

71.根据权利要求69或70所述的方法,还包括:平坦化所述第二背面电介质层,并且使所述第一导电过孔部分相对于所述第二背面电介质层凹陷。

72.一种接合结构,包括:

73.根据权利要求72所述的接合结构,其中所述第一元件和所述第二元件的非导电接合区域在没有介入粘合剂的情况下直接接合。

74.一种形成微电子结构的方法,所述方法包括:

75.根据权利要求74所述的方法,其中去除所述衬底的所述部分包括:对所述第二进行研磨和抛光中的至少一项。

76.根据权利要求75所述的方法,其中研磨和抛光中的至少一项包括:平坦化所述衬底和所述导电过孔。

77.根据权利要求74所述的方法,其中去除所述导电过孔的所述部分包括:蚀刻所述导电过孔。

78.根据权利要求74所述的方法,其中提供所述电介质层包括:在所述衬底的所述背面之上并且在所述凹部中提供第一背面电介质层。

79.根据权利要求78所述的方法,其中提供所述第一背面电介质层包括:提供多个电介质层。

80.根据权利要求79所述的方法,其中提供所述多个电介质层包括:在所述衬底的所述背面之上和在所述导电过孔之上提供第一氮化硅层,以及在所述第一氮化硅之上提供第二氧化硅层。

81.根据权利要求78至80中任一项所述的方法,还包括:在进一步去除所述衬底的所述部分之前,去除所述第一背面电介质层的设置在所述衬底的所述背面之上的一部分。

82.根据权利要求78所述的方法,其中进一步去除所述衬底的所述部分包括:蚀刻所述衬底的所述背面。

83.根据权利要求82所述的方法,还包括:至少在所述衬底的所蚀刻的背面和所述第一背面电介质层的设置在所述凹部中的一部分之上提供第二背面电介质层。

84.根据权利要求83所述的方法,还包括:去除所述第二背面电介质层的至少部分,所述至少部分覆盖所述第一背面电介质层的设置在所述凹部中的所述部分。

85.根据权利要求83或84所述的方法,还包括:平坦化所述第二背面电介质层,并且使所述导电过孔相对于所述第二背面电介质层凹陷。

技术总结

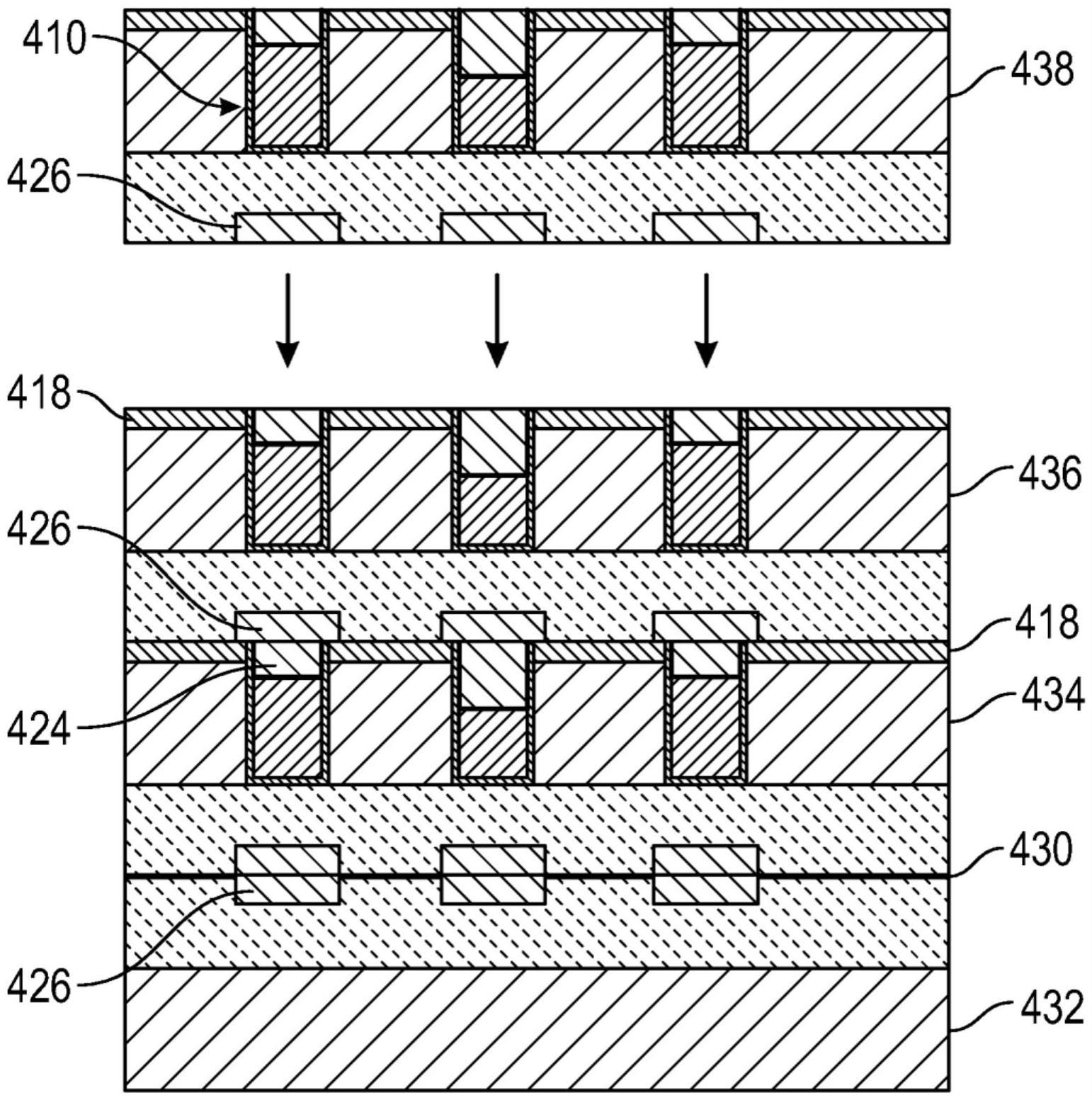

公开了一种具有贯穿衬底过孔(TSV)的微电子结构及其形成方法。微电子结构可以包括具有过孔结构的体半导体。过孔结构可以具有第一导电部分和第二导电部分。过孔结构还可以具有在第一导电部分与体半导体之间的阻挡层。该结构可以具有在第一导电部分与第二导电部分之间的第二阻挡层。第二导电部分可以从第二阻挡层延伸到体半导体的上表面。包含TSV的微电子结构被配置为使得微电子结构可以接合到第二元件或结构。

技术研发人员:G·G·小方丹,C·E·尤佐,G·C·哈德孙,J·伯斯蒂尔

受保护的技术使用者:美商艾德亚半导体接合科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!