SiC半导体装置的制作方法

本申请与2021年2月1日在日本特许厅提交的特愿2021-014602号相对应,该申请的全部公开内容通过引用并入至此。本发明涉及sic半导体装置。

背景技术:

1、专利文献1公开了包含sic基板以及形成在sic基板上的sic外延层的sic-sbd。专利文献2公开了一种半导体装置,其包含sic基板、以及在sic基板上、在与sic基板的厚度方向垂直的方向上交替形成的n型漂移区域和p型柱状区域。

2、现有技术文献

3、专利文献

4、专利文献1:美国专利申请公开第2008/0237608号说明书

5、专利文献2:美国专利申请公开第2019/0148485号说明书

技术实现思路

1、发明所要解决的课题

2、一实施方式提供能够提高电特性的sic半导体装置。

3、用于解决课题的方法

4、一实施方式提供一种sic半导体装置,其包含:具有主面的sic芯片、以及形成于上述主面的表层部且具有被至少两种5价元素调整了的杂质浓度的n型漂移区域。

5、一实施方式提供一种sic半导体装置,其包含:具有主面的sic芯片、以及形成于上述主面的表层部且具有被硼以外的3价元素调整了的杂质浓度的p型漂移区域。

6、一实施方式提供一种sic半导体装置,其包含:具有主面的sic芯片、形成于上述主面的表层部且具有被至少两种5价元素调整了的杂质浓度的n型漂移区域、以及以与上述漂移区域形成pn结部的方式形成于上述漂移区域内的p型杂质区域。

7、一实施方式提供一种sic半导体装置,其包含:具有主面的sic芯片、形成于上述主面的表层部的n型漂移区域、以及以与上述漂移区域形成pn结部的方式形成于上述漂移区域内且具有被硼以外的3价元素调整了的杂质浓度的p型杂质区域。

8、一实施方式提供一种sic半导体装置,其包含:具有主面的sic芯片、形成于上述主面的表层部且具有被硼以外的3价元素调整了的杂质浓度的p型漂移区域、以及以与上述漂移区域形成pn结部的方式形成于上述漂移区域内且具有被磷和氮以外的5价元素调整了的杂质浓度的n型杂质区域。

9、上述以外的其他目的、特征以及效果将会因通过参照附图而说明的实施方式得到明确。

技术特征:

1.一种sic半导体装置,其包含:

2.根据权利要求1所述的sic半导体装置,所述漂移区域具有以朝向所述主面上升的方式调整了的杂质浓度。

3.根据权利要求1或2所述的sic半导体装置,所述漂移区域具有被磷以外的5价元素调整了的杂质浓度。

4.根据权利要求1~3中任一项所述的sic半导体装置,所述漂移区域包含作为5价元素的氮以及氮以外的5价元素。

5.根据权利要求1~4中任一项所述的sic半导体装置,所述漂移区域具有起因于作为5价元素的第一杂质的基础浓度以及起因于作为所述第一杂质以外的5价元素的第二杂质的附加浓度。

6.根据权利要求5所述的sic半导体装置,

7.根据权利要求6所述的sic半导体装置,

8.根据权利要求5~7中任一项所述的sic半导体装置,所述附加浓度具有朝向所述主面上升的浓度分布。

9.根据权利要求5~8中任一项所述的sic半导体装置,所述基础浓度具有在厚度方向上大致恒定的浓度分布。

10.一种sic半导体装置,其包含:

11.根据权利要求10所述的sic半导体装置,所述漂移区域具有以朝向所述主面上升的方式调整了的杂质浓度。

12.根据权利要求10或11所述的sic半导体装置,所述漂移区域包含铝、镓和铟中的至少一种3价元素。

13.根据权利要求10~12中任一项所述的sic半导体装置,所述漂移区域具有起因于作为3价元素的第一杂质的基础浓度以及起因于作为与所述第一杂质相同或不同的3价元素的第二杂质的附加浓度。

14.根据权利要求13所述的sic半导体装置,

15.根据权利要求13或14所述的sic半导体装置,所述附加浓度具有朝向所述主面上升的浓度分布。

16.根据权利要求13~15中任一项所述的sic半导体装置,所述基础浓度具有在厚度方向上大致恒定的浓度分布。

17.根据权利要求1~16中任一项所述的sic半导体装置,所述漂移区域具有属于1μm以上5μm以下、5μm以上10μm以下、10μm以上15μm以下、15μm以上20μm以下以及20μm以上25μm以下的任一个范围的厚度。

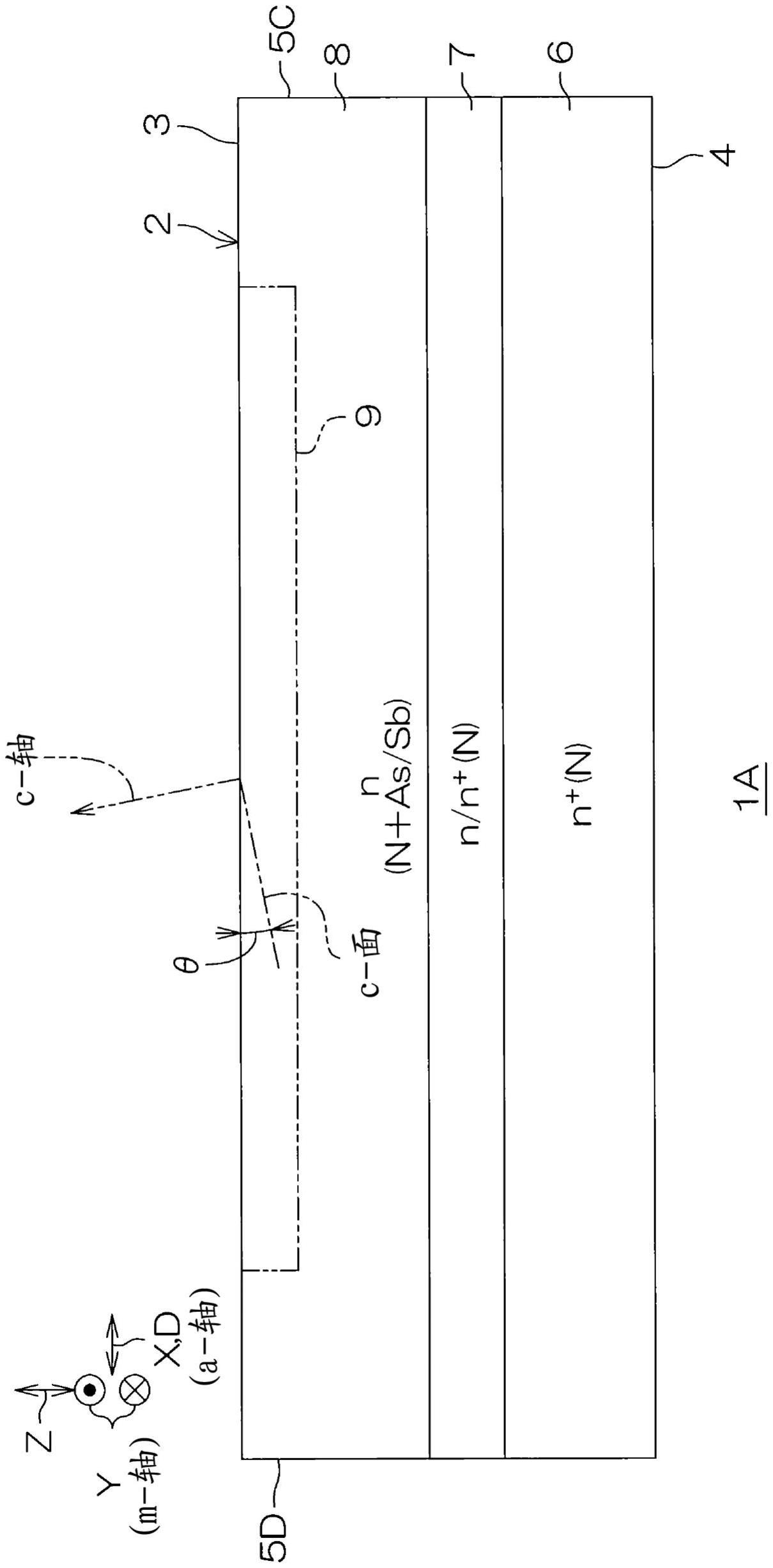

18.根据权利要求1~17中任一项所述的sic半导体装置,所述sic芯片由六方晶的sic单晶构成,

19.根据权利要求18所述的sic半导体装置,所述偏离角具有沿所述sic单晶的a轴方向的偏离方向。

20.根据权利要求1~19中任一项所述的sic半导体装置,所述漂移区域形成于sic外延层。

技术总结

一种SiC半导体装置,其包含:具有主面的SiC芯片、以及形成于上述主面的表层部且具有被至少两种5价元素调整了的杂质浓度的n型漂移区域。

技术研发人员:山本兼司,中野佑纪

受保护的技术使用者:罗姆股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!