3D半导体器件和结构的制作方法

本申请涉及集成电路(ic)器件和制造方法的一般领域,更具体地涉及多层或三维集成存储电路(3d存储)和三维集成逻辑电路(3d逻辑)器件和制造方法。

背景技术:

1、在过去的40年里,集成电路(ic)的功能和性能大幅度提高。这在很大程度上是由于“缩放”现象;即,随着每一代技术的不断发展,ic内的横向(lateral)和垂直尺寸等组件尺寸都有所减小(“缩放”)。互补金属氧化物半导体(cmos)ic中有两类主要组件,即晶体管和导线。通过“缩放”,晶体管性能和密度通常会提高,这有助于前面提到的ic性能和功能的提高。然而,将晶体管连接在一起的导线(互连件)会随着“缩放”而降低性能。目前的情况是,导线主导了ic的性能、功能和功耗。

2、半导体器件或芯片的3d堆叠是解决导线问题的一种途径。通过将晶体管排列在三维而不是二维(就像20世纪90年代的情况一样),ic中的晶体管可以放置得更靠近。这减小了导线长度,并保持低布线延迟和布线。

3、有许多构建3d堆叠集成电路或芯片的技术,包括:

4、·硅通孔(through-silicon via,tsv)技术:多层芯片分别构建。在此之后,其可以彼此接合并通过硅通孔(tsv)彼此连接。

5、·单片3d技术:通过这种方法,可以单片构建多层晶体管和导线。在以下项中描述了一些单片3d和3d ic方法:美国专利8,273,610、8,298,875、8,362,482、8,378,715、8,379,458、8,450,804、8,557,632、8,574,929、8,581,349、8,642,416、8,669,778、8,674,470、8,687,399、8,742,476、8,803,206、8,836,073、8,902,663、8,994,404、9,023,688、9,029,173、9,030,858、9,117,749、9,142,553、9,219,005、9,385,058、9,406,670、9,460,978、9,509,313、9,640,531、9,691,760、9,711,407、9,721,927、9,799,761、9,871,034、9,953,870、9,953,994、10,014,292、10,014,318、10,515,981、10,892,016;未决的美国专利申请公开案和申请14/642,724、15/150,395、15/173,686、16/337,665、16/558,304、16/649,660、16/836,659、17/151,867、62/651,722、62/681,249、62/713,345、62/770,751、62/952,222、62/824,288、63/075,067、63/091,307、63/115,000、2020/0013791、16/558,304;以及pct申请(和公开案)pct/us2010/052093、pct/us2011/042071(w02012/015550)、pct/us2016/52726(wo2017053329)、pct/us2017/052359(w02018/071143)、pct/us2018/016759(wo2018144957);以及pct/us2018/52332(wo 2019/060798)。上述专利、公开案和申请的内容以全文引用的方式并入本文中。

6、·电光:也有针对包括不同晶体层的集成单片3d的工作,如美国专利8,283,215、8,163,581、8,753,913、8,823,122、9,197,804、9,419,031、9,941,319、10,679,977和10,943,934。上述专利、公开案和申请的内容以全文引用的方式并入本文中。

7、此外,美国专利申请公开2018/0350823和美国专利申请62/963166、62/963270、62/983559、62/986772、63108433、63/118908、63/123464、63/144970、63/151664和17/151867以全文引用的方式并入本文中。

8、此外,根据本发明的一些实施例的3d技术可以实现一些非常创新的ic器件替代品,具有开发成本降低、工艺流程新颖且更简单、产量增加优点以及其它说明性优点。

技术实现思路

1、本发明涉及多层或三维集成电路(3d ic)器件和制造方法。3d ic的重要方面是允许层转移的技术。这些技术包括支持供体晶片再利用的技术,和支持在待与其一起转移的转移层上制造有源器件的技术。

技术特征:

1.一种3d器件,所述器件包括:

2.根据权利要求1所述的器件,

3.一种3d器件,所述器件包括:

4.根据权利要求2所述的器件,

5.根据权利要求2所述的器件,

6.一种3d器件,所述器件包括:

7.根据权利要求6所述的器件,

8.一种3d器件,所述器件包括:

9.一种3d器件,所述器件包括:

10.一种3d器件,所述器件包括:

11.一种3d器件,所述器件包括:

12.一种3d器件,所述器件包括:

13.根据权利要求12所述的器件,

14.根据权利要求12所述的器件,

15.一种3d器件,所述器件包括:

16.一种3d器件,所述器件包括:

17.一种3d器件,所述器件包括:

18.一种3d器件,所述器件包括:

19.一种3d器件,所述器件包括:

20.一种3d器件,所述器件包括:

21.一种3d器件,所述器件包括:

22.一种3d器件,所述器件包括:

23.一种3d器件,所述器件包括:

技术总结

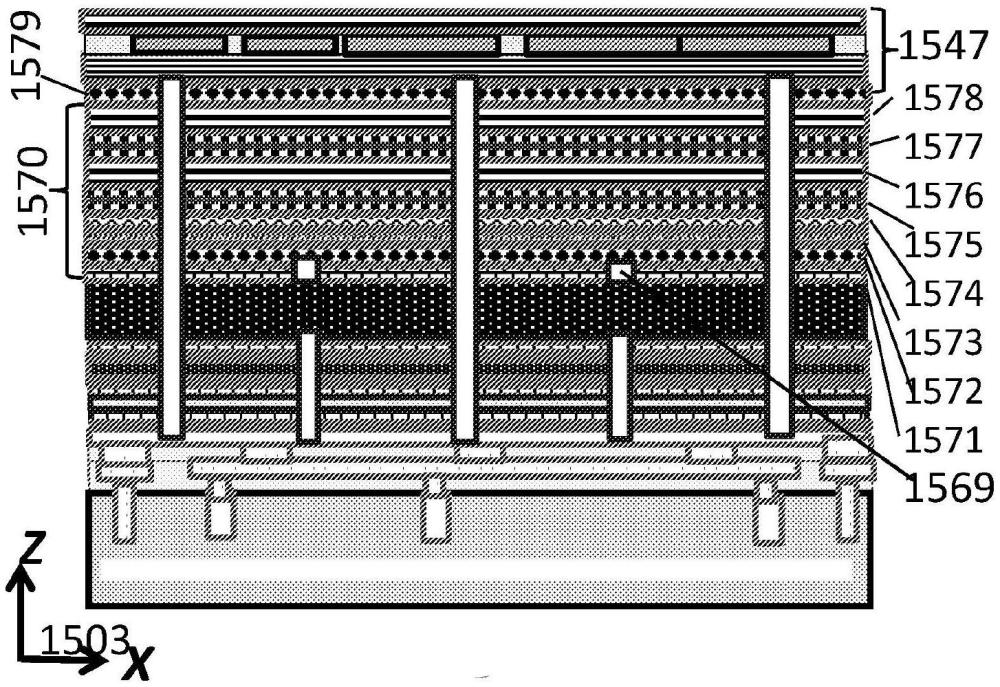

本发明涉及一种3D器件,所述器件包括:包括第一晶体管的第一层级,所述第一层级包括第一互联件;包括第二晶体管的第二层级,所述第二层级覆盖所述第一层级;包括第三晶体管的第三层级,所述第三层级覆盖所述第二层级;以及多个电子电路单元(ECU),其中所述多个ECU中的每一个包括第一电路,所述第一电路包括所述第一晶体管的一部分,其中所述多个ECU的每一个包括第二电路,所述第二电路包括所述第二晶体管的一部分,其中所述多个ECU的每一个包括第三电路,所述第三电路包括所述第三晶体管的一部分,其中所述ECU的每一个包括垂直母线,且其中所述ECU的每一个包括至少一个高电阻率富陷阱层。

技术研发人员:兹维·奥尔巴赫,韩金宇,布莱恩·克洛奎斯特,亚伦·卡彭特

受保护的技术使用者:三维单晶公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!