半导体结构及其制备方法与流程

本发明涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、重布线技术(redistribution layer,rdl)是在晶圆表面沉积金属层和电介质层,并形成相应金属布线图形,以将原来设计的集成电路(integrated circuit,ic)线路接点位置(i/o pad)进行重新布线,使ic能适用于不同的封装形式。

2、然而,传统的重布线技术形成的重布线层在填充电介质层内的孔洞时,会形成凹陷及侧壁,不利于晶片允收测试(wafer acceptance test,wat)扎针;另外,晶片允收测试探针卡(wat probe card)会扎在重布线层的侧壁上,带出大量重布线层残屑,造成探针卡和晶圆污染,甚至造成探针卡损坏。

技术实现思路

1、基于此,有必要针对现有技术中rdl填充电介质层内空洞形成具有凹陷及侧壁的重布线层,不利于wat扎针,探针卡扎在侧壁上,带出大量重布线层残屑,造成探针卡和晶圆污染的问题,提供一种半导体结构及其制备方法。

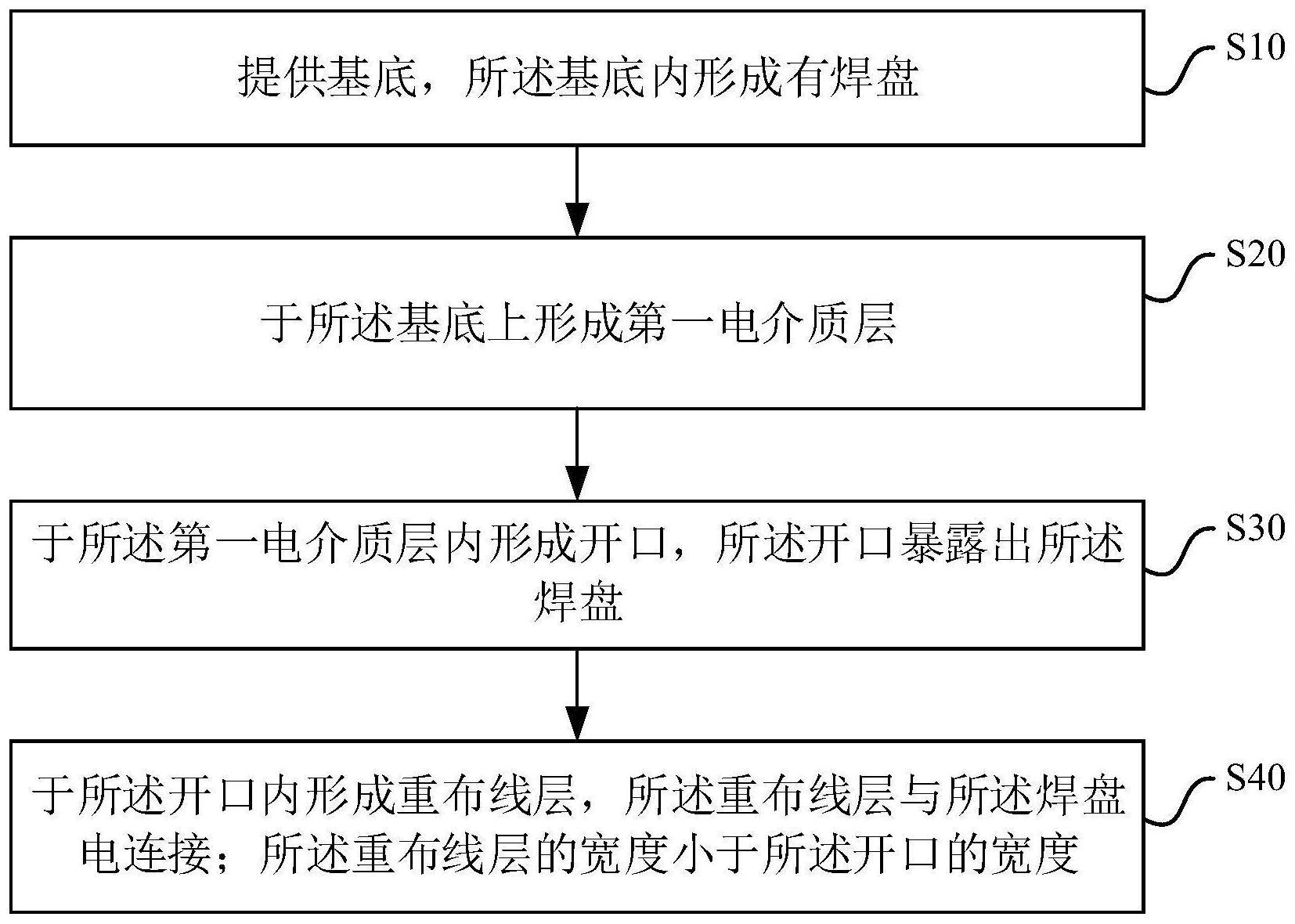

2、为解决上述技术问题,本申请的第一方面提出一种半导体结构的制备方法,包括:

3、提供基底,所述基底内形成有焊盘;

4、于所述基底上形成第一电介质层;

5、于所述第一电介质层内形成开口,所述开口暴露出所述焊盘;

6、于所述开口内形成重布线层,所述重布线层与所述焊盘电连接;所述重布线层的宽度小于所述开口的宽度。

7、于上述实施例中提供的半导体结构的制备方法中,在具有焊盘的基底上形成第一电介质层,第一电介质层内形成开口,开口暴露出基底内焊盘;并于开口内形成重布线层,重布线层与焊盘电连接;位于开口内的重现布线层的宽度小于开口的宽度。焊盘及第一电介质层相较于传统rdl技术保持不变,于开口内形成的重布线层的宽度小于开口的宽度,本申请重布线层不具有传统rdl技术形成的凹陷及侧壁,有利于wat探针扎针,不会造成重布线层大量残屑污染,能够很好的保护探针卡,保证探针卡和晶圆的洁净度。

8、在其中一个实施例中,所述开口的宽度大于所述焊盘的宽度。

9、在其中一个实施例中,所述开口的纵截面形状为倒梯形;所述重布线层与所述开口的侧壁之间具有间隙,重布线层不具有凹陷及侧壁,使得探针卡在进行wat测试时,有多余的空间与重布线层相接触,利于wat测试扎针。

10、在其中一个实施例中,所述第一电介质层包括氧化硅层。

11、在其中一个实施例中,所述于所述基底上形成第一电介质层之前,还包括于所述基底的上表面形成钝化层的步骤;所述第一电介质层形成于所述钝化层的上表面;所述开口沿厚度方向贯穿所述钝化层,以暴露出所述焊盘。

12、在其中一个实施例中,所述于所述基底上形成第一电介质层包括:

13、于所述钝化层的上表面形成第一电介质材料层;

14、对所述第一电介质材料层进行刻蚀处理,以得到所述第一电介质层。

15、在其中一个实施例中,所述于所述钝化层的上表面形成第一电介质材料层之后,且对所述第一电介质材料层进行刻蚀处理之前,还包括采用干法刻蚀工艺或化学机械研磨工艺对所述第一电介质材料层进行减薄处理。

16、在其中一个实施例中,所述于所述第一电介质层内形成开口之后,且于所述开口内形成重布线层之前,还包括:

17、于所述第一电介质层的上表面形成第二电介质层;

18、于所述第二电介质层的上表面及所述开口内形成过渡层,所述过渡层与所述焊盘相接触。

19、在其中一个实施例中,所述于所述第一电介质层的上表面形成第二电介质层包括:

20、于所述第一电介质层的上表面及所述开口内形成第二电介质材料层;

21、去除位于所述开口内的所述第二电介质材料层,以得到所述第二电介质层。

22、在其中一个实施例中,所述于所述开口内形成重布线层,包括:

23、于所述过渡层的上表面形成重布线材料层;

24、刻蚀所述重布线材料层,以得到所述重布线层;所述重布线层经由所述过渡层与所述焊盘电连接。

25、在其中一个实施例中,所述于所述开口内形成重布线层之后,还包括:

26、于所述重布线层的表面形成阻挡层,所述阻挡层包覆所述重布线层的上表面及侧壁。

27、本申请的第二方面提出一种半导体结构,包括:

28、基底,所述基底内具有焊盘;

29、第一电介质层,位于所述基底上;所述第一电介质层内具有开口,所述开口暴露出所述焊盘;

30、重布线层,位于所述开口内;所述重布线层与所述焊盘电连接;所述重布线层的宽度小于所述开口的宽度。

31、于上述实施例中提供的半导体结构,基底内具有焊盘;第一电介质层位于基底上;第一电介质层内具有开口,开口暴露出焊盘;重布线层,位于开口内的重布线层与焊盘电连接;重布线层的宽度小于开口的宽度。焊盘及第一电介质层相较于传统rdl技术保持不变,重布线层的宽度小于开口的宽度,本申请重布线层不具有传统rdl技术形成的凹陷及侧壁,有利于wat探针扎针,不会造成重布线层大量残屑污染,能够很好的保护探针卡,保证探针卡和晶圆的洁净度。

32、在其中一个实施例中,所述开口的宽度大于所述焊盘的宽度。

33、在其中一个实施例中,所述开口的纵截面形状为倒梯形;所述重布线层与所述开口的侧壁之间具有间隙,重布线层不具有凹陷及侧壁,使得探针卡在进行wat测试时,有多余的空间与重布线层相接触,利于wat测试扎针。

34、在其中一个实施例中,所述半导体结构还包括:

35、钝化层,位于所述基底的上表面;所述第一电介质层位于所述钝化层的上表面;所述开口沿厚度方向贯穿所述钝化层,以暴露出所述焊盘。

36、在其中一个实施例中,所述半导体结构还包括:

37、第二电介质层,位于所述第一电介质层的上表面;

38、过渡层,位于所述第二电介质层的上表面,且位于所述开口内;所述过渡层与所述焊盘相接触;

39、阻挡层,包覆所述重布线层的上表面及侧壁。

40、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,并可依照说明书的内容予以实施,以下以本发明的较佳实施例并配合附图详细说明如后。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述开口的宽度大于所述焊盘的宽度。

3.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述开口的纵截面形状为倒梯形;所述重布线层与所述开口的侧壁之间具有间隙。

4.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述第一电介质层包括氧化硅层。

5.根据权利要求1-4任一项所述的半导体结构的制备方法,其特征在于,所述于所述基底上形成第一电介质层之前,还包括于所述基底的上表面形成钝化层的步骤;所述第一电介质层形成于所述钝化层的上表面;所述开口沿厚度方向贯穿所述钝化层,以暴露出所述焊盘。

6.根据权利要求5所述的半导体结构的制备方法,其特征在于,所述于所述基底上形成第一电介质层包括:

7.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述于所述钝化层的上表面形成第一电介质材料层之后,且对所述第一电介质材料层进行刻蚀处理之前,还包括采用干法刻蚀工艺或化学机械研磨工艺对所述第一电介质材料层进行减薄处理。

8.根据权利要求1-4任一项所述的半导体结构的制备方法,其特征在于,所述于所述第一电介质层内形成开口之后,且于所述开口内形成重布线层之前,还包括:

9.根据权利要求8所述的半导体结构的制备方法,其特征在于,所述于所述第一电介质层的上表面形成第二电介质层包括:

10.根据权利要求8所述的半导体结构的制备方法,其特征在于,所述于所述开口内形成重布线层,包括:

11.根据权利要求8所述的半导体结构的制备方法,其特征在于,所述于所述开口内形成重布线层之后,还包括:

12.一种半导体结构,其特征在于,包括:

13.根据权利要求12所述的半导体结构,其特征在于,所述开口的宽度大于所述焊盘的宽度。

14.根据权利要求12所述的半导体结构,其特征在于,所述开口的纵截面形状为倒梯形;所述重布线层与所述开口的侧壁之间具有间隙。

15.根据权利要求12所述的半导体结构,其特征在于,所述半导体结构还包括:

16.根据权利要求12所述的半导体结构,其特征在于,所述半导体结构还包括:

技术总结

本发明公开了一种半导体结构及其制备方法,半导体结构的制备方法包括:提供基底,基底内形成有焊盘;于基底上形成第一电介质层;于第一电介质层内形成开口,开口暴露出焊盘;于开口内形成重布线层,重布线层与焊盘电连接;重布线层的宽度小于开口的宽度。焊盘及第一电介质层相较于传统RDL技术保持不变,于开口内形成的重布线层的宽度小于开口的宽度,本申请重布线层不具有传统RDL技术形成的凹陷及侧壁,有利于WAT探针扎针,不会造成重布线层大量残屑污染,能够很好的保护探针卡,保证探针卡和晶圆的洁净度。

技术研发人员:吴小飞,吴公一,徐亚超

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!