隔离改进的2D1R工艺方法及2D1R阵列与流程

本发明涉及存储器,更为具体地,涉及一种隔离改进的2d1r工艺方法及2d1r阵列。

背景技术:

1、对于2d1r的阵列结构,往往通过在硅衬底上采用深隔离槽实现阱与阱之间的隔离,从而实现不同二极管之间的隔离。该种方式主要存在的问题是由于无法对在p-sub中的p阱进行正向电压偏置,使得形成n阱与p阱交替存在的二极管阵列存在较大的漏电通路,同时需要非常深的深隔离槽方能实现阱与阱之前的隔离,对生产工艺带来相当大的困难度。

2、因此,亟需一种可以形成n阱与p阱交替存在的二极管阵列,同时又能够降低对深隔离槽的深度要求,增加工艺窗口的隔离改进的2d1r工艺方法及2d1r阵列。

技术实现思路

1、鉴于上述问题,本发明的目的是提供一种隔离改进的2d1r工艺方法及2d1r阵列,以解决由于无法对在p-sub中的p阱进行正向电压偏置,使得形成n阱与p阱交替存在的二极管阵列存在较大的漏电通路,同时需要非常深的深隔离槽方能实现阱与阱之前的隔离,对生产工艺带来相当大的困难度的问题。

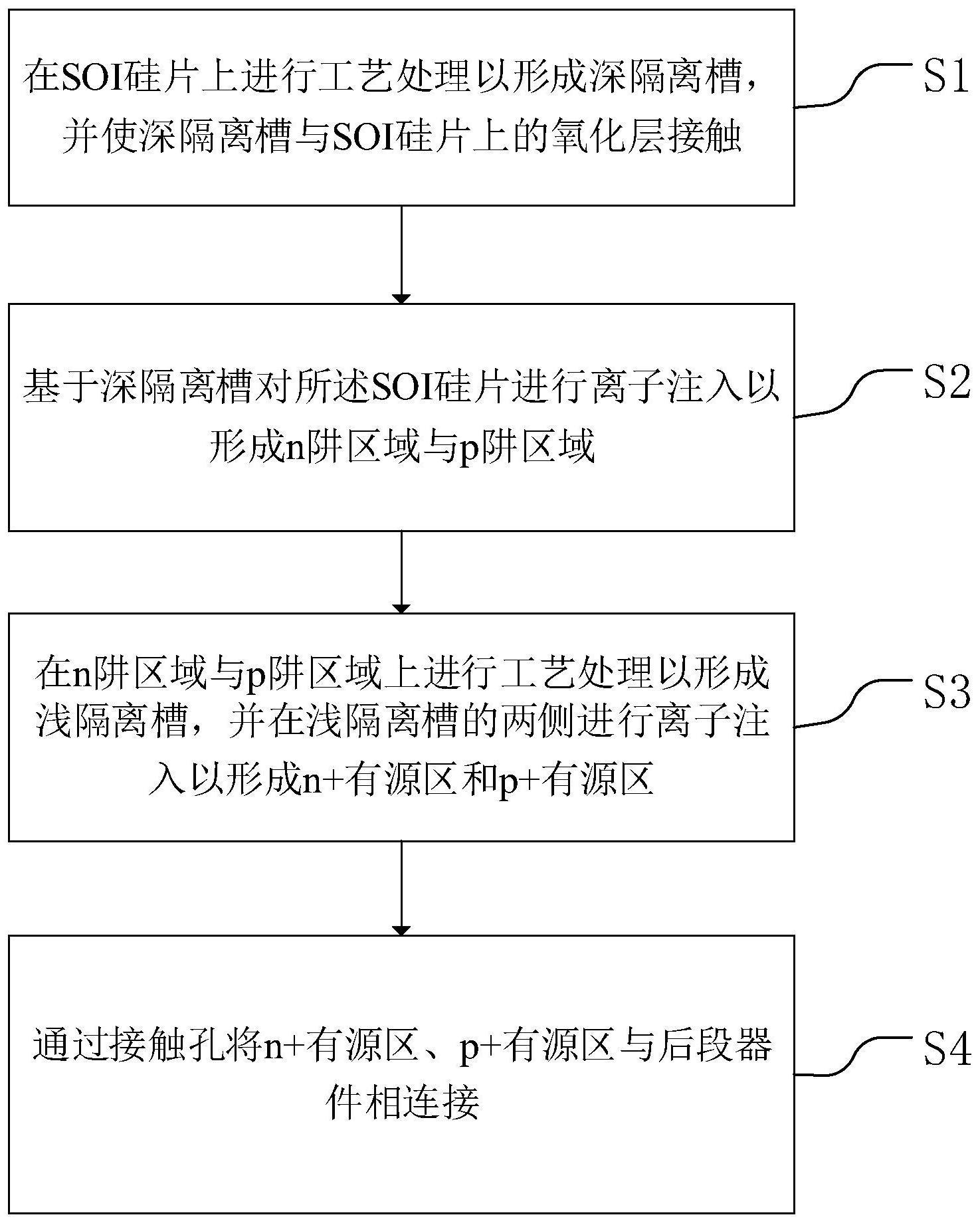

2、本发明提供的一种隔离改进的2d1r工艺方法,其中,包括:

3、在soi硅片上进行工艺处理以形成深隔离槽,并使所述深隔离槽与所述soi硅片上的氧化层接触;

4、基于所述深隔离槽对所述soi硅片进行离子注入以形成n阱区域与p阱区域;

5、在所述n阱区域与p阱区域上进行工艺处理以形成浅隔离槽,并在所述浅隔离槽的两侧进行离子注入以形成n+有源区和p+有源区;

6、通过接触孔将所述n+有源区、所述p+有源区与后段器件相连接。

7、优选地,所述工艺处理至少包括曝光处理、刻蚀处理。

8、优选地,在所述n阱区域与p阱区域上进行工艺处理以形成浅隔离槽的过程中,包括:

9、在所述n阱区域与p阱区域上进行曝光处理与刻蚀处理以形成浅隔离槽;

10、在所述浅隔离槽中填充氧化物,并以化学研磨的方式在所述浅隔离槽中填介电材料做隔离。

11、优选地,在进行离子注入以形成n阱区域与p阱区域的过程中,包括:

12、所述n阱区域由n型元素离子注入而成,所述p阱区域由p型元素离子注入而成;并且,

13、在注入元素离子的过程中通过调节注入能量来调结所述n阱区域或所述p阱区域的注入深度,通过调节注入剂量调节所述n阱区域或所述p阱区域的浓度;其中,

14、所述n阱区域与所述p阱区域的深度与浓度形成有n阱与p阱间反偏漏电,并且形成正偏电流。

15、优选地,所述n阱区域与所述p阱区域形成为二极管阵列。

16、优选地,所述后段器件包括金属层和rram器件。

17、优选地,通过接触孔将所述n+有源区、所述p+有源区与后段器件相连接的过程,包括:

18、通过所述接触孔使所述n阱区域中的n+有源区经由所述金属层与字线相连接;

19、通过所述接触孔使所述p阱区域中的p+有源区经由所述金属层与reset线相连接;

20、通过所述接触孔使所述n阱区域中的p+有源区、所述p阱区域中的n+有源区经由所述金属层与所述rram器件相连接。

21、本发明还提供一种隔离改进的2d1r阵列,通过如前所述的隔离改进的2d1r工艺方法生成,包括soi硅片,其中,

22、在所述soi硅片上设置有深隔离槽,且所述深隔离槽与所述soi硅片上的氧化层接触;

23、在所述soi硅片上设置有n阱区域与p阱区域;其中,所述n阱区域与p阱区域通过离子注入而形成,且所述n阱区域与p阱区域由所述深隔离槽相互隔离;

24、在所述n阱区域与p阱区域上形成有浅隔离槽,在所述浅隔离槽的两侧分别设置有n+有源区和p+有源区;其中,所述n+有源区和p+有源区通过离子注入而形成;

25、所述n+有源区、所述p+有源区通过接触孔与后段器件相连接。

26、优选地,所述n阱区域与所述p阱区域形成为二极管阵列。

27、优选地,所述n阱区域中的n+有源区通过所述接触孔经由所述金属层与字线相连接;

28、所述p阱区域中的p+有源区通过所述接触孔经由所述金属层与reset线相连接;

29、所述n阱区域中的p+有源区、所述p阱区域中的n+有源区通过所述接触孔经由所述金属层与所述rram器件相连接。

30、从上面的技术方案可知,本发明提供的隔离改进的2d1r工艺方法及2d1r阵列,在soi硅片上进行工艺处理以形成深隔离槽,并使深隔离槽与soi硅片上的氧化层接触;再基于深隔离槽对所述soi硅片进行离子注入以形成n阱区域与p阱区域;在n阱区域与p阱区域上进行工艺处理以形成浅隔离槽,并在浅隔离槽的两侧进行离子注入以形成n+有源区和p+有源区;通过接触孔将n+有源区、p+有源区与后段器件相连接,从而通过采用soi技术,可以在降低隔离槽深度的条件下实现更好的阱与阱的隔离效果,同时也可以形成n阱与p阱交替存在的二极管阵列,改善了工艺窗口,实现更小单元尺寸的2d1r阵列。

技术特征:

1.一种隔离改进的2d1r工艺方法,其特征在于,包括:

2.如权利要求1所述的隔离改进的2d1r工艺方法,其特征在于,

3.如权利要求2所述的隔离改进的2d1r工艺方法,其特征在于,在所述n阱区域与p阱区域上进行工艺处理以形成浅隔离槽的过程中,包括:

4.如权利要求1所述的隔离改进的2d1r工艺方法,其特征在于,在进行离子注入以形成n阱区域与p阱区域的过程中,包括:

5.如权利要求1所述的隔离改进的2d1r工艺方法,其特征在于,

6.如权利要求5所述的隔离改进的2d1r工艺方法,其特征在于,

7.如权利要求6所述的隔离改进的2d1r工艺方法,其特征在于,通过接触孔将所述n+有源区、所述p+有源区与后段器件相连接的过程,包括:

8.一种隔离改进的2d1r阵列,通过如权利要求1-7任一所述的隔离改进的2d1r工艺方法生成,包括soi硅片,其中,

9.如权利要求8所述的隔离改进的2d1r阵列,其特征在于,

10.如权利要求9所述的隔离改进的2d1r阵列,其特征在于,

技术总结

本发明提供一种隔离改进的2D1R工艺方法及2D1R阵列,在SOI硅片上进行工艺处理以形成深隔离槽,并使深隔离槽与SOI硅片上的氧化层接触;再基于深隔离槽对所述SOI硅片进行离子注入以形成n阱区域与p阱区域;在n阱区域与p阱区域上进行工艺处理以形成浅隔离槽,并在浅隔离槽的两侧进行离子注入以形成n+有源区和p+有源区;通过接触孔将n+有源区、p+有源区与后段器件相连接,从而通过采用SOI技术,可以在降低隔离槽深度的条件下实现更好的阱与阱的隔离效果,同时也可以形成n阱与p阱交替存在的二极管阵列,改善了工艺窗口,实现更小单元尺寸的2D1R阵列。

技术研发人员:曹恒,仇圣棻

受保护的技术使用者:昕原半导体(上海)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!