半导体结构及其制造方法与流程

本发明是关于半导体结构及其制造方法,特别是关于具有自对准接触插塞(self-aligned contact plugs)的半导体结构及其制造方法。

背景技术:

1、半导体产业持续地改善不同的电子组件的整合密度,借由持续降低最小元件尺寸,让更多组件能够在给定的面积中整合。例如,被广泛地应用在电力开关(power switch)元件的沟槽式栅极金属氧化物半导体场效应应晶体管,便是利用垂直结构的设计,以提升功能密度。其利用晶片的背面作为漏极,而于晶片的正面制作多个晶体管的源极以及栅极。

2、然而,随着半导体装置的功能密度不断提升,处理及制造半导体装置的复杂度亦跟着增加。例如,因受限于传统光刻曝光机台的对准能力,导致沟槽式栅极金氧半导体场效应晶体管的接触结构的特征尺寸无法缩小,而无法有效地降低装置的导通电阻(on-resistance;ron)。再者,由于机台能力或工艺限制,所形成的部件可能会有叠对(overlay)不准确的情况发生,而产生许多问题,使半导体装置的电性表现不稳定。

技术实现思路

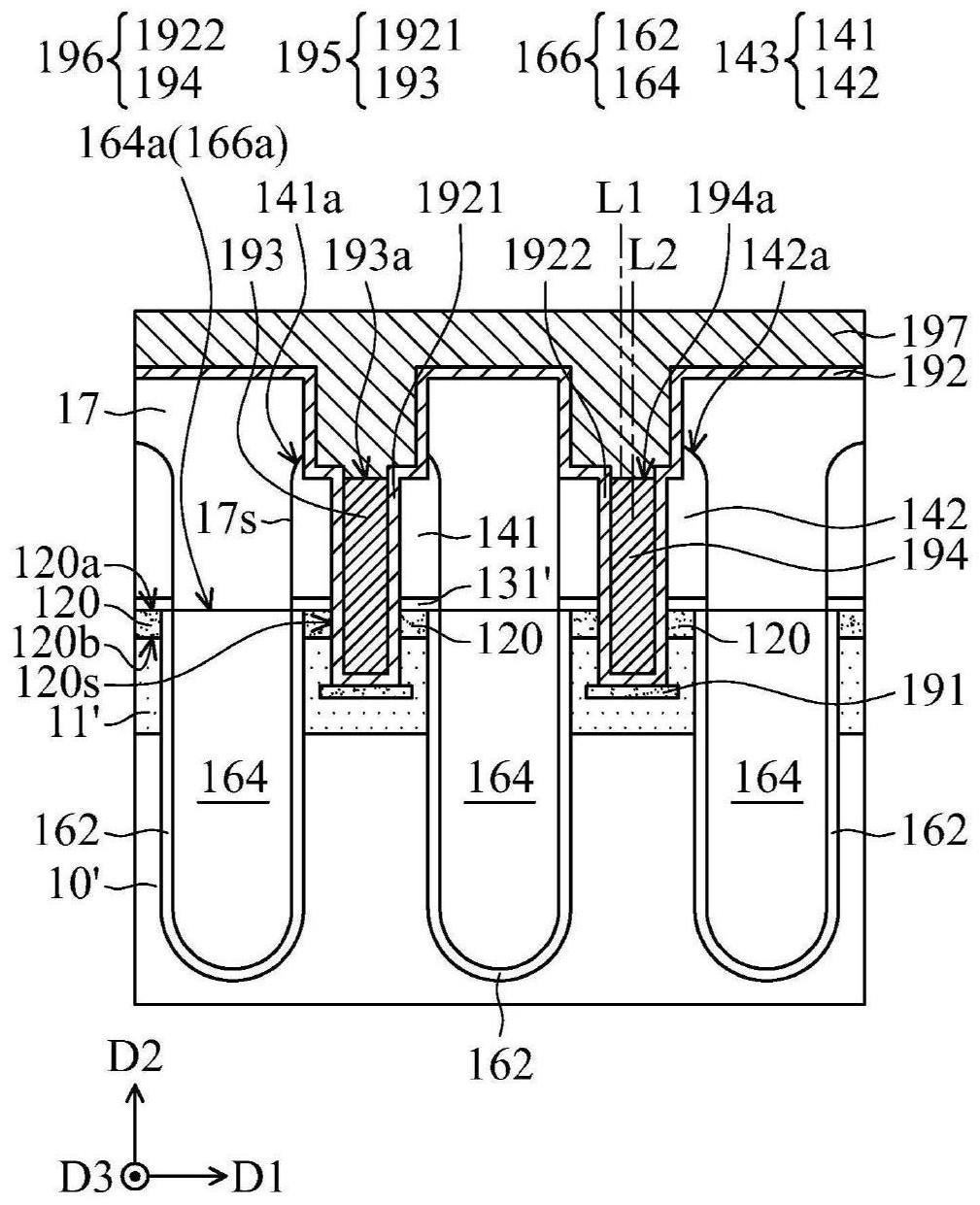

1、本申请的一些实施例提供一种半导体结构,包括一基底、位于基底中的栅极结构、分别位于相应的栅极结构上的介电部、与所述多个介电部的侧壁相邻且沿着介电部的侧壁延伸的间隔物(spacers)、位于基底与间隔物之间的源极区(source regions)、以及位于相邻的栅极结构之间并与相应的源极区接触的接触插塞(contact plugs)。所述多个源极区相邻于栅极结构。所述多个间隔物的侧壁分别与下方相应的源极区的侧壁齐平。

2、本申请的一些实施例提供一种半导体结构的制造方法,包括提供一基底;形成多个栅极结构,在该基底中;形成多个遮罩条,所述多个遮罩条在基底的第一方向上相隔开,且所述多个栅极结构与所述多个遮罩条于一垂直投影方向上不重叠;形成一间隔物层,于所述多个遮罩条的两侧,各遮罩条与间隔物层形成一图案化遮罩层;形成多个介电部覆盖所述多个栅极结构与此图案化遮罩层;移除所述多个遮罩条,形成多个开口;以及形成多个接触插塞,填入所述多个开口。

3、本申请内容的实施例提供了半导体结构及其制造方法,可制得具有自对准的接触插塞和自对准的栅极结构,并且使可接受的叠对偏移的工艺窗口得以扩大,使半导体结构的电性表现更为稳定,进而改善半导体结构的电子特性和可靠度。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述多个介电部分别与相应的所述多个栅极结构直接接触。

3.如权利要求1所述的半导体结构,其特征在于,所述多个间隔物与相应的所述多个介电部的所述多个侧壁直接接触,且所述多个间隔物的顶表面不超过所述多个介电部的顶表面。

4.如权利要求1所述的半导体结构,其特征在于,所述多个栅极结构的顶表面不超过所述多个源极区的顶表面或高于所述多个源极区的底表面。

5.如权利要求1所述的半导体结构,其特征在于,所述多个接触插塞的各个接触插塞的相对两侧壁到相邻的所述多个栅极结构的距离相等。

6.如权利要求1所述的半导体结构,其特征在于,所述多个栅极结构在第一方向上分隔开来,所述多个接触插塞的各个接触插塞的两侧所接触的所述多个源极区沿着该第一方向具有相同宽度。

7.如权利要求1所述的半导体结构,其特征在于,所述多个间隔物的一最顶表面高于所述多个接触插塞的顶表面。

8.如权利要求1所述的半导体结构,其特征在于,更包括:

9.如权利要求1所述的半导体结构,其特征在于,更包括一注入层,所述多个源极区位于该注入层上,所述多个接触插塞延伸至该注入层中。

10.一种半导体结构的制造方法,其特征在于,包括:

11.如权利要求10所述的半导体结构的制造方法,其特征在于,形成所述多个栅极结构包括:

12.如权利要求11所述的半导体结构的制造方法,其特征在于,在形成所述多个栅极结构之前,更包括:

13.如权利要求12所述的半导体结构的制造方法,其特征在于,形成所述多个遮罩条包括:

14.如权利要求13所述的半导体结构的制造方法,其特征在于,形成所述多个栅极结构包括:

15.如权利要求14所述的半导体结构的制造方法,其特征在于,在所述多个栅极结构的上方形成所述多个介电部包括:

16.如权利要求15所述的半导体结构的制造方法,其特征在于,形成所述多个接触插塞包括:

技术总结

本申请公开一种半导体结构及其制造方法,其中,所述半导体结构,包括一基底、位于该基底中的栅极结构、分别位于相应的栅极结构上的介电部、与所述多个介电部的侧壁相邻且沿着介电部的侧壁延伸的间隔物、位于基底与间隔物之间的源极区、以及位于相邻的栅极结构之间并与相应的源极区接触的接触插塞。所述多个源极区相邻于栅极结构。所述多个间隔物的侧壁分别与下方相应的源极区的侧壁齐平。

技术研发人员:廖柏翔,傅胜威,李宗晔

受保护的技术使用者:世界先进积体电路股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!