一种低副瓣波导缝隙阵列天线及设计方法

1.本发明属于无线通信领域,具体涉及一种低副瓣波导缝隙阵列天线及设计方法。

背景技术:

2.在实际工程应用中,副瓣电平的高低直接影响了天线的性能。副瓣电平越低,说明天线在不需要的方向上发射或者接收的能量越小。所以,低副瓣是非常有必要的。

3.现有基片集成波导缝隙阵列天线的低副瓣设计一般分为e面(平行于电场方向的平面) 和h面(平行于磁场方向的平面)低副瓣设计两个部分。在平行于磁场方向的平面进行赋形时,需要对每个缝隙单元结构进行调整,调整过程相对繁琐;在平行于电场方向的平面进行赋形时,需要设计不等功率功分器,设计过程相对复杂。为解决这些问题,本发明通过对部分缝隙进行反向偏移,使缝隙单元分为同相单元和反相单元。通过对同相单元和反相单元的位置进行优化,同时实现波导缝隙阵列天线在平行于电场方向的平面和平行于磁场方向的平面的二维低副瓣赋形。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明提出了一种低副瓣波导缝隙阵列天线及设计方法。

5.为了实现上述目的,本发明采用的技术方案为:

6.一种基于部分缝隙反向偏移的低副瓣波导缝隙阵列天线,包括若干根侧面为金属壁,一端为馈电端口的波导;相邻波导之间沿垂直于波导长度方向紧密排布;每一根波导上表面开有若干个平行于波导长度方向的尺寸相同的矩形缝隙单元,所述矩形缝隙单元与波导中线的距离相等;所述缝隙单元排布在波导中线两侧,相邻两个缝隙单元若在中线的同一侧,则为反相单元;相邻两个缝隙单元若在中线的两侧,则为同相单元;通过对同相单元和反相单元的位置进行优化,能够同时实现波导缝隙阵列天线在平行于电场方向的平面和平行于磁场方向的平面的二维低副瓣赋形。

7.优选地,所述波导一端接馈电端口,另一端接匹配负载或金属壁。

8.优选地,相邻两个缝隙单元沿上表面中线方向的距离相等。

9.优选地,不同波导上的第一个缝隙单元距离其对应的馈电端口的距离相等。

10.优选地,所有馈电端口在同一平面上。

11.优选地,不同同相单元之间,对应的缝隙单元处于对应中线的同一侧。

12.优选地,波导之间为等功率馈电。

13.本技术还涉及一种低副瓣波导缝隙阵列天线设计方法,通过下述步骤对同相单元和反相单元的位置进行优化:

14.步骤s1:根据缝隙阵列规模,初始化缝隙阵列的相位矩阵为同相矩阵并求解其副瓣电平,记为最优副瓣电平;

15.步骤s2:在已有的相位矩阵的基础上,逐一将相位矩阵中的一个同相单元变化为

反相单元并求解对应的副瓣电平,求解结束后将反相单元还原为同相单元;

16.步骤s3:选取步骤s2中的最低副瓣电平,记为局部最优副瓣电平;

17.步骤s4:若局部最优副瓣电平比最优副瓣电平小,令最优副瓣电平等于局部最优副瓣电平,并按照对应的方式对相位矩阵进行修改,返回步骤s2;若局部最优最优副瓣电平比最优副瓣电平大,则停止计算,输出此时的相位矩阵和最优副瓣电平。

18.优选地,所述步骤s2引入贪婪算法,将问题分解为若干个子问题,每个子问题为对于给定的阵列排布方式及其激励相位矩阵φ,将其中一个缝隙天线进行反向偏移,求解副瓣下降最多的激励矩阵φ1。

19.本技术还涉及一种低副瓣波导缝隙阵列天线,由若干根四周为金属壁,一端为馈电端口的矩形波导组成。波导沿垂直于馈电端口短边的方向紧密相连。每一根波导上表面开有若干个平行于其中线的尺寸相同的缝隙单元,缝隙单元与波导中线的距离相等,相邻两个缝隙单元沿上表面中线方向的距离相等。缝隙单元排布在中线两侧,相邻两个缝隙单元若在中线的同一侧,则组为反相单元;相邻两个缝隙单元若在中线的两侧,则组成同相单元。通过对同相单元和反相单元进行排列组合,实现波导缝隙阵列天线的低副瓣赋形。

20.优选地,所述矩形波导一端接馈电端口,另一端可以接匹配负载,也可以接金属壁形成短路端。不同矩形波导的馈电端口在同一平面上,各矩形波导之间的馈电功率相等。

21.优选地,所述不同波导上的第一个缝隙单元距离其对应的馈电端口的距离相等,相邻两个缝隙单元沿上表面中线方向的距离相等。

22.优选地,所述同相单元之间,对应的缝隙单元处于其对应的中线的同一侧。

23.本发明的工作原理在于:

24.在波导缝隙线阵中,如果相邻两个缝隙单元放置在波导中线的同一侧,这两个缝隙单元之间就有180

°

的相位差;若相邻两个缝隙单元放置在波导中线的不同侧,这两个缝隙单元之间就不存在相位差。因此,在波导缝隙天线中,不改变缝隙单元的结构,仅仅改变部分缝隙的偏移方向,就可以很容易地实现单元幅度相等,但相位相差180

°

。基于这个性质,可以对波导缝隙阵列天线进行低副瓣设计。

25.对于一个规模为2m

×

2n的位于xoy平面上的阵列天线,每一个单元都是一个理想点源。并且该阵列是关于x轴和y轴对称,对称位置上的激励相同,那么其阵因子可以表示为:

[0026][0027]

其中,m和n分别表示x轴和y轴方向上的阵元数的一半。j表示虚数单位,j2=-1。u表示sinθcosψ,v表示sinθsinψ,θ是俯仰角,ψ是方位角。d

x

和dy分别表示x轴和y轴方向的阵元间距。β是相位常数。i是激励幅度矩阵,i

mn

表示第mn个阵元的激励幅度,每个阵元激励幅度相等,取为1。φ是激励相位矩阵,φ

mn

表示第mn个阵元的激励,取值为0

°

和180

°

。以这个公式为基础,通过调控阵元的相位,就可以实现低副瓣赋形。

[0028]

本发明提供的一种基于部分缝隙反向的低副瓣波导缝隙天线阵及设计方法,与现有技术相比,至少具备有以下有益效果:

[0029]

(1)通过调整反相单元的位置,能够同时实现在平行于电场方向的平面和平行于

磁场方向的平面的低副瓣赋形,避免了复杂繁琐的单元结构尺寸设计;

[0030]

(2)通过引入贪婪算法,通过求解一系列子问题实现了低副瓣阵列天线的设计,提高了算法的性能。

附图说明

[0031]

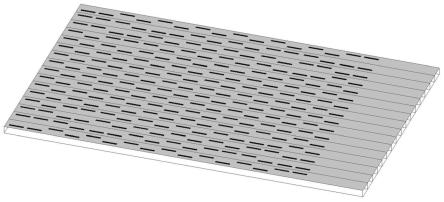

图1是本发明基于部分缝隙反向偏移的低副瓣波导缝隙阵列天线示意图;

[0032]

图2是本发明实施例的整体结构图;

[0033]

图3是本发明实施例的背面结构示意图;

[0034]

图4是本发明实施例的正面结构示意图;

[0035]

图5是本发明实施例的缝隙天线阵列示意图;

[0036]

图6是本发明实施例1的一分二等功率功分器示意图;

[0037]

图7是本发明的设计方法流程图。

[0038]

图8是本发明实施例的单元相位示意图。

[0039]

图9是本发明实施例的三维方向图(俯视图)。

[0040]

图10是本发明实施例的三维方向图(侧视图)。

[0041]

图11是本发明实施例在e、h面方向图。

[0042]

其中,1为下层金属地,2为中间介质层,3为上层金属,11为耦合口径,21为金属化通孔,22为基片集成波导,23为等功率功分网络,24为一分二等功率功分器,31为缝隙辐射单元,35为缝隙天线子阵,36~41为缝隙天线子阵中的反相双缝单元,241为中心调谐孔, 242和243为侧边调谐孔。

具体实施方式

[0043]

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点和功效。本发明还可以通过另外不同的具体实施方式加以实施或运用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

[0044]

实施例一

[0045]

首先使用本发明所提出的基于部分缝隙反向偏移的低副瓣波导缝隙阵列设计方法对16

×ꢀ

16的阵列天线进行设计,设计步骤如下:

[0046]

(1)首先确定缝隙阵列天线的大小为16

×

16,初始化阵列激励相位矩阵φ和最优副瓣电平sllb,确定子问题;

[0047]

(2)进入子问题,依次对阵列中的第i个缝隙天线进行反向偏移,获得对应激励相位矩阵φi;

[0048]

(3)计算激励相位矩阵φ

explorei

对应的阵因子,并求解出其对应的最大副瓣电平slli,并存入矩阵slle;若i《m

×

n,转入(2)。否则令slln=max(slle),转入(4)。

[0049]

(4)比较slln与sllb,如果slln》sllb,将max(sll

explore

)赋给sllb,对应的φ

explorei

赋给φ。转入步骤(2)。否则结束循环,输出φ和sllb。

[0050]

针对16

×

16的阵列天线,可以得到阵列的排布方式如图8所示,对应的结果如图9、图 10和图11所示。

[0051]

依托算法设计结果对该低副瓣波导缝隙阵列天线进行加工制作。

[0052]

如图1所示,一种基于部分缝隙反向偏移的低副瓣波导缝隙阵列天线。如图2所示,低副瓣波导缝隙阵列天线从下往上依次层叠:下层金属地1、中间介质层2、上层金属3;

[0053]

如图3所示,下层金属地1刻蚀有一个耦合口径11,被标准矩形波导的wr-10用作馈电窗口;中间介质层的金属化通孔21与下层金属地1、上层金属3一起构成了16根紧密相连的基片集成波导22和一个1分16的等功率功分网络23。1分16等功率功分网络23由四级结构相同的一分二等功率功分器24组成。

[0054]

如图4所示,上层金属刻3蚀有16

×

16个尺寸相同的缝隙单元31。

[0055]

如图5所示,缝隙单元31组成的缝隙阵列上下左右对称,由四个对称的缝隙阵列子阵35组成。每一个缝隙阵列子阵中含有6个反相单元36~41,其余均为同相单元。

[0056]

如图6所示,一分二等功率功分器24有一个中心调谐柱241和两个侧边调谐柱242、243。一分二等功率功分器左右对称,枝节宽度为1.65mm,中心调谐孔位于对称轴上,偏置量 cy=0.65mm,侧边调谐孔的偏置量rx=0.65mm,ry=0.5mm。

[0057]

具体的,相邻两个缝隙单元的横向距离为1.6mm,一个缝隙单元的长度为1.22mm,宽度为0.1mm,与基片集成波导中线的距离为0.06mm,最左端缝隙单元距末端金属通孔中心为 0.8mm。

[0058]

一分二等功率功分器左右对称,枝节宽度为1.65mm,中心调谐孔位于对称轴上,偏置量 cy=0.65mm,侧边调谐孔的偏置量rx=0.65mm,ry=0.5mm。

[0059]

基片集成波导的宽度为1.65mm,金属化通孔的直径为0.3mm,金属化通孔的间距为 0.5mm。

[0060]

本实施例的工作频率为94ghz,选用的基板为taconic tly-5,中间介质层的厚度为 0.508mm,上层金属和下层金属地的厚度为0.018mm。相邻两个缝隙单元的横向距离为1.6mm,一个缝隙单元的长度为1.22mm,宽度为0.1mm,与基片集成波导中线的距离为0.06mm,最左端缝隙单元距末端金属通孔中心为0.8mm。缝隙阵列天线上下左右对称,由四个对称的缝隙天线子阵构成。缝隙天线子阵中含有6个反相双缝单元36~41,其余均为同相双缝单元。

[0061]

如图7所示,该低副瓣波导缝隙阵列天线设计方法包括初始化相位和矩阵和副瓣电平、求解子问题的循环和输出副瓣电平和相位矩阵三个大的部分,其中求解子问题的循环部分又分为依次改变相位矩阵中的元素并记录其对应的副瓣电平sllb、将其中最好的副瓣电平命名为slln并记录其对应的相位矩阵、比较slln与sllb的大小、令sllb=slln并更新相位矩阵三个部分。

[0062]

如图8所示,通过该低副瓣波导缝隙阵列天线设计方法,可以得到同相单元和反相单元的分布图,图中白色单元表示反相单元,黑色单元表示同相单元。

[0063]

如图9所示,该低副瓣波导缝隙阵列天线设计方法设计得到的阵列的三维方向图对称性良好。

[0064]

如图10所示,该低副瓣波导缝隙阵列天线设计方法设计得到的阵列的三维方向图的副瓣保持在-18db的水平。

[0065]

如图11所示,该低副瓣波导缝隙阵列天线设计方法设计得到的阵列的在平行于电场方向的平面和平行于磁场方向的平面的方向图副瓣均保持在-18db以下的水平。

[0066]

以上所述,上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1