测试键结构及使用测试键结构的监测方法与流程

本发明涉及一种测试键(testkey)结构以及使用测试键结构的监测方法,特别是涉及一种用于半导体装置的测试键结构以及使用测试键结构监测半导体装置内的间距(spacing)的方法。

背景技术:

1、随着集成电路的发展,耗电量少且适合高集成度的金属氧化物半导体(metal-oxide-semiconductor,mos)晶体管已被广泛地应用于半导体制作工艺中。mos晶体管一般包括栅极(gate)以及位于两侧的两掺杂区,是分别作为源极(source)与漏极(drain)。在一些情况下,为了能进一步增加mos晶体管的载流子迁移率,还可选择利用选择性外延成长(selective epitaxial growth,seg)技术于两掺杂区内形成外延结构,例如硅锗(silicongermanium,sige)外延结构。

2、而在半导体先进制作工艺领域中,相邻的两个mos晶体管之间的结构健康度,特别是指两个硅锗外延结构之间的距离控制,为制作工艺中最关键的步骤,当两个mos晶体管之间的浅沟槽隔离(shallow trench isolation,sti)的位置偏高、两掺杂区的涵盖范围较广、或者是外延结构的结构偏大的时候,都会对两个mos晶体管之间的结构健康度造成严重影响。一般来说,为确保产品量产后品质的稳定,需对所生产的元件不断地进行测试,目前已知可通过测量表面距离的软件,如pro-v测量工具等于相对应的制作工艺阶段测量硅锗外延结构之间的距离,然而,该pro-v测量工具无法即时地且全面性地发现所有产品的结构缺失,以致往往于量产时容易衍生电流渗漏,甚至是低良率(low yield)等问题。因此,现行技术还待进一步改良,以便能有效地监测半导体装置内相邻结构之间的结构健康度。

技术实现思路

1、本发明的一目的在于提供一种测试键结构以及使用测试键结构的监测方法,是将测试键结构设置于每一片芯片(wafer)上以便能快速、准确且以非破坏性的手段监测特定半导体结构之间的间距。如此,本发明有利于提升半导体制作工艺的健康度,有效地避免因结构瑕疵所衍生的电流渗漏,进而可提升产品量产后的良率。

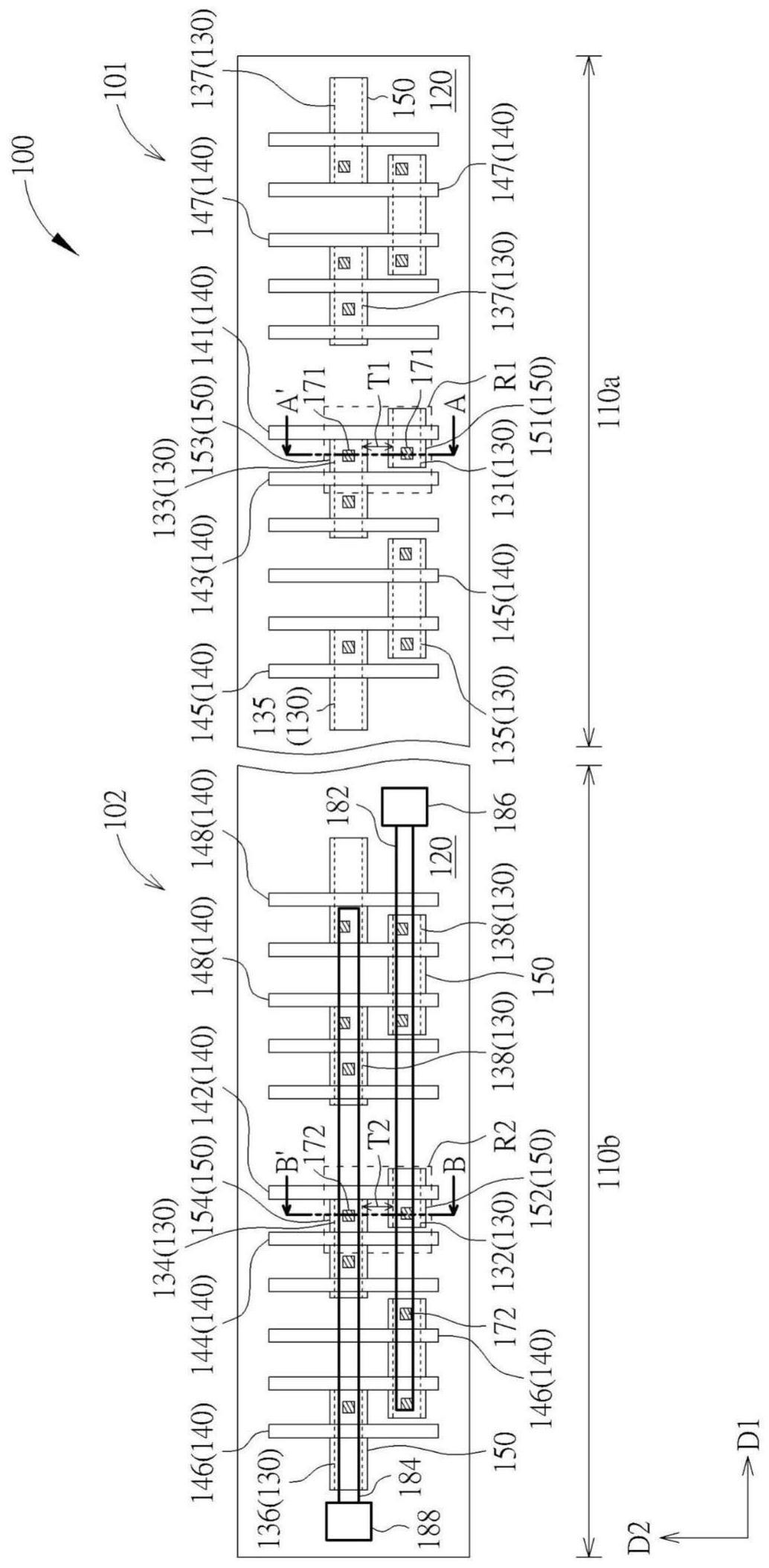

2、为达上述目的,本发明提供一种测试键结构,包括第一掺杂区与第二掺杂区、第一栅极与第二栅极、第一外延层与第二外延层、以及输入端与输出端。第一掺杂区与第二掺杂区设置于基底中。第一栅极与第二栅极设置于该基底上,并分别跨过该第一掺杂区与该第二掺杂区。第一外延层与第二外延层分别设置于该第一掺杂区与该第二掺杂区上,其中,该第一外延层与该第二外延层相互分隔地设置于该第一栅极与该第二栅极之间。输入端与输出端分别电连接至该第一外延层与该第二外延层。

3、为达上述目的,本发明另提供一种使用测试键结构的监测方法,包括以下步骤。首先,在半导体装置中提供测试键结构,该测试键结构包括第一掺杂区与第二掺杂区、第一栅极与第二栅极、第一外延层与第二外延层、以及输入端与输出端。其中,第一掺杂区与第二掺杂区设置于基底中,第一栅极与第二栅极设置于该基底上,并分别跨过该第一掺杂区与该第二掺杂区,第一外延层与第二外延层分别设置于该第一掺杂区与该第二掺杂区上。该第一外延层与该第二外延层相互分隔地设置于该第一栅极与该第二栅极之间。输入端与输出端分别电连接至该第一外延层与该第二外延层。接着,在该输入端施加第一信号,并且,通过于该输出端接受第一对应信号计算出该第一外延层与该第二外延层之间的漏电流。

4、本发明是在半导体装置的元件区内设置半导体结构,同时在该半导体装置的测试键区内设置对应于该半导体结构的至少一测试键结构。该元件区内设有第一外延层与第二外延层,其间具有间距,而该测试键区内设有相对应的第一外延层与第二外延层,且其间也具有相同的间距,由此,可利用该测试键区中的该测试键结构对应地模拟、并监测该元件区中的该第一外延层与该第二外延层之间的间距,有效地监控半导体制作工艺的健康度,避免相邻结构之间的结构瑕疵所衍生的电流渗漏,进而可大幅地提升产品量产后的良率。

技术特征:

1.一种测试键结构,其特征在于,包括:

2.依据权利要求1所述的测试键结构,其特征在于,该第一外延层与该第二外延层包括硅锗。

3.依据权利要求1所述的测试键结构,其特征在于,该第一掺杂区、该第二掺杂区、该第一栅极、与该第二栅极共同排列成矩形范围。

4.依据权利要求1所述的测试键结构,其特征在于,还包括:

5.依据权利要求4所述的测试键结构,其特征在于,该第一掺杂区、该第二掺杂区、该些第三掺杂区与该些第四掺杂区相互平行地延伸于第一方向上,该第一栅极、该第二栅极、该些第三栅极、与该些第四栅极相互平行地延伸于第二方向,并且该第一方向垂直于该第二方向。

6.依据权利要求4所述的测试键结构,其特征在于,还包括:

7.依据权利要求4所述的测试键结构,其特征在于,该第一栅极、该第二栅极、该些第三栅极与该些第四栅极设置于该输入端与该输出端之间。

8.依据权利要求1所述的测试键结构,其特征在于,该第一掺杂区与该第二掺杂区、该第一栅极与该第二栅极、该第一外延层与该第二外延层包括至少两个p型金属氧化物半导体晶体管。

9.一种使用测试键结构的监测方法,其特征在于,包括:

10.依据权利要求9所述的使用测试键结构的监测方法,其特征在于,该第一掺杂区、该第二掺杂区、该第一栅极、与该第二栅极共同排列成矩形范围。

11.依据权利要求9所述的使用测试键结构的监测方法,其特征在于,该测试键结构还包括:

12.依据权利要求11所述的使用测试键结构的监测方法,其特征在于,该第一掺杂区、该第二掺杂区、该些第三掺杂区与该些第四掺杂区相互平行地延伸于第一方向上,该第一栅极、该第二栅极、该些第三栅极、与该些第四栅极相互平行地延伸于第二方向,并且该第一方向垂直于该第二方向。

13.依据权利要求11所述的使用测试键结构的监测方法,其特征在于,该第一栅极、该第二栅极、该些第三栅极、与该些第四栅极设置于该输入端与该输出端之间。

14.依据权利要求11所述的使用测试键结构的监测方法,其特征在于,还包括:

15.依据权利要求11所述的使用测试键结构的监测方法,其特征在于,还包括:

16.依据权利要求14所述的使用测试键结构的监测方法,其特征在于,还包括:

17.依据权利要求16所述的使用测试键结构的监测方法,其特征在于,该第三间距不同于该第二间距,该第三间距与该第二间距均介于40纳米至50纳米之间。

18.依据权利要求16所述的使用测试键结构的监测方法,其特征在于,还包括:

19.依据权利要求9所述的使用测试键结构的监测方法,其特征在于,该第一外延层与该第二外延层包括硅锗,且该第一掺杂区与该第二掺杂区、该第一栅极与该第二栅极、该第一外延层与该第二外延层包括至少两个p型金属氧化物半导体晶体管。

技术总结

本发明公开一种测试键结构及使用测试键结构的监测方法,该测试键包括第一掺杂区与第二掺杂区、第一栅极与第二栅极、第一外延层与第二外延层、以及输入端与输出端。第一掺杂区与第二掺杂区设置于基底中,第一栅极与第二栅极设置于基底上,并分别跨过第一掺杂区与第二掺杂区。第一外延层与第二外延层分别设置于第一掺杂区与第二掺杂区上,并且相互分隔地设置于第一栅极与第二栅极之间。输入端与输出端分别电连接至第一外延层与第二外延层。

技术研发人员:刘杭,袁林山,杨光,戴易录,欧阳锦坚,黄清俊,谈文毅

受保护的技术使用者:联芯集成电路制造(厦门)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!