增进打线接合承受力的芯片封装的凸块结构的制作方法

本发明涉及一种芯片封装的凸块结构,尤指一种增进打线接合承受力的芯片封装的凸块结构。

背景技术:

1、在芯片封装领域中,欲使芯片封装与电子元件电性连接,可通过打线接合(wirebonding)的技艺来实现,即通过一焊线以在芯片封装结构上形成一焊点与电子元件上形成另一焊点,以使芯片封装结构与电子元件电性连接在一起。然而,当在进行打线接合作业时,现有的芯片封装结构承受来自打线接合作业或形成该焊点时所产生的正压力,使芯片的内部线路因该正压力而受到破坏,而使内部线路不容易或无法通过或安排在芯片内的各晶垫的下方,为此,制造端需重新安排芯片的内部线路的设计,进而导致制造端成本增加。

2、因此,一种有效地解决制造端需重新安排芯片的内部线路的设计而导致制造端成本增加的问题的增进打线接合承受力的芯片封装的凸块结构,为目前相关产业的迫切期待。

技术实现思路

1、本发明的主要目的在于提供一种增进打线接合承受力的芯片封装的凸块结构,其中该芯片封装的至少一凸块为一具有一定厚度的金属堆叠结构体,且每一该凸块的整体厚度设定为4.5~20微米(μm),以此增进每一该凸块的结构强度以承受来自打线接合(wirebonding)作业或形成一第一焊点时所产生的正压力,使该芯片的至少一内部线路不会因该正压力而受到破坏,而使每一该内部线路能容许通过或安排在该芯片的至少一晶垫(diepad)的下方,有效地解决制造端需重新安排芯片的内部线路的设计而导致制造端成本增加的问题。

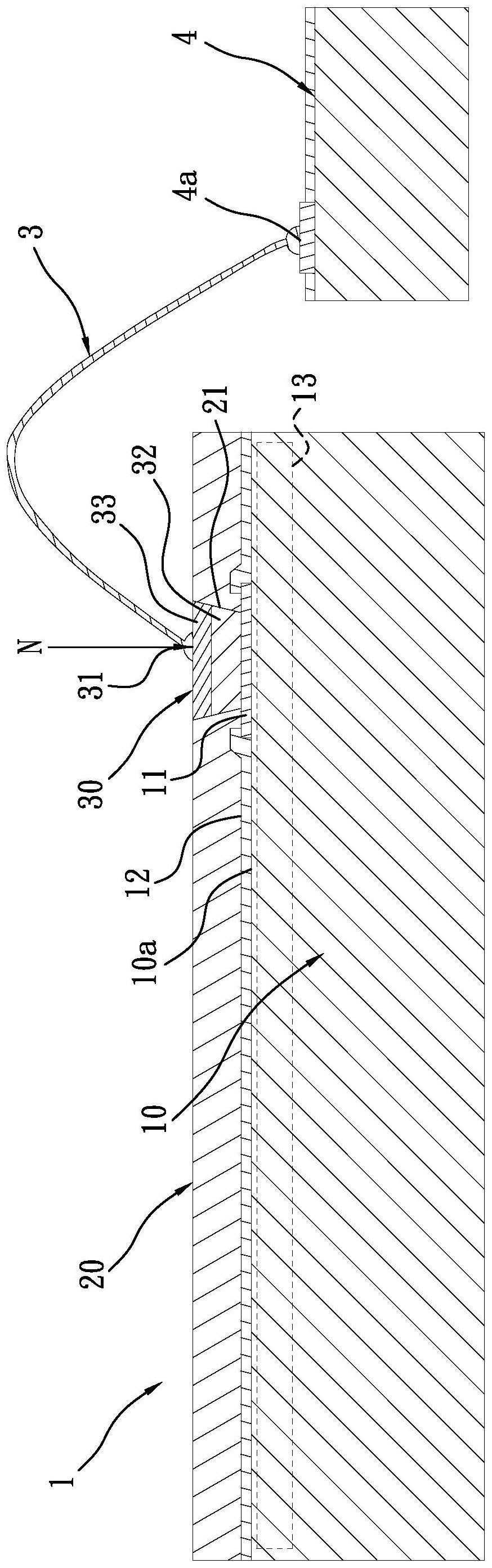

2、为达成上述目的,本发明提供一种增进打线接合承受力的芯片封装的凸块结构,该芯片封装包含一芯片、至少一介电层及至少一凸块;其中该芯片具有一第一表面及至少一内部线路,该第一表面上设有至少一晶垫(die pad)及至少一保护层,其中该芯片是由一晶圆上所分割下来形成;其中每一该介电层对应地覆盖设于该芯片的该第一表面上,每一该介电层具有至少一开口且每一该开口与该芯片的每一该晶垫位置对应;其中每一该凸块设于每一该介电层的每一该开口内并向上露出,且每一该凸块为一层状堆叠结构体且电性连接地设于该芯片的每一该晶垫的顶面上;其中当在进行打线接合(wire bonding)作业时,通过一焊线以在每一该凸块上形成一第一焊点与一电子元件上形成一第二焊点,以使该芯片封装与该电子元件电性连接在一起;该芯片封装中:每一该凸块是一由每一该晶垫的顶面上往上依序包括一镍(ni)层及一金(au)层所组成且具有一定厚度的金属堆叠结构体,其中每一该凸块的整体厚度设定为4.5~20微米(μm),以此增进每一该凸块的结构强度以承受来自打线接合作业或形成该第一焊点时所产生的正压力,使该芯片的每一该内部线路不会因该正压力而受到破坏,而使每一该内部线路能容许通过或安排在每一该晶垫的下方,有利于降低制造端的成本。

3、在本发明一较佳实施例中,该金(au)层在每一该凸块中的所占的厚度为0.005~0.2微米(μm),每一该凸块厚度其余的为该镍(ni)层的厚度。

4、为达成上述目的,本发明还提供一种增进打线接合承受力的芯片封装的凸块结构,该芯片封装包含一芯片、至少一介电层及至少一凸块;其中该芯片具有一第一表面及至少一内部线路,该第一表面上设有至少一晶垫(die pad)及至少一保护层,其中该芯片是由一晶圆上所分割下来形成;其中每一该介电层对应地覆盖设于该芯片的该第一表面上,每一该介电层具有至少一开口且每一该开口与该芯片的每一该晶垫位置对应;其中每一该凸块设于每一该介电层的每一该开口内并向上露出,且每一该凸块为一层状堆叠结构体且电性连接地设于该芯片的每一该晶垫的顶面上;其中当在进行打线接合(wire bonding)作业时,通过一焊线以在每一该凸块上形成一第一焊点与一电子元件上形成一第二焊点,以使该芯片封装与该电子元件电性连接在一起;其中:每一该凸块是一由每一该晶垫的顶面上往上依序包括一镍(ni)层、一钯(pd)层及一金(au)层所组成且具有一定厚度的金属堆叠结构体,其中每一该凸块的整体厚度设定为4.5~20微米(μm),以此增进每一该凸块的结构强度以承受来自打线接合作业或形成该第一焊点时所产生的正压力,使该芯片的每一该内部线路不会因该正压力而受到破坏,而使每一该内部线路能容许通过或安排在每一该晶垫的下方,有利于降低制造端的成本。

5、在本发明一较佳实施例中,该金(au)层在每一该凸块中的所占的厚度为0.005~0.2微米(μm),该钯(pd)层在每一该凸块中的所占的厚度为0.005~0.3微米(μm),每一该凸块其余的厚度为该镍(ni)层的厚度。

技术特征:

1.一种增进打线接合承受力的芯片封装的凸块结构,该芯片封装包含一芯片、至少一介电层及至少一凸块;其中该芯片具有一第一表面及至少一内部线路,该第一表面上设有至少一晶垫及至少一保护层,其中该芯片是由一晶圆上所分割下来形成;其中每一该介电层对应地覆盖设于该芯片的该第一表面上,每一该介电层具有至少一开口且每一该开口与该芯片的每一该晶垫位置对应;其中每一该凸块设于每一该介电层的每一该开口内并向上露出,且每一该凸块为一层状堆叠结构体且电性连接地设于该芯片的每一该晶垫的顶面上;其中当在进行打线接合作业时,通过一焊线以在每一该凸块上形成一第一焊点与一电子元件上形成一第二焊点,以使该芯片封装与该电子元件电性连接在一起;其特征在于:

2.如权利要求1所述的芯片封装的凸块结构,其特征在于,该金层在每一该凸块中的所占的厚度为0.005~0.2微米,每一该凸块其余的厚度为该镍层的厚度。

3.一种增进打线接合承受力的芯片封装的凸块结构,该芯片封装包含一芯片、至少一介电层及至少一凸块;其中该芯片具有一第一表面及至少一内部线路,该第一表面上设有至少一晶垫及至少一保护层,其中该芯片是由一晶圆上所分割下来形成;其中每一该介电层对应地覆盖设于该芯片的该第一表面上,每一该介电层具有至少一开口且每一该开口与该芯片的每一该晶垫位置对应;其中每一该凸块设于每一该介电层的每一该开口内并向上露出,且每一该凸块为一层状堆叠结构体且电性连接地设于该芯片的每一该晶垫的顶面上;其中当在进行打线接合作业时,通过一焊线以在每一该凸块上形成一第一焊点与一电子元件上形成一第二焊点,以使该芯片封装与该电子元件电性连接在一起;其特征在于:

4.如权利要求3所述的芯片封装的凸块结构,其特征在于,该金层在每一该凸块中的所占的厚度为0.005~0.2微米,该钯层在每一该凸块中的所占的厚度为0.005~0.3微米,每一该凸块其余的厚度为该镍层的厚度。

技术总结

本发明公开一种增进打线接合承受力的芯片封装的凸块结构,其中该芯片封装的至少一凸块为一具有一定厚度的金属堆叠结构体,且每一该凸块的整体厚度设定为4.5~20微米(μm),以此增进每一该凸块的结构强度以承受来自打线接合(Wire Bonding)作业或形成一第一焊点时所产生的正压力,使该芯片的至少一内部线路不会因该正压力而受到破坏,而使每一该内部线路能容许通过或安排在该芯片的至少一晶垫(Die Pad)的下方,有效地解决制造端需重新安排芯片的内部线路的设计而导致制造端成本增加的问题,有利于降低制造端的成本。

技术研发人员:于鸿祺,林俊荣,古瑞庭

受保护的技术使用者:华东科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!