半导体器件及其形成方法与流程

本公开涉及半导体器件及其形成方法。

背景技术:

1、半导体器件被用于各式各样电子应用中,例如个人计算机、手机、数码相机和其他电子设备。通常通过以下过程来制造半导体器件:在半导体衬底上按顺序执行沉积绝缘或电介质层、导电层和半导体材料层,并使用光刻对各种材料层进行图案化以在其上形成电路组件和元件。

2、半导体行业通过不断减小最小特征尺寸来不断提高各种电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度,这允许将更多的组件集成到给定区域中。然而,随着最小特征尺寸的减小,出现了应解决的其他问题。

技术实现思路

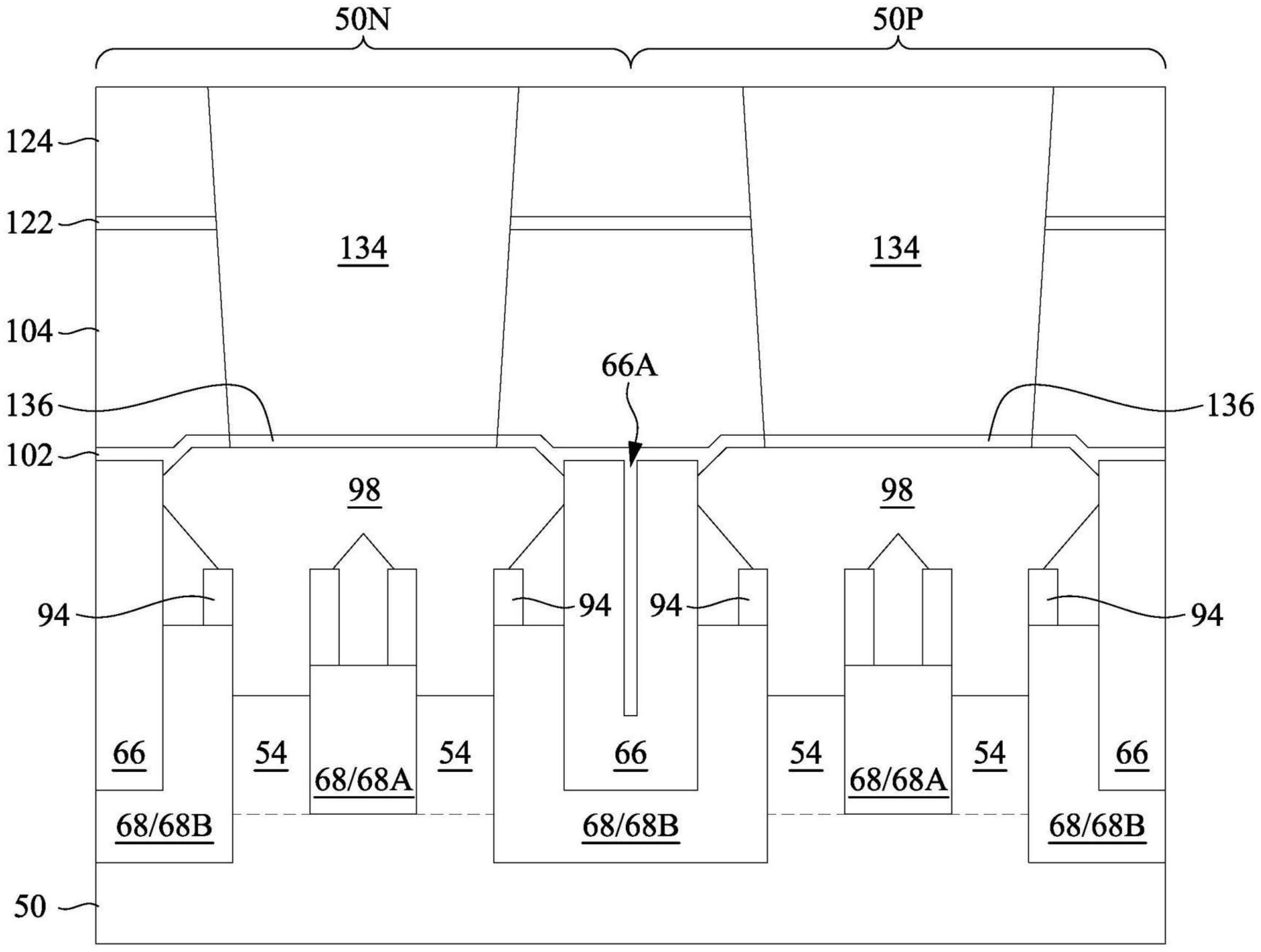

1、根据本公开的一方面,提供了一种半导体器件,包括:从衬底延伸出的第一半导体鳍;从所述衬底延伸出的第二半导体鳍;在所述衬底之上的混合鳍,所述混合鳍布置在所述第一半导体鳍与所述第二半导体鳍之间,所述混合鳍具有从所述混合鳍的顶表面向下延伸的氧化物内部;第一隔离区域,在所述第二半导体鳍、所述第一半导体鳍和所述混合鳍之间,所述混合鳍延伸得高于所述第一隔离区域的顶表面;在所述混合鳍的侧壁、所述第一半导体鳍的侧壁和所述第二半导体鳍的侧壁之上的高k栅极电介质;在所述高k栅极电介质上的栅电极;以及在所述第一半导体鳍上位于所述栅电极的相反侧的源极/漏极区域。

2、根据本公开的一方面,提供了一种形成半导体器件的方法,包括:形成从衬底延伸出的第一半导体鳍和第二半导体鳍;在所述第一半导体鳍和所述第二半导体鳍周围形成绝缘材料,所述绝缘材料的第一部分布置在所述第一半导体鳍与所述第二半导体鳍之间;在所述绝缘材料的第一部分上形成混合鳍,所述混合鳍具有在其中的接缝;使所述绝缘材料的第一部分凹陷以形成第一隔离区域;在所述第一半导体鳍、所述混合鳍和所述第二半导体鳍之上形成虚设栅极结构;在所述第一半导体鳍和所述第二半导体鳍上,在所述虚设栅极结构的相反侧形成源极/漏极区域;去除所述虚设栅极结构,以形成栅极沟槽;在所述栅极沟槽中,形成在所述第一半导体鳍、所述混合鳍和所述第二半导体鳍上的第一栅极电介质层,所述第一栅极电介质层填充所述混合鳍中的接缝;在所述栅极沟槽中,形成在所述第一栅极电介质层上的第二栅极电介质层;并且在所述栅极沟槽中,形成在所述第二栅极电介质层上的栅电极层。

3、根据本公开的一方面,提供了一种形成半导体器件的方法,包括:形成从衬底延伸出的第一半导体鳍;在所述第一半导体鳍周围形成绝缘材料;在所述第一半导体鳍周围的绝缘材料上沉积电介质层;并且去除所述电介质层的部分以形成电介质鳍,所述电介质鳍具有在其中的接缝;使所述绝缘材料凹陷,其中,在使所述绝缘材料凹陷之后,所述电介质鳍延伸得高于所述绝缘材料的顶表面;在所述第一半导体鳍、所述电介质鳍和凹陷的绝缘材料之上形成虚设栅极结构;在所述第一半导体鳍上,在所述虚设栅极结构的相反侧形成源极/漏极区域;去除所述虚设栅极结构以形成栅极沟槽;在所述栅极沟槽中执行硅前体浸泡工艺;并且在执行所述硅前体浸泡工艺之后,在所述栅极沟槽中执行氧化工艺,以在所述栅极沟槽中形成在所述第一半导体鳍和所述电介质鳍上的界面层,所述界面层填充所述电介质鳍中的接缝;在所述栅极沟槽中,形成在所述界面层上的高k栅极电介质层;并且在所述栅极沟槽中,形成在所述高k栅极电介质层上的栅电极层。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的器件,其中,所述混合鳍、所述第一半导体鳍和所述第二半导体鳍的顶表面彼此齐平。

3.根据权利要求1所述的器件,其中,所述第一半导体鳍包括在所述第一半导体鳍的侧壁与所述高k栅极电介质之间的界面氧化物层。

4.根据权利要求3所述的器件,其中,所述混合鳍的氧化物内部比所述界面氧化物层更富含硅。

5.根据权利要求1所述的器件,其中,所述混合鳍包括氮化硅、氧化钽、氧化铝、氧化锆、氧化铪、碳氮化硅、碳氮氧化硅、或它们的组合。

6.根据权利要求1所述的器件,还包括:

7.根据权利要求6所述的器件,其中,所述第一隔离区域的底表面布置得比所述第二隔离区域的底表面更远离所述混合鳍、所述第一半导体鳍和所述第二半导体鳍的顶表面。

8.一种形成半导体器件的方法,包括:

9.根据权利要求8所述的方法,其中,形成所述混合鳍包括:

10.一种形成半导体器件的方法,包括:

技术总结

本公开涉及半导体器件及其形成方法。一实施例包括一种器件,该器件包括:从衬底延伸出的第一半导体鳍、从衬底延伸出的第二半导体鳍、在衬底之上的混合鳍,混合鳍布置在第一半导体鳍与第二半导体鳍之间,并且混合鳍具有从混合鳍的顶表面向下延伸的氧化物内部。该器件还包括:在第二半导体鳍、第一半导体鳍和混合鳍之间的第一隔离区域,混合鳍延伸得高于第一隔离区域的顶表面;在混合鳍的侧壁、第一半导体鳍的侧壁、和第二半导体鳍的侧壁之上的高k栅极电介质;在高k栅极电介质上的栅电极;以及在第一半导体鳍上位于栅电极的相反侧的源极/漏极区域。

技术研发人员:林政颐,李达元,徐志安

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!