半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、随着半导体制造技术的飞速发展,半导体晶体管朝着更高的元件密度,以及更高集成度的方向发展,半导体工艺节点遵循摩尔定律的发展趋势不断减小。晶体管作为最基本的半导体晶体管目前正被广泛应用,因此随着半导体晶体管的元件密度和集成度的提高,为了适应工艺节点的减小,不得不断缩短晶体管的沟道长度。

2、为了更好的适应晶体管尺寸按比例缩小的要求,半导体工艺逐渐开始从平面晶体管向具有更高功效的三维立体式的晶体管过渡,如鳍式场效应晶体管(finfet)、全包围栅极(gate-all-around,gaa)晶体管等。其中,全包围栅极晶体管包括垂直全包围栅极晶体管和水平全包围栅极晶体管。全包围栅极晶体管中,栅极从四周包围沟道所在的区域,与平面晶体管相比,全包围栅极晶体管的栅极对沟道的控制能力更强,能够更好地抑制短沟道效应。

3、随着器件尺寸的进一步缩小,如何提高全包围栅极结构器件的性能,越来越具有难度和挑战。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构的形成方法,有利于进一步提高半导体结构的性能。

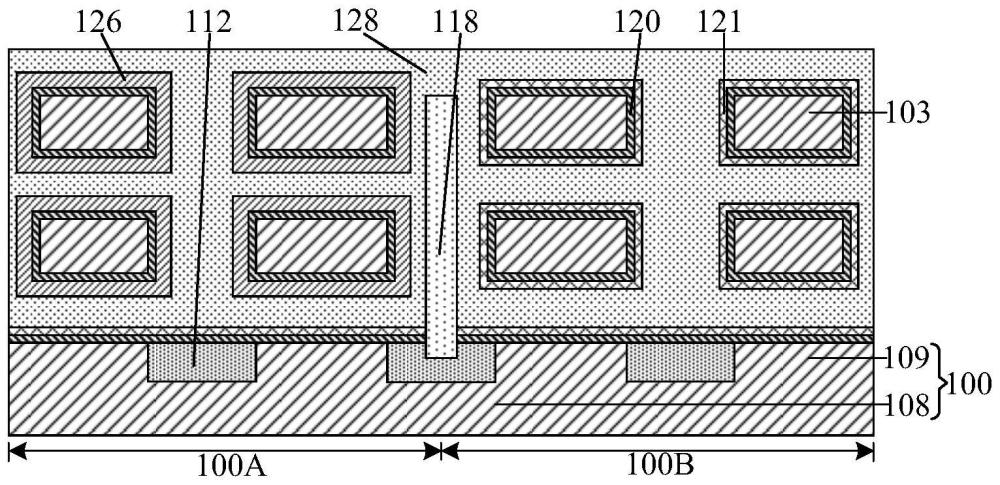

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底,基底包括第一器件区和第二器件区;沟道凸起结构,位于第一器件区和第二器件区的基底顶部;隔离层,位于沟道凸起结构侧部的基底中,且隔离层露出沟道凸起结构;阻挡层,位于第一器件区和第二器件区的交界位置处的隔离层中,阻挡层露出沟道凸起结构的侧壁,且阻挡层的顶部与沟道凸起结构的顶部相齐平,阻挡层的底部低于沟道凸起结构的底部或者与沟道凸起结构的底部相齐平;栅介质层,位于第一器件区和第二器件区的隔离层顶部,且环绕覆盖沟道凸起结构的部分顶部和部分侧壁;第一功函数层,覆盖第二器件区的栅介质层,并暴露第一器件区的栅介质层。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底,基底包括第一器件区和第二器件区,沿基底表面的法线方向,第一器件区和第二器件区的基底的顶部凸立有沟道凸起部;在沟道凸起部露出的基底中形成隔离层,隔离层覆盖沟道凸起部的侧壁,且隔离层的顶部与沟道凸起部的顶部相齐平;在第一器件区和第二器件区交界位置处的隔离层中形成阻挡层,阻挡层的顶部与沟道凸起部的顶部相齐平,且阻挡层的底部低于沟道凸起部的底部或者与沟道凸起部的底部相齐平;去除部分厚度的隔离层,露出沟道凸起部的侧壁;去除部分厚度的隔离层之后,在第一器件区和第二器件区的基底顶部形成环绕覆盖沟道凸起部部分顶部、部分侧壁的栅介质层、以及覆盖栅介质层的第一功函数层;去除第一器件区的第一功函数层。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供一种半导体结构的形成方法,先在沟道凸起部露出的基底中形成隔离层,隔离层覆盖沟道凸起部的侧壁,且隔离层的顶部与沟道凸起部的顶部相齐平,在第一器件区和第二器件区交界位置处的隔离层中形成阻挡层,阻挡层的顶部与沟道凸起部的顶部相齐平,且阻挡层的底部低于沟道凸起部的底部或者与沟道凸起部的底部相齐平,然后在去除第一器件区的第一功函数层的过程中,由于阻挡层的底部与隔离层的交界面低于沟道凸起部的底部或者与沟道凸起部的底部相齐平,使得去除第一器件区的第一功函数层所采用的刻蚀溶液向第二器件区中扩散的路径被阻挡层挡住,从而降低了第二器件区中的第一功函数层受损伤的风险,同时,在去除部分厚度的隔离层之前,先在隔离层中形成阻挡层,降低了形成阻挡层的工艺难度,也容易使阻挡层的延伸方向与沟道凸起部的延伸方向相一致,使得阻挡层能够将去除第一器件区的第一功函数层所采用的刻蚀溶液向第二器件区中扩散的路径完全挡住,进而提高了半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括:第二功函数层,覆盖所述第一器件区的栅介质层;

3.如权利要求2所述的半导体结构,其特征在于,所述第一功函数层和第二功函数层的材料不同和/或厚度不同。

4.如权利要求2或3所述的半导体结构,其特征在于,所述栅介质层的材料包括hfo2、zro2、hfsio、hfsion、hftao、hftio、hfzro、al2o3、sio2和la2o3中的一种或多种;

5.如权利要求1所述的半导体结构,其特征在于,以与所述沟道凸起结构的延伸方向相垂直的方向为横向,所述阻挡层的横向尺寸为1纳米至20纳米。

6.如权利要求1所述的半导体结构,其特征在于,所述阻挡层的底部低于所述沟道凸起结构的底部的尺寸范围小于20纳米。

7.如权利要求1所述的半导体结构,其特征在于,所述阻挡层的材料包括氮氧化硅、氮碳氧化硅和氮化硅中的一种或多种。

8.如权利要求1所述的半导体结构,其特征在于,所述沟道凸起结构为沟道叠层结构,沿所述基底表面的法线方向,所述沟道叠层结构包括一个或多个间隔设置的沟道层;所述栅介质层环绕覆盖所述沟道凸起结构的部分顶部、部分侧壁和部分底部;

9.一种半导体结构的形成方法,其特征在于,包括:

10.如权利要求9所述的半导体结构的形成方法,其特征在于,在去除所述第一器件区的所述第一功函数层之后,所述半导体结构的形成方法还包括:在所述第一器件区中形成覆盖所述栅介质层的第二功函数层;在所述第一器件区和第二器件区的所述基底顶部形成横跨所述沟道凸起部和阻挡层的栅电极层,所述栅电极层覆盖所述第一功函数层和第二功函数层。

11.如权利要求10所述的半导体结构的形成方法,其特征在于,所述第一功函数层和第二功函数层的材料不同和/或厚度不同。

12.如权利要求9所述的半导体结构的形成方法,其特征在于,形成所述隔离层的步骤包括:在所述沟道凸起部的顶部以及所述沟道凸起部露出的所述基底上形成隔离材料层;以所述沟道凸起部的顶部作为停止位置,去除高于所述沟道凸起部顶部的隔离材料层,剩余的位于所述沟道凸起部露出的所述基底上的隔离材料层作为所述隔离层。

13.如权利要求12所述的半导体结构的形成方法,其特征在于,形成所述隔离材料层的工艺包括化学气相沉积工艺。

14.如权利要求9所述的半导体结构的形成方法,其特征在于,所述隔离层的材料包括氧化硅、氮化硅和氮氧化硅中的一种或多种。

15.如权利要求9所述的半导体结构的形成方法,其特征在于,形成所述阻挡层的步骤包括:在所述第一器件区和第二器件区交界位置处的所述隔离层中形成开口;在所述沟道凸起部的顶部、所述隔离层的顶部、以及所述开口中形成阻挡材料层;以所述沟道凸起部的顶部作为停止位置,去除高于所述沟道凸起部顶部的阻挡材料层,剩余的位于所述开口中的阻挡材料层作为所述阻挡层。

16.如权利要求15所述的半导体结构的形成方法,其特征在于,形成所述开口的步骤包括:在所述隔离层和沟道凸起部的顶部形成具有掩膜开口的掩膜层,所述掩膜开口位于所述第一器件区和第二器件区交界位置处的所述隔离层的顶部;以所述掩膜层为掩膜,去除所述掩膜开口露出的所述隔离层,在所述第一器件区和第二器件区交界位置处的所述隔离层中形成开口。

17.如权利要求15所述的半导体结构的形成方法,其特征在于,形成所述开口的工艺包括干法刻蚀工艺。

18.如权利要求9所述的半导体结构的形成方法,其特征在于,去除所述第一器件区的所述第一功函数层的步骤包括:在所述基底的顶部形成覆盖所述第一功函数层和阻挡层的遮挡层;去除所述第一器件区的所述遮挡层;以所述第二器件区的剩余所述遮挡层为掩膜,去除所述第一器件区的所述第一功函数层。

19.如权利要求18所述的半导体结构的形成方法,其特征在于,去除所述第一器件区的所述遮挡层的工艺包括湿法刻蚀工艺。

20.如权利要求9所述的半导体结构的形成方法,其特征在于,所述沟道凸起部为叠层结构,所述叠层结构包括一个或多个在纵向上依次堆叠设置的沟道叠层,所述沟道叠层包括牺牲层以及位于所述牺牲层上的沟道层;

技术总结

一种半导体结构及其形成方法,方法包括:提供基底,基底包括第一器件区和第二器件区,沿基底表面的法线方向,第一器件区和第二器件区的基底的顶部凸立有沟道凸起部;在沟道凸起部露出的基底中形成隔离层,隔离层覆盖沟道凸起部的侧壁;在第一器件区和第二器件区交界位置处的隔离层中形成阻挡层,阻挡层的底部低于沟道凸起部的底部或者与沟道凸起部的底部相齐平;去除部分厚度的隔离层,露出沟道凸起部的侧壁;在第一器件区和第二器件区的基底顶部形成环绕覆盖沟道凸起部部分顶部、部分侧壁的栅介质层、以及覆盖栅介质层的第一功函数层;去除第一器件区的第一功函数层。降低第二器件区中的第一功函数层受损伤的风险,进而提高了半导体结构的性能。

技术研发人员:司进,殷立强,俞涛,崇二敏,张海洋

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!