半导体结构及其制备方法与流程

本申请涉及半导体,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、在半导体制程中,在介质层两侧的导电层(如金属层),通常通过介质层中的互连通孔进行导电连接。互连通孔内填充导电插塞。导电插塞通常采用金属材料。而金属材料容易向介质层扩散,而影响器件性能。因此,通常会先在互连通孔内壁形成扩散阻挡层,以阻止金属扩散。

2、然而,扩散阻挡层同时具有较高的电阻率,导致导电层与导电插塞之间的电阻增高,从而容易引起rc延迟问题。

技术实现思路

1、基于此,本申请实施例提供一种半导体结构及其制备方法,以降低导电层与导电插塞之间的电阻。

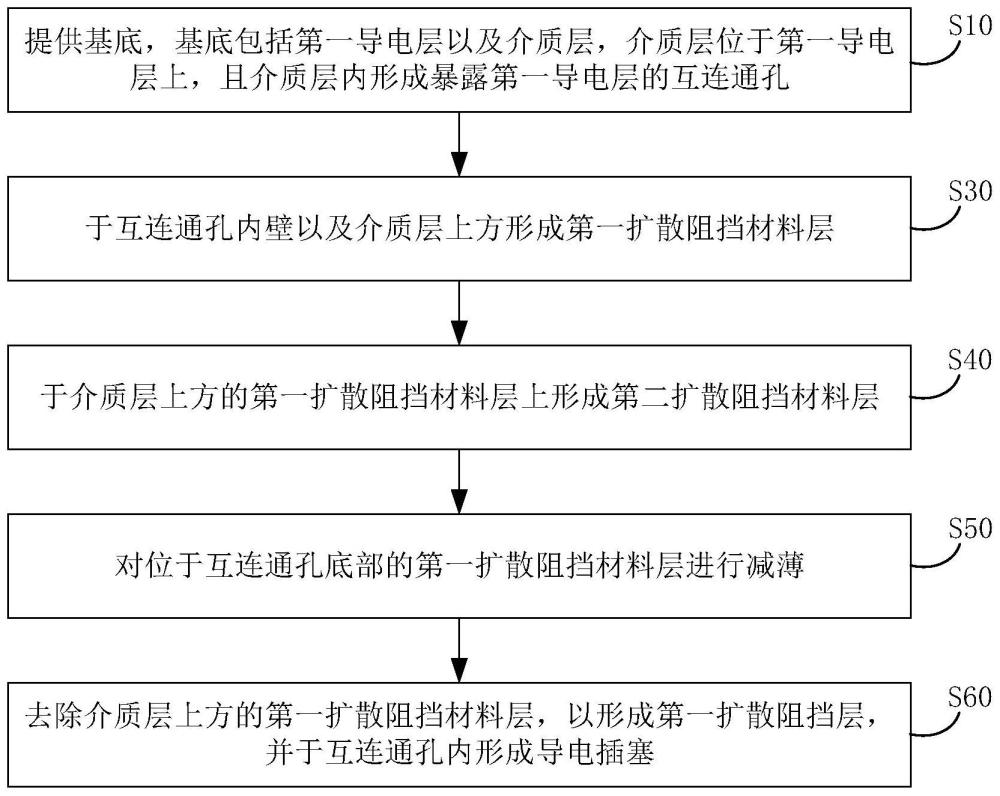

2、一种半导体结构的制备方法,包括:

3、提供基底,所述基底包括第一导电层以及介质层,所述介质层位于所述第一导电层上,且所述介质层内形成暴露所述第一导电层的互连通孔;

4、于所述互连通孔内壁以及所述介质层上方形成第一扩散阻挡材料层;

5、于所述介质层上方的所述第一扩散阻挡材料层上形成第二扩散阻挡材料层;

6、对位于所述互连通孔底部的第一扩散阻挡材料层进行减薄;

7、去除所述介质层上方的第一扩散阻挡材料层,以形成第一扩散阻挡层,并于所述互连通孔内形成导电插塞。

8、在其中一个实施例中,所述于所述介质层上方的所述第一扩散阻挡材料层上形成第二扩散阻挡材料层,包括:

9、于所述介质层上方的所述第一扩散阻挡材料层表面、所述互连通孔侧壁顶部的第一扩散阻挡材料层表面形成所述第二扩散阻挡材料层。

10、在其中一个实施例中,所述第二扩散阻挡材料层通过物理气相沉积方式形成。

11、在其中一个实施例中,所述物理气相沉积方式采用高沉积速率沉积方式,所述沉积速率不小于5nm/s且不大于10nm/s。

12、在其中一个实施例中,进行物理气相沉积时,沉积温度为180℃-220℃,沉积功率为1300w-1700w,氮气流量为55sccm-65sccm,氩气流量为9sccm-11sccm。

13、在其中一个实施例中,所述第一扩散阻挡材料层通过原子层沉积方式形成,且形成的第一扩散阻挡材料层的厚度为10nm-12nm;和/或

14、所述物理气相沉积方式形成的所述第二扩散阻挡材料层的厚度为10nm-15nm。

15、在其中一个实施例中,所述第二扩散阻挡材料层为wnx,其中,x值大于0.9。

16、在其中一个实施例中,所述第二扩散阻挡材料层的材料与所述第一扩散阻挡材料层的材料相同。

17、在其中一个实施例中,所述互连通孔的侧壁与水平方向的角度为86°至90°。

18、在其中一个实施例中,减薄后,所述第一扩散阻挡材料层的厚度为3nm-5nm。

19、在其中一个实施例中,所述对位于所述互连通孔底部的第一扩散阻挡材料层进行减薄,包括:

20、对位于所述互连通孔底部的第一扩散阻挡材料层进行物理轰击处理。

21、在其中一个实施例中,所述于所述互连通孔内壁以及所述介质层上方形成第一扩散阻挡材料层之前,还包括:

22、对所述互连通孔底部的第一导电层进行还原处理。

23、在其中一个实施例中,所述还原处理与所述物理轰击处理在同一工艺腔室内进行。

24、在其中一个实施例中,

25、进行还原处理时,通入氢气以及氩气,氢气流量为18-22sccm,氩气流量为90-110sccm,且设置偏置功率为180w-200w,解离功率为1800w-2200w。

26、在其中一个实施例中,

27、进行行物理轰击处理时,通入氩气,氩气流量为90-110sccm,且设置偏置功率为600w-1000w,解离功率为1800w-2200w。

28、在其中一个实施例中,所述对位于所述互连通孔底部的第一扩散阻挡材料层进行减薄,包括:对位于所述互连通孔底部的第一扩散阻挡材料层进行干法刻蚀。

29、在其中一个实施例中,所述去除所述介质层上方的第一扩散阻挡材料层,以形成第一扩散阻挡层,并于所述互连通孔内形成导电插塞,包括:

30、于所述互连通孔内以及所述第二扩散阻挡材料层上方形成导电插塞材料层;

31、进行化学机械研磨处理,以去除所述第二扩散阻挡材料层上方的导电插塞材料层以及第一扩散阻挡材料层,以形成所述导电插塞以及所述第一扩散阻挡层。

32、在其中一个实施例中,所述进行化学机械研磨处理,以去除所述第二扩散阻挡材料层上方的导电插塞材料层以及第一扩散阻挡材料层之后,还包括:

33、对所述介质层以及所述互连通孔内的导电插塞以及第一扩散阻挡层继续进行化学机械研磨处理。

34、在其中一个实施例中,所述去除所述介质层上方的第一扩散阻挡材料层,以形成第一扩散阻挡层,并于所述互连通孔内形成导电插塞之后,还包括:

35、于所述介质层上形成第二导电层,所述第二导电层覆盖所述导电插塞。

36、一种半导体结构,根据上述任一项所述的方法制备形成,所述半导体结构包括:

37、基底,包括第一导电层以及介质层,所述介质层位于所述第一导电层上,且所述介质层内形成互连通孔;

38、第一扩散阻挡层,位于所述互连通孔内壁,且位于所述互连通孔底部的第一扩散阻挡层的厚度小于位于所述互连通孔侧壁的第一扩散阻挡层的厚度;

39、导电插塞,位于所述互连通孔内的所述第一扩散阻挡层表面,且填充所述互连通孔。

40、在其中一个实施例中,所述互连通孔底部的第一扩散阻挡层的厚度为3nm-5nm,位于所述互连通孔侧壁的第一扩散阻挡层的厚度为10nm-12nm。

41、在其中一个实施例中,所述半导体结构还包括:

42、第二导电层,位于所述介质层上,且覆盖所述导电插塞。

43、上述半导体结构及其制备方法,可以通过互连通孔侧壁的扩散阻挡层有效防止导电插塞中的金属扩散至介质层。同时,通过对互连通孔底部的第一扩散阻挡层进行减薄,从而使得导电插塞与第一导电层之间的电阻可以被有效降低。

44、同时,半导体结构的制备方法中,在形成第一扩散阻挡材料层之后,还在于介质层上方的第一扩散阻挡材料层上形成第二扩散阻挡材料层。在对互连通孔底部的第一扩散阻挡材料层进行减薄的时候,第二扩散阻挡材料层可以防止介质层上方的第一扩散阻挡材料层被明显减薄或者去除掉。此时,一方面在减薄过程中可以对介质层进行保护,防止减薄过程损伤介质层。另一方面,在形成导电插塞的过程中,也可以有效防止金属材料向介质层扩散,从而保证器件性能。同时,第二扩散阻挡材料层与第一扩散阻挡材料层均为具有阻挡金属扩散功能的膜层,从而使得第二扩散阻挡材料层的形成,不会对第一扩散阻挡材料层造成污染。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述于所述介质层上方的所述第一扩散阻挡材料层上形成第二扩散阻挡材料层,包括:

3.根据权利要求1或2所述的半导体结构的制备方法,其特征在于,所述第二扩散阻挡材料层通过物理气相沉积方式形成。

4.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述物理气相沉积方式采用高沉积速率沉积方式,所述沉积速率不小于5nm/s且不大于10nm/s。

5.根据权利要求3所述的半导体结构的制备方法,其特征在于,进行物理气相沉积时,沉积温度为180℃-220℃,沉积功率为1300w-1700w,氮气流量为55sccm-65sccm,氩气流量为9sccm-11sccm。

6.根据权利要求3所述的半导体结构的制备方法,其特征在于,

7.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述第二扩散阻挡材料层为wnx,其中,x值大于0.9。

8.根据权利要求1或7所述的半导体结构的制备方法,其特征在于,所述第二扩散阻挡材料层的材料与所述第一扩散阻挡材料层的材料相同。

9.根据权利要求1所述的半导体结构的制备方法,其特征在于,

10.根据权利要求1或9所述的半导体结构的制备方法,其特征在于,所述对位于所述互连通孔底部的第一扩散阻挡材料层进行减薄,包括:

11.根据权利要求10所述的半导体结构的制备方法,其特征在于,所述于所述互连通孔内壁以及所述介质层上方形成第一扩散阻挡材料层之前,还包括:

12.根据权利要求11所述的半导体结构的制备方法,其特征在于,所述还原处理与所述物理轰击处理在同一工艺腔室内进行。

13.根据权利要求12所述的半导体结构的制备方法,其特征在于,

14.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述去除所述介质层上方的第一扩散阻挡材料层,以形成第一扩散阻挡层,并于所述互连通孔内形成导电插塞,包括:

15.根据权利要求14所述的半导体结构的制备方法,其特征在于,所述进行化学机械研磨处理,以去除所述第二扩散阻挡材料层上方的导电插塞材料层以及第一扩散阻挡材料层之后,还包括:

16.根据权利要求14或15所述的半导体结构的制备方法,其特征在于,所述去除所述介质层上方的第一扩散阻挡材料层,以形成第一扩散阻挡层,并于所述互连通孔内形成导电插塞之后,还包括:

17.一种半导体结构,其特征在于,根据权利要求1-16任一项所述的方法制备形成,所述半导体结构包括:

18.根据权利要求17所述的半导体结构,其特征在于,所述互连通孔底部的第一扩散阻挡层的厚度为3nm-5nm,位于所述互连通孔侧壁的第一扩散阻挡层的厚度为10nm-12nm。

19.根据权利要求17或18所述的半导体结构,其特征在于,所述半导体结构还包括:

技术总结

本申请涉及一种半导体结构及其制备方法。其中,半导体结构的制备方法包括:提供基底,基底包括第一导电层以及介质层,介质层位于第一导电层上,且介质层内形成暴露第一导电层的互连通孔;于互连通孔内壁以及介质层上方形成第一扩散阻挡材料层;于介质层上方的第一扩散阻挡材料层上形成第二扩散阻挡材料层;对位于互连通孔底部的第一扩散阻挡材料层进行减薄;去除介质层上方的第一扩散阻挡材料层,以形成第一扩散阻挡层,并于互连通孔内形成导电插塞。本申请实施例可以有效降低导电层与导电插塞之间的电阻。

技术研发人员:张杰,冯毅伟,费凡,闫冬

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!