半导体结构及制备方法与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构及制备方法。

背景技术:

1、随着cmos技术的发展,传统的二氧化硅栅介质和多晶硅栅极(polycrystallinesilicon)晶体管已经达到物理极限,比如说由于量子隧穿效应导致的漏电流过大的问题和多晶硅栅极的耗尽问题等严重影响了半导体器件的性能。从45nm技术节点开始,二氧化硅栅介质层的厚度降低到2nm以下,为了改善栅极泄漏电流,半导体业界利用高k介质材料hfo2和hfsion取代二氧化硅作为栅介质。利用高k介质材料代替常规二氧化硅栅介质和金属栅代替多晶硅栅的工艺称为hkmg工艺技术,其中,hk是high k的缩写,mg是metal gate的缩写,也就是金属栅极。

2、高介电常数金属栅mos晶体管的栅极结构采用hkmg,hkmg包括有高介电常数层(hk)和金属栅(mg),其中金属栅包括有金属功函数层和金属导电材料层,其中金属功函数层用于调节器件的阈值电压,当金属功函数层的功函数不同时,器件的平带电压也就不同,最后使得器件的阈值电压不同。一般在形成外围区的栅极结构时,通常为简化工艺会同时形成nmos器件的hkmg以及pmos器件的hkgm,由于pmos器件的初始栅极结构的膜层结构比nmos器件的初始栅极结构的膜层结构较多,从而在刻蚀工艺中出现一系列技术问题,例如,足部缺陷问题(footing)或者缩颈现象。

技术实现思路

1、本公开实施例提供一种半导体结构及制备方法,至少有利于改善同时形成nmos器件的hkmg以及pmos器件的hkgm时,避免pmos器件的hkmg的足部缺陷问题。

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构的制备方法,包括:提供基底,基底包括第一型区以及第二型区;第一型区的基底上具有第一绝缘层以及初始第一栅结构,第二型区的基底上具有第二绝缘层与初始第二栅结构;多次同时刻蚀初始第一栅结构以及初始第二栅结构形成第一栅结构以及第二栅结构,第一栅结构的底部在基底的正投影位于第一栅结构的顶部在基底的正投影内;其中,第一次刻蚀工艺后,位于第一型区的第一绝缘层的顶面不暴露外部。

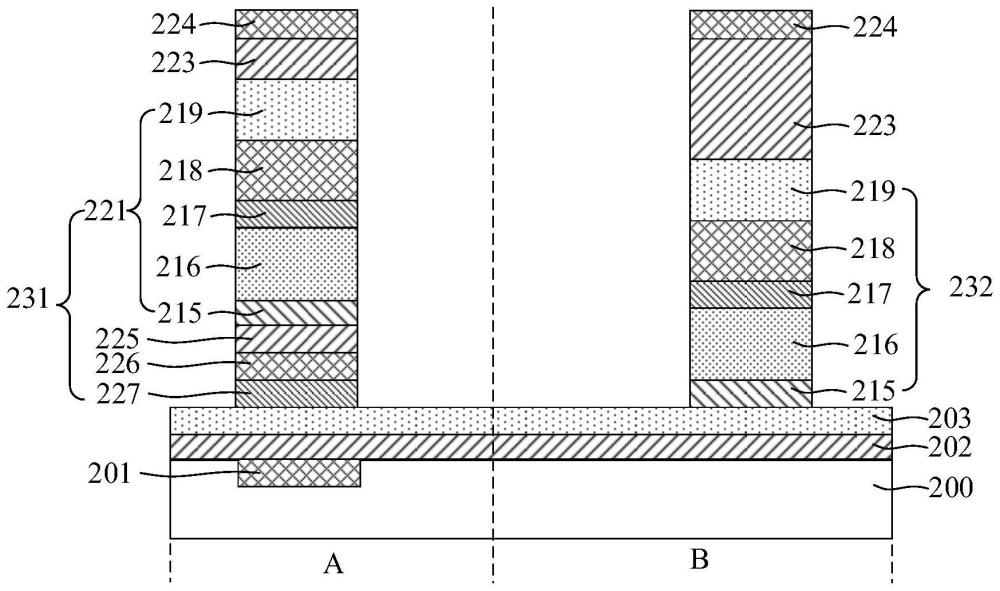

3、在一些实施例中,初始第一栅结构包括层叠的第一功函数膜、第二功函数膜以及导电膜,初始第二栅结构包括第二功函数膜以及导电膜;多次同时刻蚀初始第一栅结构以及初始第二栅结构的工艺步骤包括:刻蚀位于第一型区的基底上的导电膜以及第二功函数膜形成间隔排布的第一导电层的同时,刻蚀位于第二型区的基底上的导电膜以及第二功函数膜形成间隔排布的第二导电层;采用第一湿法刻蚀工艺刻蚀第一功函数膜形成第一功函数层,第一功函数层在基底的正投影位于第一导电层在基底的正投影内,第一功函数层以及第一导电层共同构成第一栅结构,第二导电层作为第二栅结构。

4、在一些实施例中,采用干法刻蚀工艺形成第一导电层以及第二导电层;第一湿法刻蚀工艺的刻蚀液为盐酸溶液。

5、在一些实施例中,盐酸溶液的浓度为200:1。

6、在一些实施例中,第一湿法刻蚀工艺的刻蚀时间为50s-70s。

7、在一些实施例中,在形成第二功函数膜之前还包括:在第一功函数膜形成阻挡膜;刻蚀第一功函数膜之前还包括:刻蚀阻挡膜形成阻挡层,阻挡层在基底的正投影位于第一导电层在基底的正投影内,阻挡层、第一功函数层以及第一导电层共同构成第一栅结构。

8、在一些实施例中,采用第二湿法刻蚀工艺刻蚀阻挡膜,第二湿法刻蚀工艺的刻蚀液为硫酸与过氧化氢混合溶液。

9、在一些实施例中,硫酸与过氧化氢的质量比为33:1。

10、在一些实施例中,第二湿法刻蚀工艺的刻蚀时间为5s-20s。

11、在一些实施例中,刻蚀阻挡膜与刻蚀第一功函数膜交替进行,直至第一功函数层在基底的正投影以及阻挡层在基底的正投影均位于第一导电层在基底的正投影内。

12、在一些实施例中,形成第一绝缘层以及第二绝缘层包括:在基底表面形成介质膜,位于第一型区的介质膜作为第一绝缘层,位于第二型区的介质膜作为第二绝缘层;刻蚀初始第一栅结构之后还包括:刻蚀第一绝缘层形成第一栅介质层的同时,刻蚀第二绝缘层形成第二栅介质层。

13、在一些实施例中,第一功函数层的侧面与第一导电层的侧面之间的间距小于等于1.5nm。

14、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构,包括:基底,基底包括第一型区以及第二型区;第一绝缘层以及第二绝缘层,第一绝缘层位于第一型区的基底上,第二绝缘层位于第二型区的基底上;第一栅结构,第一栅结构位于第一型区的第一绝缘层上;第二栅结构,第二栅结构位于第二型区的第二绝缘层上。

15、在一些实施例中,第一栅结构包括层叠设置的第一功函数层以及第一导电层,第一功函数层在基底的正投影位于第一导电层在基底的正投影内;第二栅结构包括第二导电层。

16、在一些实施例中,第一栅结构还包括:阻挡层,阻挡层位于第一功函数层与第一导电层之间。

17、本公开实施例提供的技术方案至少具有以下优点:

18、本公开实施例提供的技术方案中,通过多次同时刻蚀初始第一栅结构以及初始第二栅结构的过程中,在第一次刻蚀后第一绝缘层的顶面不暴露,第一栅结构的底部在基底的正投影位于第一栅结构的顶部在基底的正投影内,即第一栅结构的底部不存在足部缺陷问题,后续刻蚀第一绝缘层以及第二绝缘层形成高介电栅介质时,第一栅结构的底部的第一栅介质层不会存在足部缺陷问题。此外,同时形成第一栅结构以及第二栅结构,可以减少分别制备第一栅结构以及第二栅结构所需的光罩数量,节约工艺成本,同时还能生产速率,从而能提高产品的竞争性。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述初始第一栅结构包括层叠的第一功函数膜、第二功函数膜以及导电膜,所述初始第二栅结构包括所述第二功函数膜以及所述导电膜;

3.根据权利要求2所述的半导体结构的制备方法,其特征在于,采用干法刻蚀工艺形成所述第一导电层以及第二导电层;所述第一湿法刻蚀工艺的刻蚀液为盐酸溶液。

4.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述盐酸溶液的浓度为200:1。

5.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述第一湿法刻蚀工艺的刻蚀时间为50s-70s。

6.根据权利要求2所述的半导体结构的制备方法,其特征在于,在形成第二功函数膜之前还包括:在所述第一功函数膜形成阻挡膜;刻蚀所述第一功函数膜之前还包括:刻蚀所述阻挡膜形成阻挡层,所述阻挡层在所述基底的正投影位于所述第一导电层在所述基底的正投影内,所述阻挡层、所述第一功函数层以及第一导电层共同构成所述第一栅结构。

7.根据权利要求6所述的半导体结构的制备方法,其特征在于,采用第二湿法刻蚀工艺刻蚀所述阻挡膜,所述第二湿法刻蚀工艺的刻蚀液为硫酸与过氧化氢混合溶液。

8.根据权利要求7所述的半导体结构的制备方法,其特征在于,所述硫酸与过氧化氢的质量比为33:1。

9.根据权利要求7所述的半导体结构的制备方法,其特征在于,所述第二湿法刻蚀工艺的刻蚀时间为5s-20s。

10.根据权利要求6所述的半导体结构的制备方法,其特征在于,刻蚀所述阻挡膜与刻蚀所述第一功函数膜交替进行,直至所述第一功函数层在所述基底的正投影以及所述阻挡层在所述基底的正投影均位于所述第一导电层在所述基底的正投影内。

11.根据权利要求2或6所述的半导体结构的制备方法,其特征在于,形成所述第一绝缘层以及所述第二绝缘层包括:在所述基底表面形成介质膜,位于所述第一型区的所述介质膜作为所述第一绝缘层,位于所述第二型区的所述介质膜作为所述第二绝缘层;刻蚀所述初始第一栅结构之后还包括:刻蚀所述第一绝缘层形成第一栅介质层的同时,刻蚀所述第二绝缘层形成所述第二栅介质层。

12.根据权利要求2所述的半导体结构的制备方法,其特征在于,第一功函数层的侧面与所述第一导电层的侧面之间的间距小于等于1.5nm。

13.一种如权利要求1~12任一项所述的半导体结构的制备方法制备的半导体结构,其特征在于,包括:

14.根据权利要求13所述的半导体结构,其特征在于,所述第一栅结构包括层叠设置的第一功函数层以及第一导电层,所述第一功函数层在所述基底的正投影位于所述第一导电层在所述基底的正投影内;所述第二栅结构包括第二导电层。

15.根据权利要求14所述的半导体结构,其特征在于,所述第一栅结构还包括:阻挡层,所述阻挡层位于所述第一功函数层与所述第一导电层之间。

技术总结

本公开实施例涉及半导体领域,提供一种半导体结构及制备方法,制备方法包括:提供基底,基底包括第一型区以及第二型区;第一型区的基底上具有第一绝缘层以及初始第一栅结构,第二型区的基底上具有第二绝缘层与初始第二栅结构;多次同时刻蚀初始第一栅结构以及初始第二栅结构形成第一栅结构以及第二栅结构,所述第一栅结构的底部在所述基底的正投影位于所述第一栅结构的顶部在所述基底的正投影内;其中,第一次刻蚀工艺后,位于所述第一型区的第一绝缘层的顶面不暴露外部。本公开实施例提供的半导体结构及制备方法,至少有利于改善同时形成NMOS器件的HKMG以及PMOS器件的HKGM时,避免PMOS器件的HKMG的足部缺陷问题。

技术研发人员:刘洋

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!