半导体装置的制造方法及半导体装置与流程

本申请属于半导体,尤其涉及一种半导体装置的制造方法及半导体装置。

背景技术:

1、在现有的高压功率半导体装置中,终端区(termination area)围绕主动区并且在足够高的击穿电压(breakdown voltage)下运作。终端区的空乏延伸宽度(depletionextension width)会影响终端区的电场分布。为了达到均匀的电场分布,现有的终端区需要复杂的制造制程以形成复数个堆栈层,并且必须占用一大部分的芯片面积,而且,还需要额外的离子植入制程,其大幅增加了制造成本。

2、另外,随着高压功率半导体装置的技术的发展,击穿电压的需求也随着每个芯片所整合的半导体组件越来越多而越来越高。表面电场(surface electric field)的延伸能力(capability of extension)将直接决定高压功率半导体装置的击穿电压性能,而现有的终端区的表面电场较窄,难以达到预期的击穿电压性能。

技术实现思路

1、有鉴于此,本申请实施例提供一种半导体装置的制造方法及半导体装置,能够以低成本延伸表面电场并且提高击穿电压。

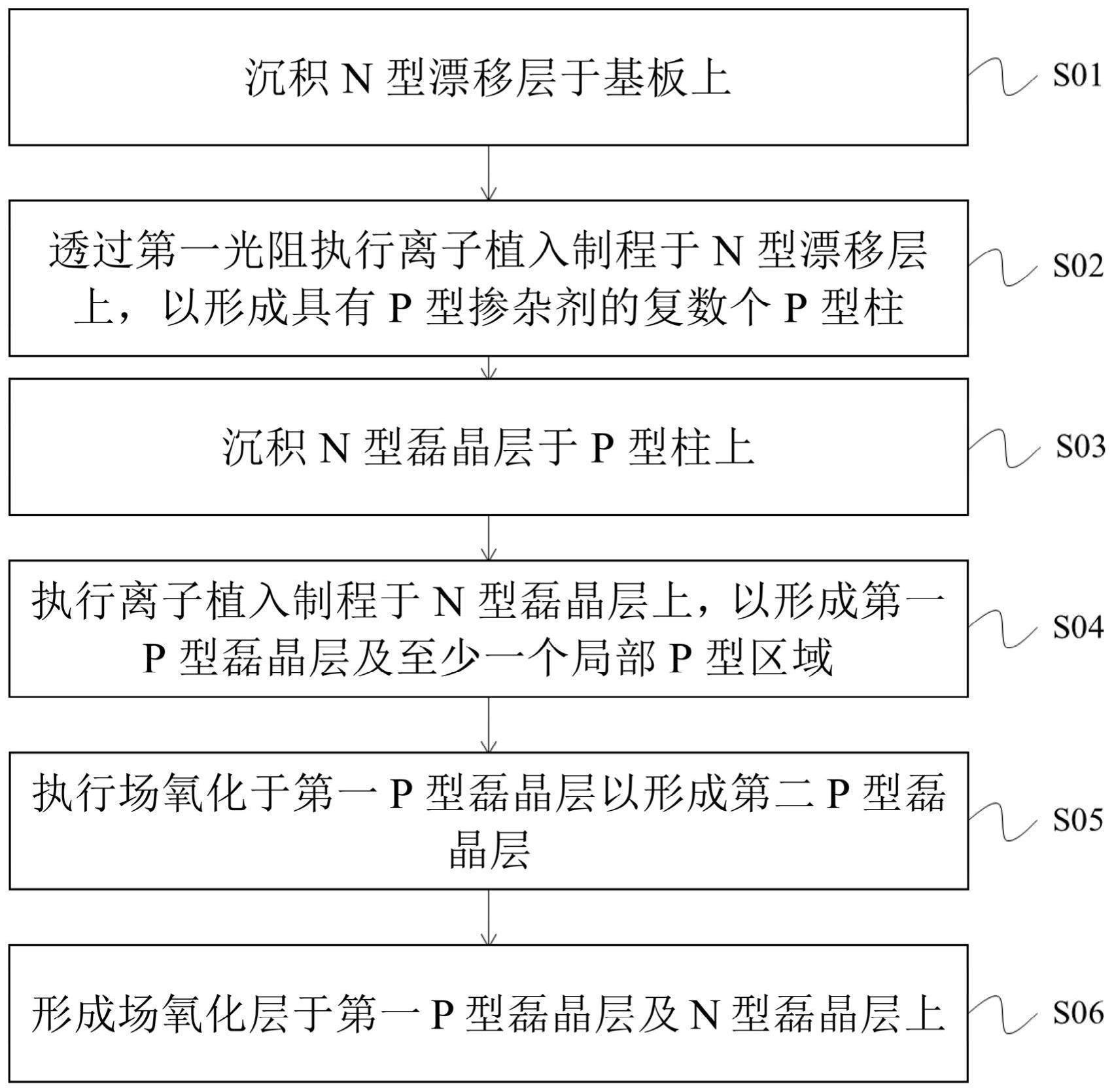

2、第一方面,本申请实施例提供一种半导体装置的制造方法。包括以下步骤:

3、沉积n型漂移层于基板上;

4、执行离子植入制程于n型漂移层上以形成复数个p型柱;

5、沉积n型磊晶层于复数个p型柱上;

6、执行离子植入制程于n型磊晶层上以形成第一p型磊晶层及至少一个局部p型区域;

7、执行场氧化于第一p型磊晶层以形成第二p型磊晶层;以及,

8、形成场氧化层于第一p型磊晶层及n型磊晶层上;其中,局部p型区域穿过n型磊晶层到达场氧化层。

9、优选地,执行离子植入制程于n型漂移层上,以形成复数个p型柱的步骤包括以下步骤:

10、执行离子植入制程于n型漂移层上以形成复数个p型区域。

11、优选地,执行离子植入制程于n型漂移层上,以形成复数个p型柱的步骤还包括以下步骤:

12、(a)沉积n型层于p型区域上;

13、(b)执行离子植入制程于n型层上以形成p型区域;

14、(c)重复步骤(a)至步骤(b)至少一次;

15、(d)执行场氧化于p型区域以形成p型柱。

16、优选地,局部p型区域沿复数个p型柱中的一个的纵向形成于第二p型磊晶层上。

17、优选地,各局部p型区域彼此隔开。

18、优选地,局部p型区域数量与p型柱的数量比例为1:3至1:100。

19、优选地,半导体装置的表面电场的峰值等于或小于2.1×105v/cm。

20、优选地,半导体装置的击穿电压大约等于或大于装置耐受击穿电压额定值(sustained breakdown voltage rating)的1.05倍。

21、优选地,半导体装置的制造方法还包括以下步骤:

22、执行多晶硅沉积于第一p型磊晶层上以形成多晶硅层,其中多晶硅层邻接于场氧化物;

23、设置源电极于多晶硅层的一侧;

24、设置闸电极,其设置于多晶硅层的另一侧;以及,

25、设置等电位环电极于场氧化物上。

26、第二方面,本申请实施例还提供一种半导体装置。半导体装置包括:

27、n型漂移层;

28、复数个p型柱,其分别设置于n型漂移层上;

29、第二p型磊晶层,其设置于p型柱上;

30、n型磊晶层,其设置于第二p型磊晶层上;

31、第一p型磊晶层,其设置并邻接于n型磊晶层;

32、场氧化层,其设置于第一p型磊晶层及n型磊晶层上;以及,

33、至少一个局部p型区域,其设置于p型柱上并且穿过n型磊晶层到达场氧化层。

34、优选地,局部p型区域配置为延伸半导体装置的表面电场的空乏边界。

35、优选地,局部p型区域沿复数个p型柱中的一个的纵向设置于第二p型磊晶层上。

36、优选地,各局部p型区域彼此隔开。

37、优选地,局部p型区域数量与p型柱数量的比例为1:3至1:100。

38、优选地,半导体装置的表面电场的峰值等于或小于2.1×105v/cm。

39、优选地,半导体装置的击穿电压等于或大于装置耐受击穿电压额定值的1.05倍。

40、优选地,半导体装置还包括基板,基板包括主动区以及连接主动区的终端区,其中n型漂移层设置于终端区上。

41、优选地,半导体装置还包括:

42、多晶硅层,其设置于第一p型磊晶层上,其中多晶硅层邻接于场氧化物;

43、源电极,其设置于多晶硅层的一侧;

44、闸电极,其设置于多晶硅层的另一侧;以及

45、等电位环电极,其设置于场氧化物上。

46、本申请实施例提供的半导体装置的制造方法及半导体装置具有以下优点:

47、本申请实施例的半导体装置的制造方法及半导体装置提供了一个终端区,其中设置有局部p型区域,并且使得n型磊晶层传递至场氧化层。通过局部p型区域,本申请的半导体装置能够扩展半导体装置的表面电场的空乏边界并降低表面电场的峰值,从而实现均匀的电场分布并且提高击穿电压。并且,逆向阻隔电压的能力也增加了。由于较低的表面电场,对高温反向偏压可靠性测试更加稳健。由于电位分布与电场有关,因此本申请的半导体装置的电位分布宽度增加。较低的表面电场可以获得更大的技术制程的抗扰力,从而提高本申请的半导装置的稳定性。局部p型区域可以通过各种模式很好地控制以实现所期望的性能。此外,本申请的局部p型区域可以通过使用与形成主动区域的制程中相同的光阻(photo resistor)来形成,而无需使用任何额外的光阻,从而节省了制造成本。

技术特征:

1.一种半导体装置的制造方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的半导体装置的制造方法,其特征在于,执行离子植入制程于所述n型漂移层上,以形成复数个所述p型柱的步骤包括以下步骤:

3.根据权利要求2所述的半导体装置的制造方法,执行离子植入制程于所述n型漂移层上,以形成所述复数个p型区域的步骤还包括以下步骤:

4.根据权利要求1所述的半导体装置的制造方法,其特征在于,所述局部p型区域具有复数个,且沿复数个所述p型柱中的一个的纵向形成于所述第二p型磊晶层上。

5.根据权利要求4所述的半导体装置的制造方法,其特征在于,复数个所述局部p型区域彼此隔开。

6.根据权利要求1所述的半导体装置的制造方法,其特征在于,其中所述局部p型区域的数量与所述p型柱的数量的比例为1:3至1:100。

7.根据权利要求1所述的半导体装置的制造方法,其特征在于,所述半导体装置的表面电场的峰值等于或小于2.1×105v/cm。

8.根据权利要求1所述的半导体装置的制造方法,其特征在于,所述半导体装置的击穿电压等于或大于装置耐受击穿电压额定值的1.05倍。

9.根据权利要求1所述的半导体装置的制造方法,其特征在于,还包括以下步骤:

10.一种半导体装置,其特征在于,包括:

11.根据权利要求10所述的半导体装置,其特征在于,至少一个所述局部p型区域配置为延伸所述半导体装置的表面电场的空乏边界。

12.根据权利要求10所述的半导体装置,其特征在于,至少一个所述局部p型区域沿复数个所述p型柱中的一个的纵向而设置于所述第二p型磊晶层上。

13.根据权利要求10所述的半导体装置,其特征在于,所述局部p型区域具有复数个,且彼此隔开。

14.根据权利要求10所述的半导体装置,其特征在于,所述局部p型区域的数量与所述p型柱的数量的比例为1:3至1:100。

15.根据权利要求10所述的半导体装置,其特征在于,所述半导体装置的表面电场的峰值等于或小于2.1×105v/cm。

16.根据权利要求10所述的半导体装置,其特征在于,所述半导体装置的击穿电压等于或大于装置耐受击穿电压额定值的1.05倍。

17.根据权利要求10所述的半导体装置,其特征在于,还包括基板,所述基板包括主动区以及连接所述主动区的终端区,其中所述n型漂移层设置于所述终端区上。

18.根据权利要求10所述的半导体装置,其特征在于,还包括:

技术总结

本申请属于半导体技术领域,提供一种半导体装置的制造方法及半导体装置,半导体装置的制造方法包括以下步骤:沉积N型漂移层于基板上;执行离子植入制程于N型漂移层上以形成复数个P型柱;沉积N型磊晶层于复数个P型柱上;执行离子植入制程于N型磊晶层上,以形成第一P型磊晶层及至少一个局部P型区域;执行场氧化于第一P型磊晶层,以形成第二P型磊晶层;以及形成场氧化层于第一P型磊晶层及N型磊晶层上;至少一个局部P型区域穿过N型磊晶层到达场氧化层。该半导体装置的制造方法能够扩展半导体装置的表面电场的空乏边界并降低表面电场的峰值,从而实现均匀的电场分布并且提高击穿电压,无需使用任何额外的光阻,节省了制造成本。

技术研发人员:林哲铭,朴钟浩,全珖延

受保护的技术使用者:强茂股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!