半导体结构及其形成方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、横向双扩散mosfet(lateral double-diffused mosfet,ldmos)作为功率开关器件广泛应用于高压集成电路中,例如ac-dc led驱动器、开关电源、电机驱动器等。就高功率ldmos而言,同时实现高击穿电压(breakdown voltage,bv)和低导通电阻(on-resistance,ron,sp)是理想目标。然而,导通电阻随着击穿电压的增加而快速增加,这也被称为″硅极限″关系(ron,sp∝bv2.5),导致高功耗。目前有多种技术来优化这两个重要参数之间的关系,如减小的表面场(reduced surface field,resurf)、超级结和横向掺杂的变化(variation oflateral doping,vld)。

2、对于中低压ldmos,沟槽接触结构(trench ct)是目前业界的主流技术。这是因为沟槽ct技术不会破坏晶片表面上的载流子路径,所以它可以实现较低的导通电阻。然而,由于侧墙(spacer)处的电介质过厚,表面电场存在明显的下降,这意味着高电压不能有效地在漂移区下降。因此,基于沟槽ct技术的ldmos的击穿电压与导通电阻的关系难以进一步优化。

3、因此,有必要提供一种更有效、更可靠的技术方案,以进一步优化基于沟槽ct技术的ldmos的击穿电压与导通电阻的关系。

技术实现思路

1、本申请提供一种半导体结构及其形成方法,可以降低基于沟槽ct技术的ldmos器件的导通电阻,提高热载流子退化性能。

2、本申请的一个方面提供一种半导体结构的形成方法,包括:提供半导体衬底,所述半导体衬底表面形成有栅极层;在所述栅极层侧壁以及栅极层两侧的半导体衬底部分表面形成氧化层;在所述氧化层表面形成导电层,所述氧化层和导电层共同构成所述栅极层的侧墙;在所述栅极层部分表面、所述栅极层一侧的侧墙表面以及所述侧墙一侧的半导体衬底表面形成阻挡层;在所述阻挡层中形成暴露所述导电层的第一开口;在所述半导体衬底上形成完全覆盖所述半导体衬底的层间介质层;在所述层间介质层中形成贯穿所述层间介质层且连接所述导电层和阻挡层的接触结构。

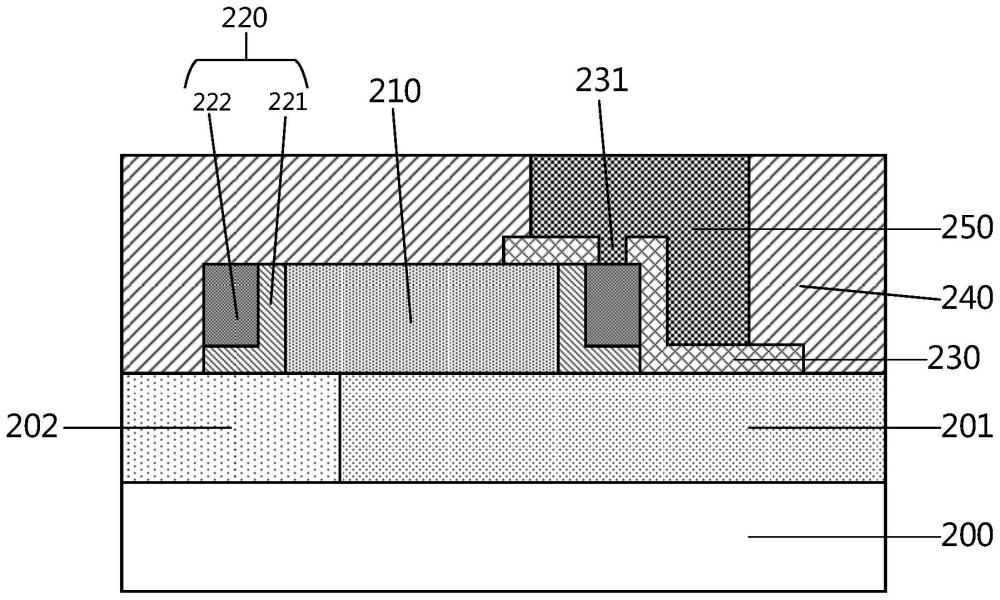

3、在本申请的一些实施例中,所述半导体衬底中形成有漂移区和阱区,其中,所述漂移区位于所述栅极层与阻挡层连接的一侧的半导体衬底中并延伸至所述栅极层下方,所述阱区位于所述栅极层另一侧的半导体衬底中并延伸至所述栅极层下方与所述漂移区邻接。

4、在本申请的一些实施例中,形成所述氧化层和导电层的方法包括:在所述栅极层表面和侧壁以及所述半导体衬底表面依次形成氧化材料层和导电材料层;刻蚀所述氧化材料层和导电材料层形成所述氧化层和导电层。

5、在本申请的一些实施例中,所述层间介质层的材料与所述阻挡层的材料不同。

6、在本申请的一些实施例中,所述层间介质层的材料为氧化硅,所述阻挡层的材料为氮化硅。

7、在本申请的一些实施例中,形成所述接触结构的方法包括:在所述层间介质层表面形成图案化的光阻层,所述图案化的光阻层定义所述接触结构的位置;以所述图案化的光阻层为掩膜刻蚀所述层间介质层至暴露所述阻挡层以及暴露所述第一开口底部的导电层形成第二开口;在所述第二开口中形成所述接触结构。

8、在本申请的一些实施例中,所述导电层的材料为多晶硅。

9、本申请的另一个方面提供一种半导体结构,包括:半导体衬底,所述半导体衬底表面形成有栅极层;氧化层,位于所述栅极层侧壁以及栅极层两侧的半导体衬底部分表面;导电层,位于所述氧化层表面,所述氧化层和导电层共同构成所述栅极层的侧墙;阻挡层,位于所述栅极层部分表面、所述栅极层一侧的侧墙表面以及所述侧墙一侧的半导体衬底表面;层间介质层,位于所述半导体衬底上完全覆盖所述半导体衬底;接触结构,贯穿所述层间介质层以及所述导电层顶部的部分阻挡层且连接所述导电层和阻挡层。

10、在本申请的一些实施例中,所述半导体衬底中形成有漂移区和阱区,其中,所述漂移区位于所述栅极层与阻挡层连接的一侧的半导体衬底中并延伸至所述栅极层下方,所述阱区位于所述栅极层另一侧的半导体衬底中并延伸至所述栅极层下方与所述漂移区邻接。

11、在本申请的一些实施例中,所述层间介质层的材料与所述阻挡层的材料不同。

12、在本申请的一些实施例中,所述层间介质层的材料为氧化硅,所述阻挡层的材料为氮化硅。

13、在本申请的一些实施例中,所述导电层的材料为多晶硅。

14、本申请提供一种半导体结构及其形成方法,将栅极层的侧墙从传统的ono三层结构替换成氧化硅和多晶硅双层结构,可以降低基于沟槽ct技术的ldmos器件的导通电阻,提高热载流子退化性能。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述半导体衬底中形成有漂移区和阱区,其中,所述漂移区位于所述栅极层与阻挡层连接的一侧的半导体衬底中并延伸至所述栅极层下方,所述阱区位于所述栅极层另一侧的半导体衬底中并延伸至所述栅极层下方与所述漂移区邻接。

3.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述氧化层和导电层的方法包括:

4.如权利要求1所述的半导体结构的形成方法,其特征在于,所述层间介质层的材料与所述阻挡层的材料不同。

5.如权利要求4所述的半导体结构的形成方法,其特征在于,所述层间介质层的材料为氧化硅,所述阻挡层的材料为氮化硅。

6.如权利要求4所述的半导体结构的形成方法,其特征在于,形成所述接触结构的方法包括:

7.如权利要求1所述的半导体结构的形成方法,其特征在于,所述导电层的材料为多晶硅。

8.一种半导体结构,其特征在于,包括:

9.如权利要求8所述的半导体结构,其特征在于,所述半导体衬底中形成有漂移区和阱区,其中,所述漂移区位于所述栅极层与阻挡层连接的一侧的半导体衬底中并延伸至所述栅极层下方,所述阱区位于所述栅极层另一侧的半导体衬底中并延伸至所述栅极层下方与所述漂移区邻接。

10.如权利要求8所述的半导体结构,其特征在于,所述层间介质层的材料与所述阻挡层的材料不同。

11.如权利要求10所述的半导体结构,其特征在于,所述层间介质层的材料为氧化硅,所述阻挡层的材料为氮化硅。

12.如权利要求8所述的半导体结构,其特征在于,所述导电层的材料为多晶硅。

技术总结

本申请提供半导体结构及其形成方法,所述半导体结构包括:半导体衬底,所述半导体衬底表面形成有栅极层;氧化层,位于所述栅极层侧壁以及栅极层两侧的半导体衬底部分表面;导电层,位于所述氧化层表面,所述氧化层和导电层共同构成所述栅极层的侧墙;阻挡层,位于所述栅极层部分表面、所述栅极层一侧的侧墙表面以及所述侧墙一侧的半导体衬底表面;层间介质层,位于所述半导体衬底上完全覆盖所述半导体衬底;接触结构,贯穿所述层间介质层以及所述导电层顶部的部分阻挡层且连接所述导电层和阻挡层。本申请提供一种半导体结构及其形成方法,可以降低基于沟槽CT技术的LDMOS器件的导通电阻,提高热载流子退化性能。

技术研发人员:李智,侯艳红,陈亮,杨林宏

受保护的技术使用者:中芯国际集成电路制造(天津)有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!