半导体结构及其形成方法与流程

本申请涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、在芯片制造过程中,静电损伤的防护是非常重要的。在实际的芯片中,会设置多种保护结构,例如金属保护环等,但是用来测试评价芯片性能的测试键(testkey)通常未进行良好的保护,而使其受到静电损伤,从而导致测试结果发生变化,无法准确检测芯片性能。

2、合理的测试键设计可以有效避免静电损伤的发生,起到准确监测器件性能的作用。

技术实现思路

1、本申请要解决的技术问题是提供一种半导体结构及其形成方法,可以防止器件的静电损伤。

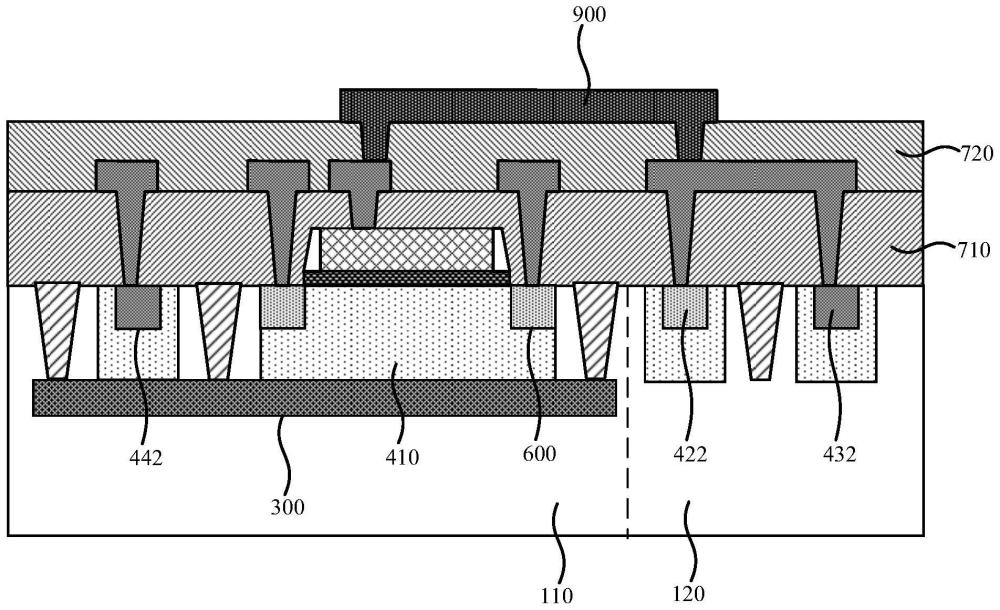

2、为解决上述技术问题,本申请提供了一种半导体结构,包括:衬底,所述衬底包括器件区和保护区;第一掺杂区,位于所述衬底的器件区中;器件结构,位于所述第一掺杂区上,包括栅极结构;保护二极管,位于所述衬底的保护区中,并与所述器件结构隔离,用于疏导第一电荷;第二掺杂区,位于所述衬底的保护区中,并与所述保护二极管隔离;第三掺杂区,位于所述第二掺杂区中,用于疏导与所述第一电荷电性相反的第二电荷;栅极衬垫,电连接所述栅极结构、所述保护二极管及所述第三掺杂区。

3、在本申请的一些实施例中,所述第二掺杂区、所述第三掺杂区及所述衬底的表面平齐。

4、在本申请的一些实施例中,所述保护二极管包括:第四掺杂区,顶面与所述衬底的表面平齐,并与所述第二掺杂区的掺杂类型相同;第五掺杂区,与所述第四掺杂区的掺杂类型不同,并位于所述第四掺杂区中且表面和所述第四掺杂区的顶面平齐。

5、在本申请的一些实施例中,所述第一掺杂区和所述第五掺杂区的掺杂类型相同,并与所述第二掺杂区、第三掺杂区及第四掺杂区的掺杂类型不同。

6、在本申请的一些实施例中,所述第二掺杂区和所述第四掺杂区通过第一隔离结构隔离。

7、在本申请的一些实施例中,所述栅极结构包括栅氧化层和位于所述栅氧化层表面的栅极层;所述器件结构还包括:阱区,与所述第一掺杂区的掺杂类型不同,并位于所述第一掺杂区的表面,且所述阱区的表面和所述衬底的顶面平齐,其中所述栅氧化层位于所述阱区的表面;源漏,位于所述栅极结构两侧的所述阱区中。

8、在本申请的一些实施例中,所述阱区和所述保护二极管通过第二隔离结构隔离。

9、在本申请的一些实施例中,所述半导体结构还包括:第六掺杂区,位于所述第一掺杂区的表面,且所述第六掺杂区的表面和所述衬底的顶面平齐;第七掺杂区,与所述第六掺杂区的掺杂类型相同,并位于所述第六掺杂区中,且所述第七掺杂区的顶面和所述第六掺杂区的表面平齐。

10、在本申请的一些实施例中,所述第六掺杂区的一侧与所述器件结构通过第三隔离结构隔离,另一侧还包括第四隔离结构。

11、在本申请的一些实施例中,所述半导体结构还包括所述栅极层、所述源漏、所述保护二极管、所述第三掺杂区及所述第七掺杂区的金属互连线。

12、在本申请的一些实施例中,所述栅极衬垫与所述栅极层、所述保护二极管及所述第三掺杂区的金属互连线电连接。

13、本申请还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括器件区和保护区;在所述衬底的器件区中形成第一掺杂区;在所述衬底的器件区形成包括栅极结构的器件结构,在所述衬底的保护区形成与所述器件结构隔离的保护二极管、与所述保护二极管隔离的第二掺杂区以及第三掺杂区,其中所述保护二极管用于疏导第一电荷,所述第三掺杂区用于疏导与所述第一电荷电性相反的第二电荷;形成电连接所述栅极结构、所述保护二极管及所述第三掺杂区的栅极衬垫。

14、在本申请的一些实施例中,所述器件结构、所述保护二极管、所述第二掺杂区和所述第三掺杂区的形成方法包括:在所述第一掺杂区的表面形成所述器件结构的阱区,并在所述保护区形成第二掺杂区以及所述保护二极管的第四掺杂区;在所述阱区的表面形成所述器件结构的栅极结构;在所述栅极结构两侧的阱区中形成源漏,并在所述第四掺杂区中形成所述保护二极管的第五掺杂区;在所述第二掺杂区中形成所述第三掺杂区。

15、在本申请的一些实施例中,在形成所述阱区、所述第二掺杂区及所述第四掺杂区的同时,还在所述第一掺杂区的表面形成第六掺杂区;在形成所述第三掺杂区的同时,还在所述第六掺杂区中形成第七掺杂区。

16、在本申请的一些实施例中,形成所述栅极衬垫的方法包括:形成所述栅极层、所述源漏、所述保护二极管、所述第三掺杂区及所述第七掺杂区的金属互连线;形成电连接所述栅极结构、所述保护二极管及所述第三掺杂区的金属互连线的所述栅极衬垫。

17、在本申请的一些实施例中,在形成所述第一掺杂区之前,还包括:在所述衬底的器件区和保护区中形成隔离结构。

18、在本申请的一些实施例中,所述隔离结构包括:用于隔离所述第二掺杂区和所述第四掺杂区的第一隔离结构;用于隔离所述阱区和所述保护二极管的第二隔离结构;位于所述第六掺杂区一侧且用于和所述器件结构隔离的第三隔离结构,以及位于所述第六掺杂区另一侧的第四隔离结构。

19、与现有技术相比,本申请技术方案的半导体结构及其形成方法具有如下有益效果:

20、在衬底的保护区形成保护二极管以及第二掺杂区、第三掺杂区,可以将芯片制作工艺中形成的电性相反的电荷同时疏导至衬底中,解决了目前的静电防护方法只能防护正电荷或者负电荷的问题,能够较好的保护栅氧化层以避免器件特性受到影响。

21、在器件区设置第一掺杂区,可以和保护区形成电学隔离,确保在器件区加电时不受保护区的影响,解决了目前的静电防护方法会影响器件区正常加电的问题。进一步地,在衬底的第六掺杂区一侧与所述器件结构通过第三隔离结构隔离,另一侧还包括第四隔离结构,形成物理隔离避免闩锁效应的发生。

22、保护二极管以及第二掺杂区、第三掺杂区的形成方法与现有工艺相兼容,不会引入额外的工艺步骤。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第二掺杂区、所述第三掺杂区及所述衬底的表面平齐。

3.根据权利要求1所述的半导体结构,其特征在于,所述保护二极管包括:

4.根据权利要求3所述的半导体结构,其特征在于,所述第一掺杂区和所述第五掺杂区的掺杂类型相同,并与所述第二掺杂区、第三掺杂区及第四掺杂区的掺杂类型不同。

5.根据权利要求3所述的半导体结构,其特征在于,所述第二掺杂区和所述第四掺杂区通过第一隔离结构隔离。

6.根据权利要求1所述的半导体结构,其特征在于,所述栅极结构包括栅氧化层和位于所述栅氧化层表面的栅极层;所述器件结构还包括:

7.根据权利要求6所述的半导体结构,其特征在于,所述阱区和所述保护二极管通过第二隔离结构隔离。

8.根据权利要求6所述的半导体结构,其特征在于,所述半导体结构还包括:

9.根据权利要求8所述的半导体结构,其特征在于,所述第六掺杂区的一侧与所述器件结构通过第三隔离结构隔离,另一侧还包括第四隔离结构。

10.根据权利要求8所述的半导体结构,其特征在于,所述半导体结构还包括所述栅极层、所述源漏、所述保护二极管、所述第三掺杂区及所述第七掺杂区的金属互连线。

11.根据权利要求10所述的半导体结构,其特征在于,所述栅极衬垫与所述栅极层、所述保护二极管及所述第三掺杂区的金属互连线电连接。

12.一种半导体结构的形成方法,其特征在于,包括:

13.根据权利要求12所述的半导体结构的形成方法,其特征在于,所述器件结构、所述保护二极管、所述第二掺杂区和所述第三掺杂区的形成方法包括:

14.根据权利要求13所述的半导体结构的形成方法,其特征在于,在形成所述阱区、所述第二掺杂区及所述第四掺杂区的同时,还在所述第一掺杂区的表面形成第六掺杂区;在形成所述第三掺杂区的同时,还在所述第六掺杂区中形成第七掺杂区。

15.根据权利要求14所述的半导体结构的形成方法,其特征在于,形成所述栅极衬垫的方法包括:

16.根据权利要求14所述的半导体结构的形成方法,其特征在于,在形成所述第一掺杂区之前,还包括:在所述衬底的器件区和保护区中形成隔离结构。

17.根据权利要求16所述的半导体结构的形成方法,其特征在于,所述隔离结构包括:

技术总结

本申请提供一种半导体结构及其形成方法,所述半导体结构,包括:衬底,所述衬底包括器件区和保护区;第一掺杂区,位于所述衬底的器件区中;器件结构,位于所述第一掺杂区上,包括栅极结构;保护二极管,位于所述衬底的保护区中,并与所述器件结构隔离,用于疏导第一电荷;第二掺杂区,位于所述衬底的保护区中,并与所述保护二极管隔离;第三掺杂区,位于所述第二掺杂区中,用于疏导与所述第一电荷电性相反的第二电荷;栅极衬垫,电连接所述栅极结构、所述保护二极管及所述第三掺杂区。所述半导体结构及其形成方法可以防止器件的静电损伤。

技术研发人员:强朝辉,史蕊蕊

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!