一种半导体结构的制作方法与流程

本发明涉及半导体,具体而言涉及一种半导体结构的制作方法。

背景技术:

1、随着5g时代的到来,市场上对射频芯片的需求越来越高,与传统的砷化镓(gaas)和蓝宝石(sos)技术相比,射频绝缘体上硅(rf soi)器件具有更好的射频性能,更高的集成度和更低的材料成本。rf soi是指利用绝缘体上硅(soi)技术的射频产品,soi内置隔离衬底高电阻率的特性可以从本质上减小结电容和漏电流,提高开关速度、降低功耗,尤其适用于保障射频信号的完整性。

2、然而,soi内置隔离衬底高电阻率的特性还会导致工艺过程中产生的电荷不易释放,使得soi衬底较传统体硅衬底的电弧敏感性更高,当电荷聚积达到一定值时会发生电弧放电。尤其在刻蚀工艺期间,晶圆边缘发生电弧放电的概率更高。

3、因此,有必要提出一种新的半导体结构的制作方法,以解决上述问题。

技术实现思路

1、在

技术实现要素:

部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

2、本发明提供了一种半导体结构的制作方法,包括:

3、提供半导体晶圆;

4、形成覆盖所述半导体晶圆的介电层;

5、在所述介电层的边缘形成第一光阻层;

6、形成覆盖所述半导体晶圆的第二光阻层,并图案化所述第二光阻层;

7、以所述图案化的第二光阻层为掩膜蚀刻所述介电层。

8、进一步,所述第一光阻层包括负光阻,所述第二光阻层包括正光阻。

9、进一步,采用硅片边缘曝光工艺形成所述第一光阻层。

10、进一步,所述第一光阻层的宽度范围为3mm~5mm。

11、进一步,所述介电层包括大尺寸顶层通孔层或大尺寸顶层沟槽层。

12、进一步,蚀刻所述介电层以形成贯穿所述介电层的通孔。

13、进一步,在蚀刻所述介电层之后还包括步骤:去除所述第二光阻层和所述第一光阻层。

14、进一步,在去除所述第二光阻层和所述第一光阻层之后还包括步骤:在所述通孔中填充金属材料。

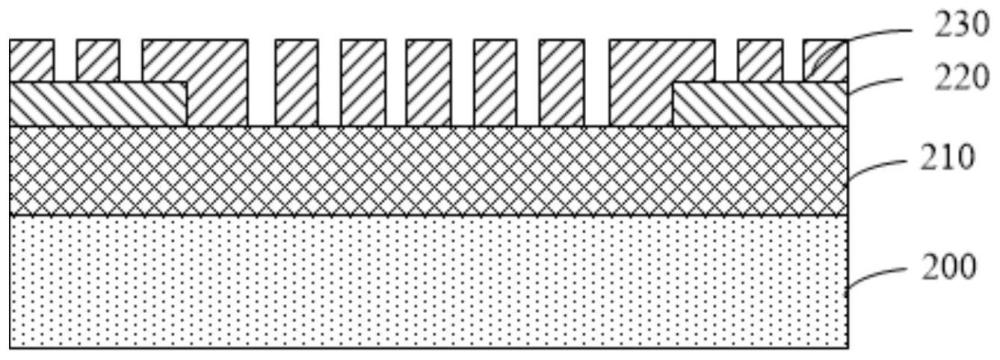

15、进一步,所述半导体晶圆包括半导体衬底,以及位于所述半导体衬底与所述介电层之间的半导体层堆叠。

16、进一步,所述半导体结构包括射频绝缘体上硅器件结构。

17、根据本发明提供的半导体结构的制作方法,在形成覆盖晶圆的第二光阻层之前首先在晶圆边缘形成第一光阻层,防止对晶圆边缘的刻蚀,从而避免了刻蚀工艺期间晶圆边缘发生电弧放电,提高了晶圆的良率。

技术特征:

1.一种半导体结构的制作方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的制作方法,其特征在于,所述第一光阻层包括负光阻,所述第二光阻层包括正光阻。

3.如权利要求1所述的半导体结构的制作方法,其特征在于,采用硅片边缘曝光工艺形成所述第一光阻层。

4.如权利要求1所述的半导体结构的制作方法,其特征在于,所述第一光阻层的宽度范围为3mm~5mm。

5.如权利要求1所述的半导体结构的制作方法,其特征在于,所述介电层包括大尺寸顶层通孔层或大尺寸顶层沟槽层。

6.如权利要求5所述的半导体结构的制作方法,其特征在于,蚀刻所述介电层以形成贯穿所述介电层的通孔。

7.如权利要求6所述的半导体结构的制作方法,其特征在于,在蚀刻所述介电层之后还包括步骤:

8.如权利要求7所述的半导体结构的制作方法,其特征在于,在去除所述第二光阻层和所述第一光阻层之后还包括步骤:

9.如权利要求1所述的半导体结构的制作方法,其特征在于,所述半导体晶圆包括半导体衬底,以及位于所述半导体衬底与所述介电层之间的半导体层堆叠。

10.如权利要求1所述的半导体结构的制作方法,其特征在于,所述半导体结构包括射频绝缘体上硅器件结构。

技术总结

本发明公开了一种半导体结构的制作方法,包括:提供半导体晶圆;形成覆盖所述半导体晶圆的介电层;在所述介电层的边缘形成第一光阻层;形成覆盖所述半导体晶圆的第二光阻层,并图案化所述第二光阻层;以所述图案化的第二光阻层为掩膜蚀刻所述介电层。根据本发明提供的半导体结构的制作方法,在形成覆盖晶圆的第二光阻层之前首先在晶圆边缘形成第一光阻层,防止对晶圆边缘的刻蚀,从而避免了刻蚀工艺期间晶圆边缘发生电弧放电,提高了晶圆的良率。

技术研发人员:周洋

受保护的技术使用者:中芯集成电路(宁波)有限公司

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!