半导体结构及其形成方法、存储器与流程

本公开涉及半导体,具体而言,涉及一种半导体结构及其形成方法、存储器。

背景技术:

1、在半导体制程过程中,通常需要对薄膜进行图案化,进而形成半导体器件需要的图形。在此过程中,为了完成图形转移需要在晶圆表面形成带有多个掩膜图案的掩膜层,然而受制程工艺的限制,各掩膜图案之间的结构的尺寸偏差较大,导致产品良率降低。

2、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、有鉴于此,本公开提供一种半导体结构及其形成方法、存储器,可降低尺寸偏差,降低后续工艺难度,提高产品良率。

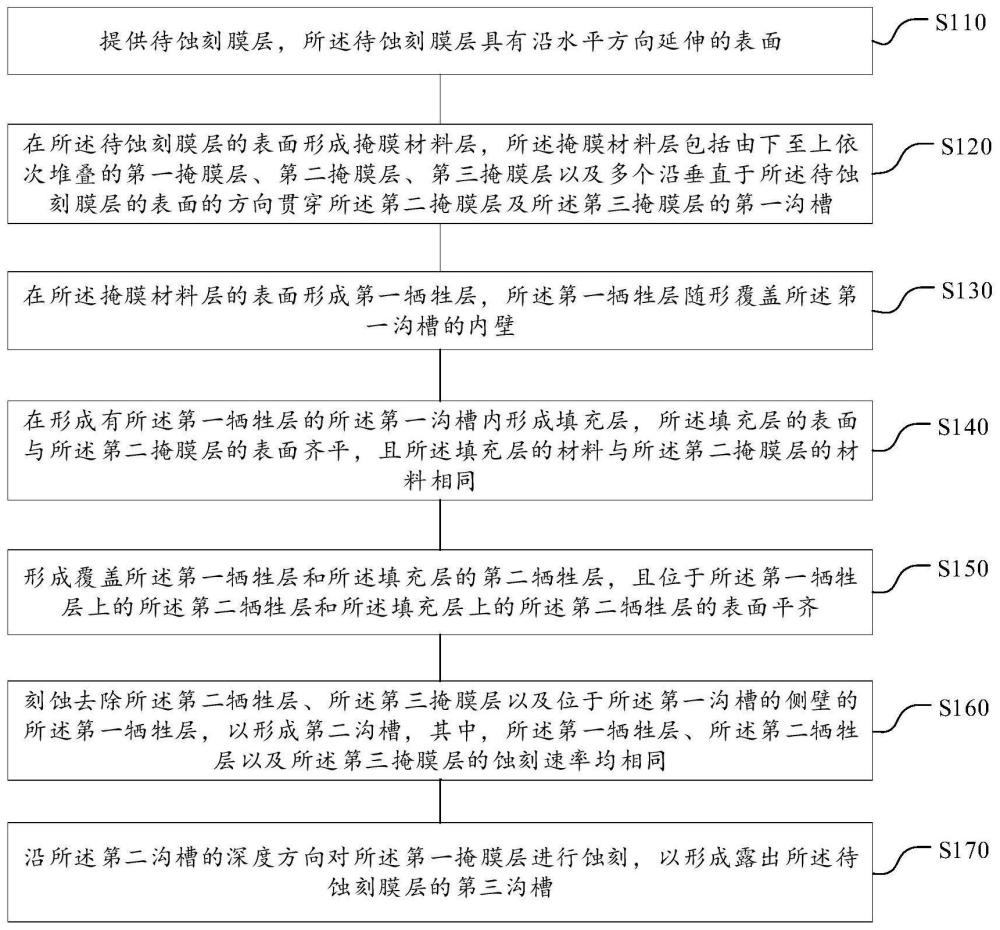

2、根据本公开的一个方面,提供一种半导体结构的形成方法,包括:

3、提供待蚀刻膜层,所述待蚀刻膜层具有沿水平方向延伸的表面;

4、在所述待蚀刻膜层的表面形成掩膜材料层,所述掩膜材料层包括由下至上依次堆叠的第一掩膜层、第二掩膜层、第三掩膜层以及多个沿垂直于所述待蚀刻膜层的表面的方向贯穿所述第二掩膜层及所述第三掩膜层的第一沟槽;

5、在所述掩膜材料层的表面形成第一牺牲层,所述第一牺牲层随形覆盖所述第一沟槽的内壁;

6、在形成有所述第一牺牲层的所述第一沟槽内形成填充层,所述填充层的表面与所述第二掩膜层的表面齐平,且所述填充层的材料与所述第二掩膜层的材料相同;

7、形成覆盖所述第一牺牲层和所述填充层的第二牺牲层,且位于所述第一牺牲层上的所述第二牺牲层和所述填充层上的所述第二牺牲层的表面平齐;

8、刻蚀去除所述第二牺牲层、所述第三掩膜层以及位于所述第一沟槽的侧壁的所述第一牺牲层,以形成第二沟槽,其中,所述第一牺牲层、所述第二牺牲层以及所述第三掩膜层的蚀刻速率均相同;

9、沿所述第二沟槽的深度方向对所述第一掩膜层进行蚀刻,以形成露出所述待蚀刻膜层的第三沟槽。

10、在本公开的一种示例性实施例中,所述第一牺牲层、所述第二牺牲层以及所述第三掩膜层的材料相同。

11、在本公开的一种示例性实施例中,在所述第一沟槽的宽度方向上,所述填充层的宽度与相邻的所述第一沟槽之间的所述第二掩膜层的宽度相等。

12、在本公开的一种示例性实施例中,所述第二掩膜层的厚度大于或等于100nm,且小于或等于300nm;所述第三掩膜层的厚度大于20nm。

13、在本公开的一种示例性实施例中,采用干法蚀刻工艺去除所述第二牺牲层、所述第三掩膜层以及位于所述第一沟槽的侧壁的所述第一牺牲层。

14、在本公开的一种示例性实施例中,所述第一牺牲层、所述第二牺牲层以及所述第三掩膜层的材料均为氧化硅,所述干法蚀刻的蚀刻气体为四氟化碳、乙烷或氯气中至少一种。

15、在本公开的一种示例性实施例中,所述填充层的材料与所述第二掩膜层的材料相同。

16、在本公开的一种示例性实施例中,所述填充层与所述第二掩膜层的材料均为旋涂硬掩膜。

17、在本公开的一种示例性实施例中,形成所述掩膜材料层包括:

18、在所述待蚀刻膜层的表面形成沿垂直于所述待蚀刻膜层的方向由下至上依次堆叠的第一掩膜层、第二掩膜层、第三掩膜层以及光阻层;

19、对所述光阻层进行曝光和显影,以形成光阻图案;

20、以所述第一掩膜层为蚀刻停止层,并以所述光阻图案为掩膜对所述第二掩膜层及所述第三掩膜层进行蚀刻,以形成多个分别露出所述第一掩膜层的第一沟槽。

21、在本公开的一种示例性实施例中,形成所述填充层包括:

22、在所述第一牺牲层的表面形成填充层,所述填充层至少填满所述第一沟槽;

23、对所述填充层进行蚀刻,以去除位于所述第一沟槽外的所述填充层,并使位于所述第一沟槽内的所述填充层的顶部与所述第二掩膜层远离所述待蚀刻膜层的表面齐平。

24、在本公开的一种示例性实施例中,所述去除所述第二牺牲层、所述第三掩膜层以及位于所述第一沟槽的侧壁的所述第一牺牲层,以形成第二沟槽,包括:

25、去除所述第二牺牲层、所述第三掩膜层以及位于所述第三掩膜层的顶部及侧壁上的所述第一牺牲层;

26、去除位于所述第一沟槽的侧壁上的所述第一牺牲层,以将所述第一掩膜层的表面露出,所述填充层与所述第二掩膜层之间的空间构成第二沟槽。

27、在本公开的一种示例性实施例中,所述第一掩膜层包括蚀刻停止层及图形转移层,所述蚀刻停止层位于所述图形转移层表面。

28、在本公开的一种示例性实施例中,所述形成方法还包括:

29、以具有所述第三沟槽的所述第一掩膜层为掩膜对所述待蚀刻膜层进行蚀刻,以在所述待蚀刻膜层中形成目标图案。

30、根据本公开的一个方面,提供一种半导体结构,所述半导体结构由上述任意一项所述的半导体结构的形成方法形成。

31、根据本公开的一个方面,提供一种存储器,包括由上述任意一项所述的半导体结构的形成方法形成的半导体结构。

32、本公开的半导体结构及其形成方法、存储器,由于填充层的表面与第二掩膜层的表面齐平,且在蚀刻形成第二沟槽的过程中,由于第一牺牲层、第二牺牲层以及第三掩膜层的蚀刻速率均相同,使得第一牺牲层、第二牺牲层以及第三掩膜层可同时蚀刻至第二掩膜层及填充层的表面,即,当第二牺牲层和第三掩膜层蚀刻完后,剩余的第一牺牲层的顶部可与第二掩膜层及填充的表面齐平;在后续蚀刻过程中,可对位于填充层及第二掩膜层之间的第一牺牲层进行选择性蚀刻,进而形成第二沟槽,在此过程中,由于填充层的表面与第二掩膜层的表面齐平,且填充层的材料与第二掩膜层的材料相同,在通过同一种蚀刻气体或蚀刻溶液对第一牺牲层进行蚀刻的过程中,即便该气体或溶液会对填充层或第二掩膜层有所消耗,其两者的消耗速率也是相等的,可使第二掩膜层与填充层始终保持同样的占比,有助于减小由于蚀刻不均而引起位于第二沟槽两侧的第二掩膜层与填充层之间的尺寸偏差,有助于降低最终形成的第三沟槽的两侧的第一掩膜层的尺寸偏差,进而降低后续工艺难度,提高产品良率。

33、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.根据权利要求1所述的形成方法,其特征在于,所述第一牺牲层、所述第二牺牲层以及所述第三掩膜层的材料相同。

3.根据权利要求1所述的形成方法,其特征在于,在所述第一沟槽的宽度方向上,所述填充层的宽度与相邻的所述第一沟槽之间的所述第二掩膜层的宽度相等。

4.根据权利要求1所述的形成方法,其特征在于,所述第二掩膜层的厚度大于或等于100nm,且小于或等于300nm;所述第三掩膜层的厚度大于20nm。

5.根据权利要求2所述的形成方法,其特征在于,采用干法蚀刻工艺去除所述第二牺牲层、所述第三掩膜层以及位于所述第一沟槽的侧壁的所述第一牺牲层。

6.根据权利要求5所述的形成方法,其特征在于,所述第一牺牲层、所述第二牺牲层以及所述第三掩膜层的材料均为氧化硅,所述干法蚀刻的蚀刻气体为四氟化碳、乙烷或氯气中至少一种。

7.根据权利要求1所述的形成方法,其特征在于,所述填充层的材料与所述第二掩膜层的材料相同。

8.根据权利要求7所述的形成方法,其特征在于,所述填充层与所述第二掩膜层的材料均为旋涂硬掩膜。

9.根据权利要求1-8任一项所述的形成方法,其特征在于,形成所述掩膜材料层包括:

10.根据权利要求1-8任一项所述的形成方法,其特征在于,形成所述填充层包括:

11.根据权利要求1-8任一项所述的形成方法,其特征在于,所述去除所述第二牺牲层、所述第三掩膜层以及位于所述第一沟槽的侧壁的所述第一牺牲层,以形成第二沟槽,包括:

12.根据权利要求11所述的形成方法,其特征在于,所述第一掩膜层包括蚀刻停止层及图形转移层,所述蚀刻停止层位于所述图形转移层表面。

13.根据权利要求1-8任一项所述的形成方法,其特征在于,所述形成方法还包括:

14.一种半导体结构,其特征在于,所述半导体结构由权利要求1-13任一项所述的半导体结构的形成方法形成。

15.一种存储器,其特征在于,包括由权利要求13所述的半导体结构的形成方法形成的半导体结构。

技术总结

本公开是关于半导体技术领域,涉及一种半导体结构及其形成方法、存储器,本公开的形成方法包括:在待蚀刻膜层的表面形成掩膜材料层,掩膜材料层包括第一掩膜层、第二掩膜层、第三掩膜层以及贯穿第二掩膜层及第三掩膜层的第一沟槽;形成第一牺牲层,第一牺牲层随形覆盖第一沟槽的内壁;在第一沟槽内形成填充层,填充层的表面与第二掩膜层的表面齐平,填充层的材料与第二掩膜层的材料相同;形成第二牺牲层,位于第一牺牲层上和填充层上的第二牺牲层的表面平齐;形成第二沟槽;沿第二沟槽的深度方向对第一掩膜层进行蚀刻,以形成露出待蚀刻膜层的第三沟槽。本公开的形成方法可降低尺寸偏差,降低后续工艺难度,提高产品良率。

技术研发人员:宛伟,刘梅花

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!