具有图案化的贯穿电介质过孔和再分布层的封装架构的制作方法

本公开涉及针对在半导体集成电路(ic)封装中具有图案化的贯穿电介质过孔(tdv)和再 分布层(rdl)的封装架构的技术、方法和设备。

背景技术:

1、通常制作在半导体材料(例如硅)的晶片上的电子电路被称为ic。具有这样的ic的晶片典型 地被切割成众多的单个管芯。管芯可以被封装到含有一个或多个管芯以及其它电子部件(例如电阻 器、电容器和电感器)的ic封装中。ic封装可以被集成到电子系统(例如消费者电子系统)或服 务器(例如大型机)上。

技术实现思路

技术特征:

1.一种微电子组件,包括:

2.根据权利要求1所述的微电子组件,其中,所述导电迹线耦合到所述电介质材料中的电感器、变压器、电容器和电阻器中的一个或多个。

3.根据权利要求1所述的微电子组件,其中,所述导电迹线的一部分被配置用于电源分配。

4.根据权利要求3所述的微电子组件,其中,所述部分包括电源平面。

5.根据权利要求1所述的微电子组件,其中,所述导电迹线的一部分被配置为对电信号进行布线。

6.根据权利要求5所述的微电子组件,其中,所述电信号包括高频信号和射频(rf)信号中的至少一个。

7.根据权利要求1所述的微电子组件,其中,所述电介质材料包括氧、碳和氮中的至少一种与硅的化合物。

8.根据权利要求1-7中任何一项所述的微电子组件,还包括在所述电介质材料中的贯穿电介质材料过孔(tdv),以将所述导电迹线与所述第一多个ic管芯、所述第二多个ic管芯和所述第三多个ic管芯中的至少一个电耦合。

9.一种ic封装,包括:

10.根据权利要求9所述的ic封装,其中,所述电介质材料包括氧、碳和氮中的至少一种与硅的化合物。

11.根据权利要求9所述的ic封装,其中,所述tdv被配置为将所述导电迹线与所述第二ic管芯电耦合。

12.根据权利要求9所述的ic封装,其中,所述tdv被配置为将所述导电迹线与所述封装基板电耦合。

13.根据权利要求9所述的ic封装,其中,所述互连包括第一互连,并且所述ic封装还包括位于第三层中的第三ic管芯,所述第三层由第二互连耦合到所述第二层,所述第二互连在所述第二互连中的相邻的第二互连之间具有小于10微米的间距。

14.根据权利要求13所述的ic封装,其中,所述tdv被配置为将所述第三ic管芯与所述导电迹线电耦合。

15.根据权利要求13所述的ic封装,其中,所述tdv被配置为将所述第三层与所述第一层电耦合。

16.根据权利要求13所述的ic封装,其中,所述tdv被配置为将所述第三层与所述封装基板电耦合。

17.根据权利要求9-16中任何一项所述的ic封装,其中:

18.一种制作微电子组件的方法,所述方法包括:

19.根据权利要求18所述的方法,其中,形成导电迹线和tdv包括:

20.根据权利要求19所述的方法,其中:

21.根据权利要求18所述的方法,其中,形成所述导电迹线和所述tdv包括:

22.根据权利要求21所述的方法,其中,在所述ic管芯周围形成导电柱和迹线包括:

23.根据权利要求22所述的方法,还包括在所述导电柱和迹线上电镀阻挡金属,其中,所述阻挡金属防止所述导电柱和迹线渗入所述电介质材料中。

24.根据权利要求21所述的方法,其中,在所述ic管芯周围形成导电柱和迹线包括:

25.根据权利要求21-24中任何一项所述的方法,其中,所述导电柱中的至少一些导电柱部分地延伸穿过所述电介质材料的厚度。

技术总结

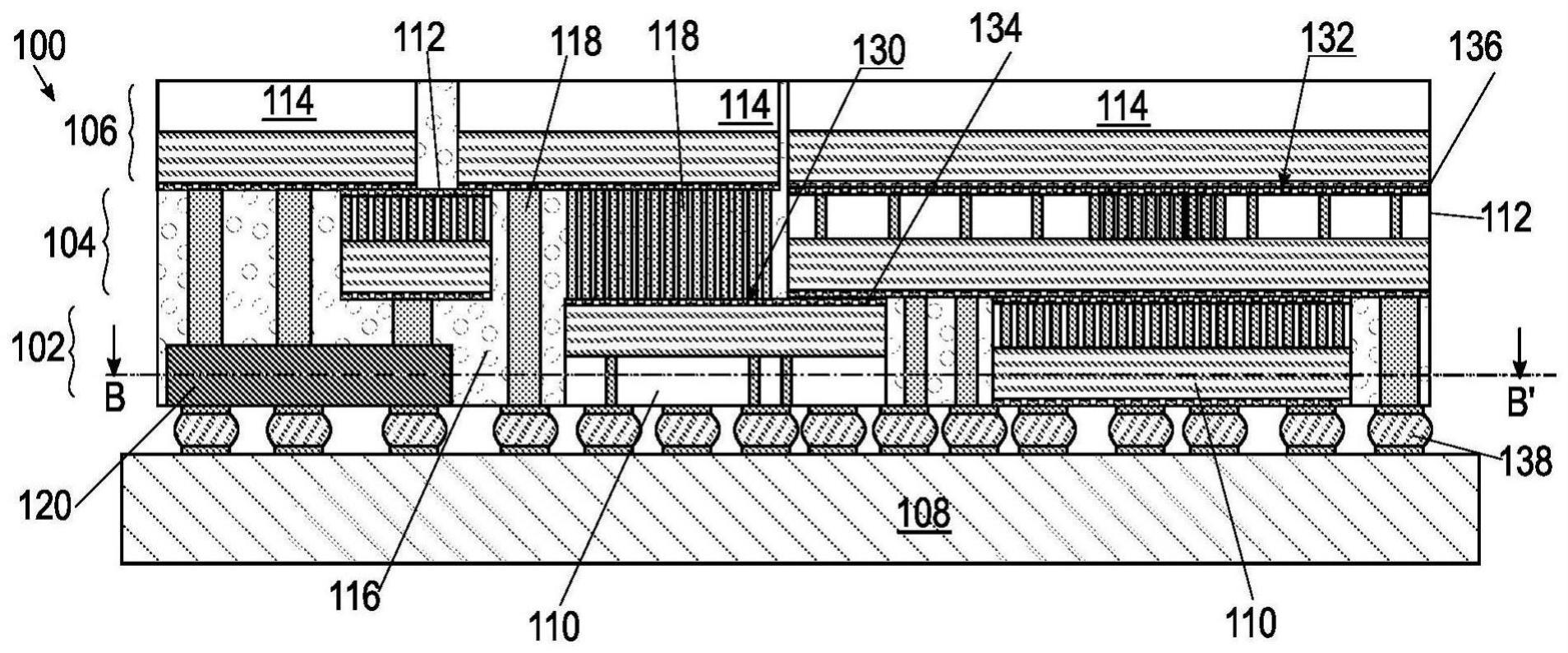

本文提供了一种具有图案化的贯穿电介质过孔和再分布层的封装架构。提供了一种微电子组件,该微电子组件包括:位于第一层中的第一多个集成电路(IC)管芯;位于第二层中的第二多个IC管芯;以及位于第三层中的第三多个IC管芯,其中:第二层位于第一层和第三层之间,位于两个相邻层之间的界面包括在互连中的相邻互连之间具有小于10微米的间距的互连,并且第一层、第二层和第三层中的每个包括电介质材料,并且还包括在电介质材料中的导电迹线。

技术研发人员:A·A·埃尔谢尔比尼,C·M·佩尔托,K·俊,B·M·罗林斯,S·M·利夫,B·A·杰克逊,R·J·穆诺茨,J·M·斯旺

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!